Article

# Study of CMOS-SOI Integrated Temperature Sensing Circuits for On-Chip Temperature Monitoring

## Maria Malits \*, Igor Brouk and Yael Nemirovsky

Department of Electrical Engineering, Technion—Israel Institute of Technology, Haifa 3200003, Israel; bigor@tx.technion.ac.il (I.B.); nemirov@ee.technion.ac.il (Y.N.)

\* Correspondence: maria.malits@gmail.com; Tel.: +972-4-829-4683

Received: 11 April 2018; Accepted: 17 May 2018; Published: 19 May 2018

Abstract: This paper investigates the concepts, performance and limitations of temperature sensing circuits realized in complementary metal-oxide-semiconductor (CMOS) silicon on insulator (SOI) technology. It is shown that the MOSFET threshold voltage ( $V_t$ ) can be used to accurately measure the chip local temperature by using a  $V_t$  extractor circuit. Furthermore, the circuit's performance is compared to standard circuits used to generate an accurate output current or voltage proportional to the absolute temperature, i.e., proportional-to-absolute temperature (PTAT), in terms of linearity, sensitivity, power consumption, speed, accuracy and calibration needs. It is shown that the  $V_t$  extractor circuit is a better solution to determine the temperature of low power, analog and mixed-signal designs due to its accuracy, low power consumption and no need for calibration. The circuit has been designed using 1  $\mu$ m partially depleted (PD) CMOS-SOI technology, and demonstrates a measurement inaccuracy of  $\pm 1.5$  K across 300 K–500 K temperature range while consuming only 30  $\mu$ W during operation.

**Keywords:** CMOS-SOI; proportional to absolute temperature (PTAT); temperature sensor;  $V_t$  extractor circuit

## 1. Introduction

Smart integrated temperature sensors and circuits are the main building blocks in all analog and mixed-signal applications, as well as in high-performance systems-on-chip (SoCs). Since the design complexity and density of VLSI circuits are increasing day by day continuous thermal monitoring is necessary to reduce thermal damage, increase reliability and avoid thermal runaway scenarios that can cause irreversible damage, i.e., overheating. The temperature across the chip should be monitored continuously, and the system operation should be adjusted accordingly. For example, in multicore SoCs, temperature information is being leveraged to maximize performance. The workload is shuffled between different cores before the temperature rises to a dangerous level. Alternatively, the clock rate is dynamically adjusted to boost system performance within a certain thermal budget [1–3].

To implement a comprehensive thermal monitoring system multiple temperature sensors should be used. The desired number of sensors, their exact location, and accuracy depend greatly on system-level requirements, integrated circuits (IC) packaging, and cooling system (if any). Sensor accuracy and operation range are two key system-level considerations. Typically, a less accurate sensor consumes less silicon area and power compared to a highly accurate sensor. A narrower temperature detection dynamic range relaxes the linearity requirements, which further saves area and power. It is challenging to generalize this problem, but it is widely known that the design tradeoffs are largely driven by exact application and system-level architecture. Therefore, the temperature sensors, which are used for temperature monitoring in VLSI chips should meet the following requirements: compatibility with the target process, a reasonable silicon area, low power consumption, require no additional

fabrication (CMOS-SOI compatibility), low cost, high accuracy and sensor linearity in the desired temperature range.

Following these requirements, various on-chip temperature-sensing circuit have been reported in the literature. In CMOS technology, the most widely used approach takes advantage of the proportional-to-absolute temperature (PTAT) property of the voltage difference between two forward-biased diodes or bipolar junction transistors (BJT) with different currents or areas [4,5]. The accuracy of BJT-based sensors depends on the diode ideality factor and accuracy of the current ratio used to bias them. Diode ideality factor is a process-dependent parameter. Careful and meticulous layout for good matching alone cannot guarantee the required matching between the individual current mirrors to achieve the desired level of accuracy. Therefore, on-chip dynamic element matching, trimming, and post fabrication calibration techniques are used in this type of sensor to improve accuracy. As a result, thermal diodes that enable accurate temperature measurement are large and power consuming, renders them suboptimal for the whole chip thermal profiling applications where placement of a large number of sensors is necessary.

For temperature sensors operating above 500 K or uncooled thermal sensors [6] CMOS-SOI process is usually adopted due to its reduced leakage currents compared to bulk CMOS, low power consumption and availability of commercial process. Most of the CMOS based temperature sensors are not compatible with CMOS-SOI technology due to the thin device layer. The two most commonly used elements for temperature sensing available in CMOS-SOI technology are: lateral diodes [7–12] and standard MOSFET transistors [13]. The SOI-based diode is an attractive choice for a temperature sensor because it is compact in size, gives linear response up to ultra-high temperature [11] and is simpler to integrate with on-chip, sensor drive and readout circuitry. While SOI diode temperature sensors have been utilize for temperature monitoring in different application [7–12] the effect of device mismatches and consequently calibration needs are rarely discussed. One of these [8], describes a work that uses a SOI lateral PIN diode for temperature sensing from 100 K to 400 K and suggests to improve the diodes accuracy by reducing the temperature range of the diode. In other study [12], a smart CMOS-SOI temperature sensor has been described that uses a self-discharging SOI diode for temperature sensing and an error of  $\pm 1.95C$  (3 $\sigma$ ) has been achieved after two-point calibration.

In this paper, we address the aforementioned challenges by demonstrating the design and successful implementation of a small, low-power, and accurate on chip temperature sensing circuit based on "Threshold Voltage Thermometry" [14], namely a threshold voltage ( $V_t$ ) extractor circuit. The performance of the  $V_t$  extractor circuit is compared to a standard circuit used for temperature sensing, i.e., PTAT circuit, in terms of sensitivity, linearity, speed, accuracy, calibration needs, area and sensor power consumption. Both circuits were designed using 1  $\mu$ m PD CMOS-SOI technology [15] and their performance has been experimentally verified by comparing simulated and measured results.

For 1  $\mu m$  CMOS-SOI process, this  $80 \times 100$  ( $\mu m^2$ ) sensor consumes ~30  $\mu W$  using a 5-V supply. Our thermal measurements using multiple chips show only  $\pm 1.5$  K inaccuracy between the 300 K and 500 K temperature range.

## 2. Proportional to Absolute Temperature (PTAT) Circuit

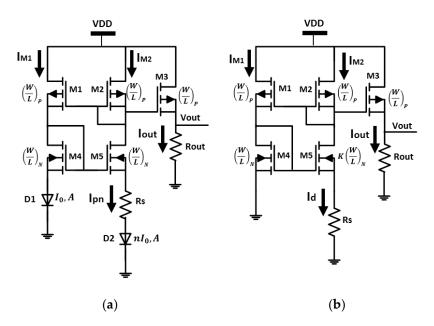

Proportional to absolute temperature circuits are widely used to generate temperature independent current/voltage sources, band-gap reference circuits and temperature sensors in many digital, analog and mix-signal systems. Typical CMOS based PTAT circuits are shown in Figure 1a,b [16]. The first circuit is based on the exponential dependence of the vertical PN diode forward voltage upon temperature and the second one is based on the dependence of resistors and channel mobility to generate an output voltage/current proportional to the chip local temperature.

Sensors 2018, 18, 1629 3 of 14

**Figure 1.** Conventional proportional to absolute temperature (PTAT) circuit implemented in CMOS technology based on (**a**) the exponential dependence of vertical PN diodes; (**b**) Polysilicon resistors.

# 2.1. Principle of Operation

The sensing principle of a PTAT temperature sensor is depicted in Figure 1a. The sensor's core consists of a pair of matched vertical PN diodes biased by two identical current sources ( $I_{pn}$ ) while diode D2 consists of n parallel connected diodes with the same device area [7]. The voltage drop on each diode is given by [14]:

$$V_{pn} = \frac{k_B T}{q} \left[ \ln \left( \frac{I_{pn}}{I_0} + 1 \right) \right] \approx \frac{k_B T}{q} \ln \left( \frac{I_{pn}}{I_0} \right) \tag{1}$$

where  $I_{pn}$  is the diode current, q is the electron charge,  $k_B$  is Boltzmann's constant,  $V_{pn}$  is the voltage across the diode, T is the absolute temperature,  $I_0$  is the temperature-dependent reverse saturation current.

By choosing the upper transistors so that the current in both branches is similar ( $I_{M1} = I_{M2} = I_{pn}$ ), and by neglecting channel length modulation and bulk effect the circuit output voltage can be calculated:

$$V_{pn,D1} = V_{pn,D2} + I_{pn} \cdot R_{s}$$

$$\frac{k_{B}T}{q} \ln \left( \frac{I_{pn}}{I_{0}} \right) = \frac{k_{B}T}{q} \ln \left( \frac{I_{pn}}{nI_{0}} \right) + I_{pn} \cdot R_{s}$$

$$I_{pn} = I_{out} = \frac{k_{B}T \ln(n)}{qR_{s}}$$

$$V_{out} = I_{out} \cdot R_{out} = \frac{k_{B}T}{q} \cdot \ln(n) \cdot \frac{R_{out}}{R_{s}}$$

(2)

where n is the number of parallel connected diodes,  $I_{out}$  is the circuit output current,  $R_{out}$  and  $R_s$  are the output and series resistors respectively. Usually, the resistors  $R_{out}$  and  $R_s$  are from the same type so their temperature coefficient will balance each other and improve the circuit performance.

Figure 1b illustrates another PTAT implementation which uses the dependence of mobility and resistors upon temperature to generate the output voltage. The upper p-type transistors (M1 and M2) have the same current ( $I_{\rm M1} = I_{\rm M2} = I_d$ ) because they have identical dimensions. Hence, we can calculate the NMOS gate voltage:

$$V_{qs4} = V_{q5} + I_d \times R_s \tag{3}$$

where  $V_{gs}$  is the transistor gate-source voltage and  $I_d$  is the transistor drain current.

Sensors **2018**, *18*, 1629 4 of 14

By neglecting body effect we can determine the circuit output voltage:

$$\sqrt{\frac{2I_{d}}{\mu_{n}C_{ox}(W/L)_{N}}} + V_{t4} = \sqrt{\frac{2I_{d}}{\mu_{n}C_{ox}K(W/L)_{N}}} + V_{t5} + I_{d} \times R_{s}$$

$$\sqrt{\frac{2I_{d}}{\mu_{n}C_{ox}(W/L)_{N}}} \left(1 - \frac{1}{\sqrt{K}}\right) = I_{d} \times R_{s}$$

$$I_{d} = I_{out} = \frac{2}{\mu_{n}C_{ox}(W/L)_{N}} \times \frac{1}{R_{s}^{2}} \left(1 - \frac{1}{\sqrt{K}}\right)^{2}$$

$$V_{out} = I_{out} \times R_{out} = \frac{2}{\mu_{n}C_{ox}(W/L)_{N}} \times \frac{R_{out}}{R_{s}^{2}} \left(1 - \frac{1}{\sqrt{K}}\right)^{2}$$

(4)

where  $\mu_n$  is the electron mobility, K is transistors M4 and M5 size ratio, W and L are the transistor width and length respectively and  $C_{ox}$  is the oxide capacitance.

As seen from Equation (4), the output voltage is inversely proportional to the channel mobility creating a proportional to absolute temperature output voltage. It is important to emphasize that since each diode-connected device feeds from a current source this design is relatively independent of  $V_{dd}$ .

## 2.2. Implementation

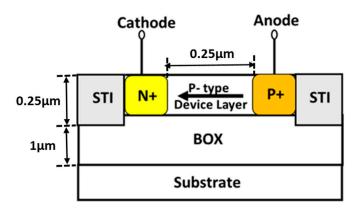

In CMOS-SOI technology it is impossible to manufacture a vertical diode due to the thin body layer; hence, in order to implement a diode based circuit (Figure 1a), a forward-biased diode is built with a lateral structure based on the device layer, forming a source/drain PIN junction. The diode based circuit was implemented using 25 N+/P-well/P+ non-gated diodes (24 are finger diodes interdigitated in parallel) with width of 16  $\mu$ m and length of 0.25  $\mu$ m, as presented in Figure 2. The PMOS and NMOS dimensions are  $(W/L)_P = 6 \mu m/2 \mu m/(W/L)_N = 6 \mu m/3 \mu m$  for the diode based design and  $(W/L)_P = 24 \mu m/2 \mu m/(W/L)_N = 6 \mu m/3 \mu m$  for the resistor based design. The size ratio between transistors M4 and M5, i.e., K, in the resistor based PTAT (Figure 1b) is 2.

Figure 2. Schematic cross-section of the lateral SOI diode used in the diode based PTAT circuit.

Both architectures are realized in a standard 1  $\mu m$  PD CMOS-SOI process [15]. The maximum operating voltage is 5 V. The buried oxide (BOX) thickness is 1  $\mu m$ , the gate oxide thickness is 25 nm, and the active silicon thickness is 250 nm. The circuits chip areas are  $178 \times 150 \ \mu m^2$  and  $85 \times 100 \ \mu m^2$  for the diode based design and the resistor based design, respectively. The resistors in both circuits are implemented using high resistivity Polysilicon.

Although the SOI lateral diode is modeled as an ideal diode, it should be noted that the saturation current exhibits perimeter dependence rather than area dependence, as in regular planar bulk diodes, due to the thin body layer. Contrary to CMOS bulk diodes, where surface effects may be neglected, the thin device layer in SOI technology requires a model where the current is primarily dependent on surface effects, i.e.,  $I_0 = J_{SW}(T) \times \text{Perimeter}$ .

As a result, the saturation current is strongly affected by the surface, determined by the device periphery. This significantly increases the mismatch between diodes and affects the diode's

Sensors **2018**, *18*, 1629 5 of 14

performance as a temperature sensor, as reported in [14] for lateral diodes fabricated in two different SOI processes.

#### 2.3. Measurements and Simulations

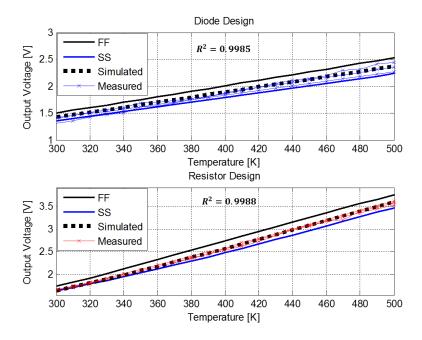

The output voltage of both designs is sampled by using a DMM4040 Digital Precision Multimeter (Tektronix, Beaverton, OR, USA) while the circuit's temperature is determined with a variable temperature micro probe system from MMR Technologies (San Jose, CA, USA), which features a temperature control accuracy of  $\pm 0.01$  K. All transistors (M1–M5) are biased and their current measured using a B1500A semiconductor parameter analyzer (Agilent, Santa Clara, California, USA). Three samples from each design were characterized in temperature ranging from 300 K to 500 K and the measured output voltage is shown in Figure 3. These results are compared to  $V_{out}$  vs. T curves obtained from electrical simulations in the SPICE simulator based on BSIM4 MOSFET models [17], also presented in Figure 3.

**Figure 3.** Measured and simulated output voltage of three chips for both PTAT designs at a temperature range of 300 K–500 K. Dots: experimental data; dashed lines: simulation results using the SPICE circuit simulator based on and BSIM4 MOSFET models; solid: circuit output voltage in different process corners (FF and SS).

The temperature sensing circuits' performance is also analyzed using process corner simulations. A four-corner model file provided by the foundry is used for the corner-based analysis. In Figure 3 only the corners with worst case variations are shown—Fast NMOS Fast PMOS (FF) and Slow NMOS Slow PMOS (SS).

In this analysis, the coefficient of determination,  $R^2$  [18] has been used to evaluate the linearity of the sensor, through the agreement between the experimental data and their best linear fit. Figure 3 shows that the resistor based design exhibits linear dependence upon temperature in the entire temperature range ( $R^2$  = 0.9988 in the worst case sample) and minimal variations between the measured samples. The diode based design is also linear as a function of temperature ( $R^2$  = 0.9985 in the worst case sample), but has larger variations between the different samples. The measured temperature sensitivity of the output voltage after a linear curve fit is 9.8 mV/K for the resistor based PTAT design and it is close to that obtained from the simulation. The sensitivity of the diode based design is

Sensors **2018**, *18*, 1629 6 of 14

4.7 mV/K for a bias current of  $3.3 \mu\text{A}$ , which is higher than that reported for SOI lateral PIN diodes, which is in the order of 1.1 mV/K for a bias current of  $2 \mu\text{A}$  [7–9].

As illustrated in Figure 3, for the diode based design there is a DC shift between the measured and simulated results for all measured samples (maximum value of DC shift is 32 mV) due to the dependence of the saturation current in the diode dimensions. This dependency of the saturation current causes a large mismatch between lateral diodes that should be identical, as reported by us in [14]. As a result, the accuracy of the diode based PTAT circuit decreases.

In addition, the corner analysis shows that the worst case maximum temperature error occurs at the FF corner and caused combined offset of 100 mV and 150 mV for the resistor and diode based PTAT designs. It is important to note that this offset includes large mismatches in polysilicon resistance value and can be improved by matched layout. The shifts and variations between the different measured samples for the diode based design results in large temperature measurement errors and require precise calibration process.

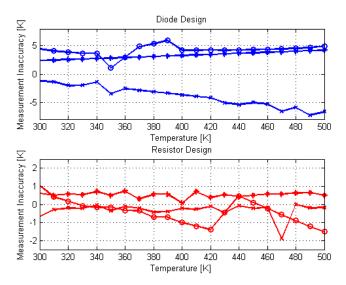

The error in the temperature measurement ( $\Delta T$ ) has been obtained by calculating the difference,  $\Delta V_{out}$ , between the measured and simulated  $V_{out}$  vs. T, which is then converted into temperature using the circuit sensitivity. Figure 4 shows the error in temperature measurement as a function of applied temperature for both designs in the measured samples presented in Figure 3. Accordingly, the sensor's inaccuracy is estimated:

$$\Delta T = \frac{\left| V_{out,measured} - V_{out,simulated} \right|}{dV_{out}/dT}$$

(5)

Figure 4. Measurement inaccuracy versus temperature for three different chips in both PTAT designs.

From the extracted error curves presented in Figure 4 one can observe a maximum error of  $\pm 6.5~K$  for the diode based PTAT circuit and an error of  $\pm 1.5~K$  when using the temperature dependence of polysilicon resistors, without any additional calibration. These results show that the resistor based PTAT circuit is a good temperature sensor for temperatures ranging from 300 K till 500 K, though it is power consuming. The circuit measured power consumption at room temperature is 0.25 mW for the resistor based design and 45  $\mu W$  for the diode based design. Errors similar to the errors calculated for the resistor based design, in order of 2 K, have been presented in [12] after two-point calibration for temperature sensing from 278 K up to 373 K using fully depleted single lateral SOI diode consuming 100  $\mu W$ .

Sensors **2018**, 18, 1629 7 of 14

### 2.4. Time Response

In addition to the steady-state on-chip temperature distribution, the sensor's thermal transient response can also be of interest for various applications. For instance, in dynamic thermal/leakage management, the dynamic variation of on-chip temperature is used to adjust the operation of the chip such that the leakage power and the peak chip temperature can be properly controlled [19].

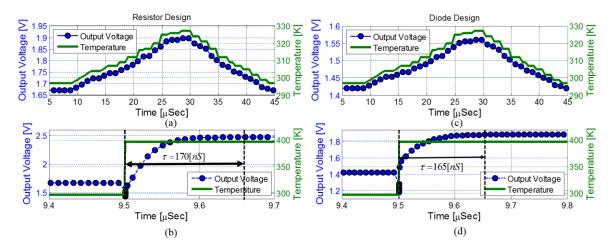

The time response of a temperature sensor is defined as the time it takes the sensor output to achieve 63% of its final value after a step change in temperature is impressed on its surface. To perform thermal transient analysis, a numerical integration method such as the backward Euler is required [20]. To solve the thermal transient analysis problem, one can model the thermal system as an equivalent RC circuit. Then, a SPICE-like simulation technique can be applied to the equivalent RC circuit to provide the thermal transient response [20,21]. In this study the PTAT time response was simulated using SPICE circuit simulator with BSIM4 MOSFET models [17]. The standard MOSFET models were changed to include a parameter describing each device specific temperature rise above the simulated ambient temperature, i.e.,  $t_{rise}$ . Then, in order to simulate a local temperature, only trise of the MOSFETs composing the temperature sensing circuit were changed externally and the PTAT output voltage was sampled. The transient simulation results are presented in Figure 5 for both PTAT designs and two temperature profiles: a graduate and a step temperature change.

**Figure 5.** Simulated time response to a graduate local temperature change (**a**,**c**) and to a step change in local temperature (**b**,**d**) for both PTAT designs.

Figure 5a,c show the PTAT response to a graduate temperature change; from  $t=10~\mu s$  to  $t=30~\mu s$  the circuit local temperature increases from 295 K to 330 K ( $t_{rise}=35~K$ ) and then it starts to cool down to room temperature. This is a lifelike scenario for most CMOS-SOI applications were the thermal time constants are long [22]. It can be easily concluded that both PTAT designs follow the temperature changes accurately and without delay, meaning that the time response of the circuit is much smaller than chip thermal time constants.

The time response of each design is obtained by simulating a step change in the sensor local temperature and the results are presented in Figure 5b,d. Time constants of 170 ns and 165 ns were calculated for the resistor and diode based designs, respectively.

# 3. V<sub>t</sub> Extractor Circuit

We previously proposed to determine the chip local temperature by measuring the transistor threshold voltage [14]. This requires a careful thermal characterization of  $V_t(T)$  and  $\mathrm{d}V_t/\mathrm{d}T$  of the process under study. Subsequently, by monitoring the changes in  $V_t$  under actual operation, the true local temperature of devices can be determined. We refer to this method as "Threshold—Voltage

Thermometry" and we recently described it in details in [14]. In order to implement this method the MOSFET threshold voltage needs to be extracted during the chip operation, i.e., on-line. This was done by using a  $V_t$  extractor circuit [23–27]. A  $V_t$  extractor is a circuit that extracts the threshold voltage of a MOS device according to the device local temperature [23].

# 3.1. Principle of Operation

The architecture for a  $V_t$  extractor circuit which we have chosen to implement is based on [28]. We chose this design because it combines a simple low voltage  $V_t$  extracting block and feedback, to achieve independence of the output from the supply voltage, low current consumption (therefore, low consumption), accuracy of the extracted threshold voltage toward supply voltage variations and transistor mismatch.

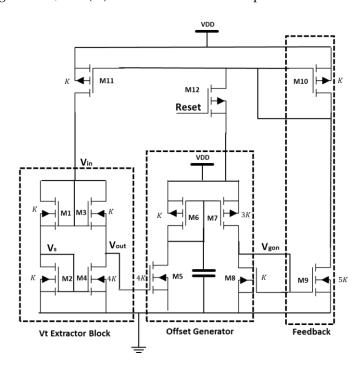

The tested extractor is presented in Figure 6 and consists of three blocks: (i) a simple  $V_t$  extracting block; (ii) an offset generator; and (iii) the current feedback loop.

**Figure 6.** Schematic of  $V_t$  Extractor circuit.

## 3.1.1. Analysis of $V_t$ Extracting Block

Assuming transistors M1 till M4 are all operating in saturation, with the ratios of (W/L) shown in Figure 6 ( $K_1 = K_2 = K_3 = K_4/4 = K$ ), eliminating body effect ( $V_{bs,i} = 0$ ) by connecting the bulk and source terminals in order to improve the circuit accuracy, and assuming that the drain current ( $I_d$ ) of each MOSFET follows the simple quadratic law:

$$I_{d_i} = K_i (V_{gs_i} - V_t)^2 (6)$$

then:

$$I_{d1} = I_{d2} \Rightarrow V_s = V_{in}/2$$

$$I_{d3} = I_{d4} \Rightarrow V_{out} = V_t$$

(7)

where the voltage nodes ( $V_s$ ,  $V_{in}$  and  $V_{out}$ ) are shown in Figure 6 and  $K_i$  is the transcoductance of transistor i.

In order to compensate for channel length modulation, mobility reduction and transistor mismatch the following feedback to the  $V_t$  extractor block ( $V_{in}$ ) is needed [23]:

$$V_{in} = 2V_{out} + 2V_{off} (8)$$

where  $V_{off}$  is several  $(k_BT/q)$ .

## 3.1.2. Analysis of Offset Generator

In the attempt to implement the feedback shown in Equation (8), an offset should be added to  $V_{out}$ . The purpose of the offset generator is to take the  $V_t$  extractor block output and add an offset of several  $(k_BT/q)$  to this value. Considering that  $V_{out}$  is close to  $V_t$ , then  $V_{gs5} - V_t < 3k_BT/q$ , subthreshold drain current equations are used in order to calculate this block's output  $-V_{gon}$ :

$$aI_{d5} = I_{d8} \Rightarrow aI_0 \exp(V_{out}/(k_B T/q)) = \frac{I_0}{b} \exp(V_{gon}/(k_B T/q))$$

$$\Rightarrow V_{gon} = V_{out} + (k_B T/q) \ln(ab)$$

(9)

where  $a = K_7/K_6$  is the p-mirror current gain and b is the ratio  $K_5/K_8$ . Hence,  $V_{gon}$  includes the necessary offset from  $V_{out}$ .

## 3.1.3. Analysis of Feedback Block

Transistors M9 and M4 in Figure 6 are 5 and 4 times wider than M2, respectively, and due to the current mirror formed by M10 and M11,  $V_{gon}$  is fed back to  $V_s$  as follows:

$$I_{d9} = I_{d2} + I_{d4} \Rightarrow V_s = V_{gon} \stackrel{(6)+(9)}{\Rightarrow} V_{in} = 2V_{out} + 2(k_BT/q)\ln(ab)$$

(10)

so the proposed feedback implements Equation (10), corresponding to Equation (8) resulting in a very accurate extraction of the threshold voltage.

# 3.2. Implementation

The circuit was implemented in 1  $\mu$ m PD CMOS-SOI process [15]. The MOSFET (W/L) ratio was chosen by performing a large number of parametric simulations in which the circuit output was compared with the simulated threshold voltage calculated using BSIM4 MOSFET [17] models at different temperatures. For supply voltage of 5 V, an optimal performance in terms of accuracy, chip area and circuit power consumption was achieved for body connected transistors with body contact shortened to the source ( $V_{bs_i}=0$ ) and W/L ratio of 4/9  $\mu$ m/ $\mu$ m for all transistors in the  $V_t$  extractor, offset generator and feedback blocks. The capacitor in the offset generator block is used to prevent parasitic oscillation and noise disturbances during transient. The resent transistor (M12) is set with minimum sizing ( $W/L=4/1~\mu$ m/ $\mu$ m) and used as an on/off switch for the  $V_t$  extractor circuit.

Overall, the circuit occupies a chip area of  $80\times100~\mu m^2$  and its measured power consumption at room temperature is 27.5  $\mu$ W.

## 3.3. Measurements and Simulations

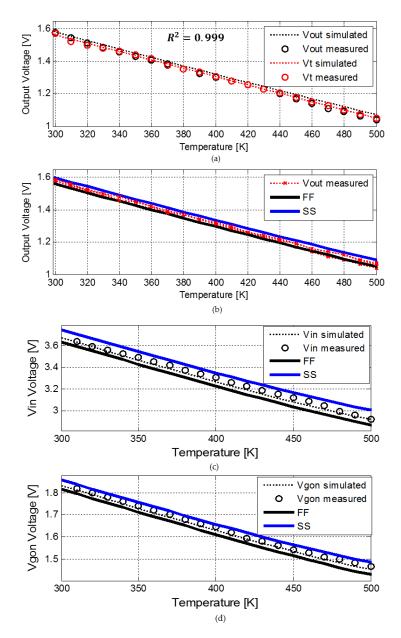

The  $V_t$  extractor voltage was measured at several nodes, see Figure 6, in temperatures ranging from 300 K to 500 K. The measured output voltage is compared to circuit DC simulations, the nominal threshold voltage obtained from BSIM4 MOSFET [17] models and process thermal characterization in order to determine the sensors accuracy. In addition, process corner simulations were run to predict linearity robustness over process variations compared to typical operation.

Figure 7 shows the measured and simulated temperature dependence of the  $V_t$  extractor circuit voltages ( $V_{out}$ ,  $V_{in}$  and  $V_{gon}$ ) for three different samples from 300 K to 500 K. The threshold voltage

Sensors 2018, 18, 1629 10 of 14

calculated using BSIM4 MOSFET [17] model and the one extracted during the process thermal characterization are presented as well. In Figure 7 only the corners with worst case variations are shown—FF and SS.

**Figure 7.** Comparison of the measured and simulate  $V_t$  extractor circuit different voltages (a) Vout and  $V_t$  (b) measured  $V_{out}$  for three different chips (c)  $V_{in}$  and (d)  $V_{gon}$ . Dots: experimental data; dashed lines: simulation results using the SPICE circuit simulator based on and BSIM4 MOSFET models; solid: circuit voltage in different process corners (FF and SS).

To evaluate the linearity of the  $V_t$  extractor circuit the coefficient of determination  $R^2$  [18] has been used like in the PTAT sensors case. As seen from Figure 7a the circuit output is linear with temperature in the entire temperature range ( $R^2$  = 0.999 for all measured samples) and produces a maximum error of ~1% (~12 mV DC shift) from the simulated and measured  $V_t$  values for all measured samples. At high temperatures, the increase in the excess voltage ( $V_{off}$ ) can cause nonlinearity in the temperature sensing capability of the  $V_t$  extractor circuit due to the offset created between the desired feedback, as indicated in Equation (8), and  $V_{in}$ . Hence, if the generated  $V_{in}$  is too high, the transistors

in the  $V_t$  extractor block (presented in Figure 6) won't operate in saturation causing nonlinearity of the output voltage.

The measured sensor sensitivity given by the slope of  $V_{out}$  vs. T shown in Figure 7a is 2.6 mV/K, which is close to the threshold voltage dependence upon temperature ( $dV_t/dT$ ) obtained from simulation (-2.5 mV/K) and is consistent over the three samples. There is a good correspondence between all measured and simulated results for all sampled circuit voltages ( $V_{out}$ ,  $V_{in}$  and  $V_{gon}$ ), as shown in Figure 7a–d. The corner analysis demonstrates that the maximum temperature error due to process variations occurs for the SS corner and caused a maximum offset of 25 mV in the circuit output voltage. In addition, as seen in Figure 7b, there are minor variations between the different measured samples which verifies the robustness, independence of the output voltage upon transistor mismatch and repeatability of this design.

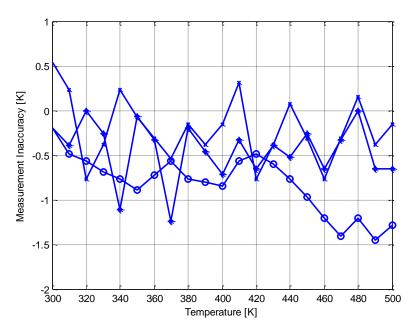

The measurement inaccuracy in the temperature sensing ( $\Delta T$ ) has been obtained by calculating the difference,  $\Delta V$ , between the circuits measured output voltage and the threshold voltage extracted during the process thermal characterization, which is then converted into temperature using the measured  $\mathrm{d}V_t/\mathrm{d}T$ . Accordingly, the error in temperature is estimated by:

$$\Delta T = \frac{\left| V_{out,measured} - V_{t,measured} \right|}{dV_{t}/dT} \tag{11}$$

Figure 8 shows the temperature error as a function of applied temperature for three different chips. The worst-case errors occur at high temperatures ( $\sim$ 500 K) most likely due to the excess voltage  $V_{off}$ , which is proportional to the thermal voltage ( $k_BT/q$ ), causing a large variation from the desired feedback as indicated in Equation (8). After applying common-centroid and other matching techniques in the layout the maximum error due to offset is 1.5 K around 500 K, as shown in Figure 8. At the low end of the temperature range near room temperature, the error is much less, around 0.5 K. In future design, offset cancellation techniques such as chopping and auto-zeroing can be applied to further reduce the effect of offset on the sensor accuracy and improve the performance.

Figure 8. Measurement inaccuracy versus temperature for three different chips.

### 3.4. Time Response

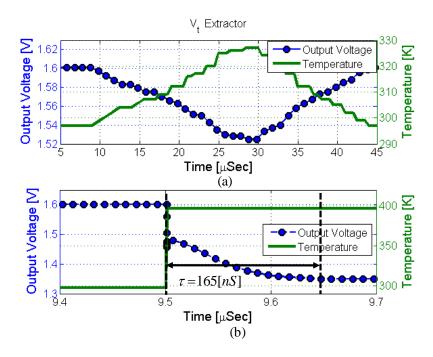

The time response of the  $V_t$  extractor circuit was simulated under the same conditions (graduate and step change in temperature) as the PTAT and the results are shown in Figure 9. Figure 9a present

the  $V_t$  extractor response to a graduate temperature change and it can be easily seen that the sensor follows the temperature changes accurately and without delay; meaning a decrease in the output voltage when temperature increases and vice versa during the chip cool down.

**Figure 9.** Simulated time response to a (**a**) graduate local temperature change and to a (**b**) step change in local temperature.

The time response of the sensor is obtained by simulating a step change in the sensor local temperature and the results are presented in Figure 9b. A Time constant of 165 ns was calculated from this simulation.

# 4. Summary

In this paper the thermal performance of various circuits for temperature sensing and monitoring manufactured in 1 μm PD CMOS-SOI technology was characterized and compared in the temperature range of 300 K-500 K. All sensors exhibit linearity and high sensitivity over the entire temperature range. However, the lateral diodes based PTAT design is inaccurate due to diode mismatches caused by the dependence of the saturation current upon diode dimensions. A resistor based PTAT has good accuracy but requires high power consumption during operation. The PTAT circuit is best utilized when implementing temperature independent current or voltage sources (Band Gap References), although a carful calibration is needed. The implemented  $V_t$  extractor circuit has a small error (1%) under nominal conditions, linear dependence upon temperature, low power consumption, low area and fast response time. This makes this sensor optimal to be used as a temperature sensor for thermal management in CMOS-SOI technologies. A performance comparison between the sensors reported in this paper and the recent on-chip temperature sensors is shown in Table 1. As evident, the  $V_t$  extractor circuit presented here is smaller than most reported sensors and has low power consumption while achieving good accuracy with no need in additional calibration. The circuit will be useful as a temperature sensor in high-performance analog, mixed-signal, and digital ICs due to its high performance and low power consumption. Other applications for this temperature sensor are IR sources or detectors and new generation of smart sensors, like gas sensors, where temperature monitoring is necessary to achieve better sensitivity and selectivity in presence of different gases [6].

| Sensor                                          | Process             | Range<br>(K) | Area<br>(mm²) | Power<br>(μW) | Maximum<br>Sensitivity<br>(mV/K) | Linearity<br>(R <sup>2</sup> ) | Accuracy<br>(K) | Calibration<br>Need |

|-------------------------------------------------|---------------------|--------------|---------------|---------------|----------------------------------|--------------------------------|-----------------|---------------------|

| [7]                                             | 150 nm<br>CMOS SOI  | 150-400      | -             | -             | 0.7                              | 0.99                           | -               | Needed              |

| [9]                                             | FD CMOS<br>SOI      | 100-400      | 0.04          | -             | -2.2                             | -                              | 2               | Needed              |

| [10]                                            | 1 μm CMOS<br>SOI    | 300-1053     | -             | 27            | -1.22                            | -                              | -               | -                   |

| [12]                                            | 32 nm<br>CMOS SOI   | 270–370      | 0.001         | 100           | -                                | -                              | 1.95 (3σ)       | Needed              |

| [13]                                            | 1 μm PD<br>CMOS SOI | 300-500      | 0.45          | 112.5         | -                                | -                              | 2               | Needed              |

| [24]                                            | 0.35 μm<br>CMOS     | 250-350      | 0.055         | 0.3           | 15 (ppm/C)                       | -                              | -               | -                   |

| [25]                                            | 1 μm PD<br>CMOS SOI | 250-520      | 0.23          | -             | 27 (ppm/C)                       | -                              | 1.8 (%)         | Needed              |

| [27]                                            | 0.35 μm<br>CMOS     | 270-400      | 0.011         | 24            | 11.8<br>(ppm/C)                  | -                              | 0.153 (%)       | -                   |

| Resistor based PTAT (This work)                 | 1 μm PD<br>CMOS SOI | 300-500      | 0.0085        | 250           | 9.8                              | 0.9988                         | 1.5             | Needed              |

| Diode based PTAT<br>(This work)                 | 1 μm PD<br>CMOS SOI | 300-500      | 0.026         | 45            | 4.7                              | 0.9985                         | 6.5             | Needed              |

| V <sub>t</sub> Extractor Circuit<br>(This work) | 1 μm PD<br>CMOS SOI | 300-500      | 0.008         | 27.5          | 2.6                              | 0.999                          | 1.5             | Not Needed          |

**Table 1.** Performance comparison.

**Author Contributions:** The work presented in this paper was a collaboration of all authors. M.M. designed/performed the experiments and wrote the paper. I.B. designed the PTAT circuits. Y.N. guided the research work and revised the paper.

**Acknowledgments:** This work was supported by the Sarah and Moshe Zisapel nano-electronics Center at the Technion—Israel Institute of Technology. The help of Ida Shumpei from Murata in the transient simulations is highly appreciated.

Conflicts of Interest: The authors declare no conflict of interest.

### References

- Poirier, C.; McGowen, R.; Bostak, C.; Naffziger, S. Power and temperature control on a 90 nm Itanium-family processor. In Proceedings of the IEEE ISSCC Digest of Technical Papers, San Francisco, CA, USA, 10 February 2005; pp. 304–305.

- 2. Duarte, D.; Geannopoulos, G.; Muhgal, U.; Wong, K.; Taylor, G. Temperature sensor design in a high volume manufacturing 65 nm CMOS digital process. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 16–19 September 2007; pp. 221–224.

- 3. Li, Y.; Lakdawala, H. Smart integrated temperature sensor Mixed signal circuits and systems in 32-nm and beyond. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 19–21 September 2011; pp. 1–8.

- 4. Pertijs, M.A.P.; Niederkorn, A.; Ma, X.; McKillop, B.; Bakker, A.; Huijsing, J.H. A CMOS smart temperature sensor with a  $3\sigma$  inaccuracy of  $\pm 0.5$  °C from -50 °C to 120 °C. *IEEE J. Solid-State Circuits* **2005**, 40, 454–461. [CrossRef]

- 5. Bakker, A.; Huijsing, J. Micropower CMOS temperature sensor with digital output. *IEEE J. Solid-State Circuits* **1996**, *31*, 933–937. [CrossRef]

- 6. Zviagintsev, A.; Blank, T.; Brouk, I.; Bloom, I.; Nemirovsky, Y. Modeling the Performance of Nano Machined CMOS Transistors for Uncooled IR Sensing. *IEEE Trans. Electron Devices* **2017**, *64*, 4657–4663. [CrossRef]

- 7. Souza, M.; Pavanello, M.A.; Flandre, D. Low power highly linear temperature sensor based on SOI lateral PIN diodes. In Proceedings of the IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, USA, 10–13 October 2016.

8. De Souza, M.; Rue, B.; Flandre, D.; Pavanello, M.A. Thermal sensing performance of lateral SOI PIN diodes in the 90–400 K range. In Proceedings of the IEEE International SOI Conference, Foster City, CA, USA, 5–8 October 2009.

- 9. De Souza, M.; Rue, B.; Flandre, D.; Pavanello, M.A. Thin-Film Lateral SOI PIN Diodes for Thermal Sensing Reaching the Cryogenic Regime. *J. Integr. Circuits Syst.* **2010**, *5*, 160–167.

- Santra, S.; Guha, P.K.; Ali, S.Z.; Haneef, I.; Udrea, F. Silicon on Insulator Diode Temperature Sensor—A

Detailed Analysis for Ultra-High Temperature Operation. *IEEE Sens. J.* 2010, 10, 997–1003. [CrossRef]

- 11. Santra, S.; Guha, P.K.; Haque, M.S.; Ali, S.Z.; Udrea, F. Si diode temperature sensor beyond 300 °C. In Proceedings of the 2007 International Semiconductor Conference, Sinaia, Romania, 15 October–17 September 2007; pp. 415–418.

- 12. Chowdhury, G.; Hassibi, A. An On-Chip Temperature Sensor with a Self-Discharging Diode in 32-nm SOI CMOS. *IEEE Trans. Circuits Syst. II Express Briefs* **2012**, *59*, 568–572. [CrossRef]

- 13. Pathrose, J.; Zou, L.; Chai, K.T.C.; Je, M.; Xu, Y.P. A Time-Domain Smart Temperature Sensor without an Explicit Bandgap Reference in SOI CMOS Operating up to 225 °C. In Proceedings of the IEEE Asian Solid-State Circuits Conference (A-SSCC), Singapore, 11–13 November 2013.

- 14. Malits, M.; Nemirovsky, Y. Nanometric Integrated Temperature and Thermal Sensors in CMOS-SOI Technology. *Sensors* **2017**, *17*, 1739. [CrossRef] [PubMed]

- 15. XFAB CMOS-SOI 1 μm Process XI10. Available online: https://www.xfab.com/en/technology/soi/10-um-xi10/ (accessed on 18 March 2018).

- 16. Gray, P.R.; Hurst, P.J.; Lewis, S.H.; Meyer, R.G. *Analysis and Design of Analogue Integrated Circuits*, 5th ed.; John Wiley & Sons: New York, NY, USA, 2009; pp. 321–324.

- 17. Berkeley Short-Channel IGFET Model (BSIM). Available online: http://www-device.eecs.berkeley.edu/bsim/ (accessed on 8 March 2018).

- 18. Nagelkerke, N.J.D. A note on the general definition of the coefficient of determination. *Biometrika* **1991**, *78*, 691–692. [CrossRef]

- 19. Li, P.; Pileggi, L.T.; Asheghi, M.; Chandra, R. IC thermal simulation and modeling via efficient multigrid-based approaches. *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.* **2006**, 25, 1763–1776.

- Cheng, Y.; Raha, P.; Teng, C.; Rosenbaum, E.; Kang, S. ILLIADS-T: An electro thermal timing simulator for temperature-sensitive reliability diagnosis of CMOS VLSI chips. *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.* 1998, 17, 668–680. [CrossRef]

- 21. Yu, Z.; Yergeau, D.; Dutton, R.; Nakagawa, S.; Deeney, J. Fast placement-dependent full chip thermal simulation. In Proceedings of the 2001 International Symposium on VLSI Technology, Systems, and Applications, Hsinchu, Taiwan, 18–20 April 2001; pp. 249–252.

- 22. Székely, V.; Rencz, M. Thermal Dynamics and the Time Constant Domain. *IEEE Trans. Compon. Packag. Technol.* **2000**, 23, 587–594. [CrossRef]

- 23. Allen, P.E.; Holberg, D.R. *CMOS Analog Circuit Design*, 3rd ed.; Holt, Rinehard and Winston: New York, NY, USA, 2011; pp. 153–160.

- 24. Ueno, K.; Hirose, T.; Asai, T.; Amemiya, Y. A 300 nW, 15 ppm/C, 20 ppm/V CMOS Voltage Reference Circuit Consisting of Subthreshold MOSFETs. *IEEE J. Solid-State Circuits* **2009**, 44, 2047–2054. [CrossRef]

- 25. Pathrose, J.; Zou, L.; Chai, K.T.C.; Je, M.; Xu, Y.P. Temperature Sensor Front End in SOI CMOS Operating up to 250 °C. *IEEE Trans. Circuits Syst. II Express Briefs* **2014**, *61*, 496–500. [CrossRef]

- 26. Nang, L.K.; Mok, P.K.T. A CMOS voltage reference based on weighted  $\Delta V_{GS}$  for CMOS low-dropout linear regulators. *IEEE J. Solid-State Circuits* **2003**, *38*, 146–150.

- 27. Zhou, Z.; Zhu, P.; Shi, Y.; Wang, H.; Ma, Y.; Xu, X.; Tan, L.; Ming, X.; Zhang, B. A CMOS voltage reference based on mutual compensation of *V*<sub>tn</sub> and *V*<sub>tp</sub>. *IEEE Trans. Circuits Syst. II Express Briefs* **2012**, *59*, 341–345. [CrossRef]

- 28. Fikos, G.; Siskos, S. Low-Voltage Low-Power Accurate CMOS V<sub>t</sub> Extractor. *IEEE Trans. Circuit Syst. II Analog Digit. Signal Process.* **2001**, 48, 626–628. [CrossRef]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).