Article

# Linearized Discrete Charge Balance Control with Simplified Algorithm for DCM Buck Converter

Run Min <sup>1</sup>D, Dian Lyu <sup>1</sup>, Shuai Cheng <sup>2</sup>, Yingshui Sun <sup>3,\*</sup> and Linkai Li <sup>1</sup>

- School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, China

- Silergy Semiconductor Technology Co., Ltd., Hangzhou 310000, China

- Commercial Headquarters, COSCO Shipping Heavy Industry Co., Ltd., Shanghai 200135, China

- \* Correspondence: swem\_sun@cosco-shipyard.com; Tel.: +86-21-5860-6301

Received: 29 July 2019; Accepted: 16 August 2019; Published: 19 August 2019

**Abstract:** In this paper, a linearized discrete charge balance (LDCB) control strategy is proposed for buck converter operating in discontinuous conduction mode (DCM). For DC-DC power converters, discrete charge balance (DCB) control is an attractive approach to improve the output voltage transient response. However, as a non-linear control strategy, the algorithm is complex, which is difficult for implementation. To reduce the complexity, this paper proposes the LDCB control strategy that is derived through linearizing conventional DCB controller. By deriving the differential functions of the DCB control algorithm, the small signal relationship between the input and output of DCB controller is explored. Furthermore, based on the relationship, the LDCB controller is formed through three parallel feed loops to the duty ratio. As a linear control approach, the achieved LDCB controller is greatly simplified for implementation. This not only saves the hardware cost, but also reduces the calculation lag, which provides potential to improve the switching frequency. Besides, since the LDCB controller shares the same small signal model as that of DCB controller, it achieves similar control loop bandwidth and transient performance. Effectiveness of the proposed LDCB control is verified by zero/pole plots, transient analyses and experimental results.

**Keywords:** charge balance; converter; DC-DC; DCM; estimator; transient response

#### 1. Introduction

In portable and processor applications, there is a continuous demand for a fast output voltage transient response. Therefore, a lot of control strategies are proposed for different DC-DC power converters. Among many strategies, the well-known  $V^2$  controls have been widely used in industrial applications, and they can achieve a great control loop bandwidth [1–3]. Predictive controls acquire state variables ahead of time, which allow earlier actions to stabilize the system [4,5]. Adaptive controls can achieve optimized performance in different conditions, which is ensured by online tunings for control parameters [6,7]. Current mode controls are effective approaches to simplify compensator design, and they can achieve fast transient performance with over current protection [8–10]. Multiloop controls are popular for their closed-loop stability and flexible load/line transient optimizations [11,12]. Sliding mode and hysteretic controls are non-linear strategies to optimize large-signal transient responses, and they are not only robust to parameter deviations, but also easy for implementation [13–15].

To achieve time-optimal output voltage transient responses, various control strategies have recently been investigated, such as time-optimal sliding-mode control [16,17], bang-bang and geometric control [18], programmable deviation current control [19], etc. Among many strategies, a practical approach to achieve time-optimal control is through capacitor charge balancing method [20–22].

Energies **2019**, 12, 3177 2 of 17

These controls adopt variable switching-on and switching-off durations to balance the charge on output capacitor, and achieve optimal output voltage transient response. Furthermore, various methods are proposed to carry out the control with digital circuits [23–26]. However, these control strategies induce a variable switching frequency, which challenges the converter modeling and EMI suppression [27,28]. Besides, all above charge balance controls are limited for buck converters operating in continuous conduction mode (CCM).

When a converter operates in discontinuous conduction mode (DCM), the discontinuous inductor current provides potential advantages of high stability, simple compensation, compact and low-cost inductor, etc. [29,30]. For DC-DC converters operating in DCM, a novel control strategy based on estimation and charge balance principle is proposed in [31]. This forms the discrete charge balance (DCB) control where all control variables are updated once every cycle. The approach is based on digital pulse wide modulation (DPWM) with a fixed switching frequency, and suits various converters, such as boost and flyback converters, etc. Furthermore, with comprehensive consideration of parasitics, the control accuracy is improved in [32,33]. However, all above DCB algorithms are non-linear, and they induce complicated calculations. Besides, the calculations must be carried out in serial, i.e., charge estimation, charge compensation and charge regulation. These not only increase the hardware cost, but also cause considerable calculation lag that limits the switching frequency.

In order to solve above mentioned issues, a linearized discrete charge balance (LDCB) control strategy is proposed in this paper, which is acquired through linearizing conventional DCB controller. By deriving the differential functions of the DCB algorithm, the small signal relationship between the input and output of DCB controller is explored. Furthermore, the LDCB controller is formed through three independent feed loops, where the outputs are summarized as duty ratio. In this way, the LDCB controller eliminates several complicated calculations, such as divisions and square roots. Besides, since the relationship between the input and output is explicitly revealed, all loops can be carried out in parallel. Both the simplified algorithm and the parallelism help to save the hardware cost, reduce the calculation lag, and provide potential to improve the switching frequency. Furthermore, since the LDCB controller shares the same small signal model as that of DCB controller, it achieves similar control loop bandwidth and transient performance. The stability and robustness under LDCB control are proved by closed-loop modeling, transient analyses and zero/pole plots.

The paper is organized as follows. In Section 2, control scheme and algorithm of the conventional DCB control strategy is introduced. The proposed LDCB controller is given in Section 3, where the small signal relationship between the input and output of DCB controller is explored. In Section 4, detailed closed-loop modeling under LDCB control is derived. Furthermore, the stability and robustness are proved by zero/pole plots and transient analyses. Experimental results and comparisons are given in Section 5 to verify effectiveness of the proposed LDCB controller. Finally, a brief conclusion is given in Section 6.

# 2. Conventional Discrete Charge Balance Control

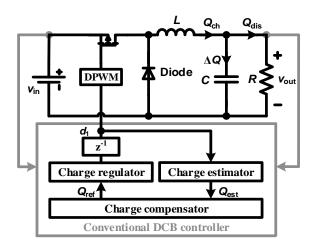

For switched mode power converters, the output capacitor is charged and discharged periodically. At steady state, the charge and discharge are equal, which ensures a constant output voltage. When operating in DCM, the charge can be strictly controlled by the duty ratio of DPWM signal. Therefore, the output voltage can be controlled by balancing the charge on the output capacitor [31–33]. This forms the DCB control strategy, and a buck converter under conventional DCB control is shown in Figure 1.

The DCB controller consists a charge estimator, a charge compensator and a charge regulator. First, the charge estimator calculates the charge to output capacitor, denoted as the estimated charge  $Q_{\text{est}}$ . An appropriate charge estimator ensures that  $Q_{\text{est}} = Q_{\text{ch}}$ , where  $Q_{\text{ch}}$  is the actual output charge. Second, to balance the charge on output capacitor, the charge compensator outputs a reference for output charge, denoted as  $Q_{\text{ref}}$ . Algorithm of the compensator determines the output voltage transient

Energies **2019**, 12, 3177 3 of 17

responses to load and input. Finally, the charge regulator adjusts a suitable duty ratio  $d_1$  to ensure that  $Q_{ch}$  tracks  $Q_{ref}$  in the next switching cycle.

Figure 1. Buck converter under conventional discrete charge balance (DCB) control.

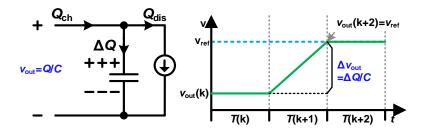

As shown in Figure 2, the output voltage is controlled by increasing or decreasing the charge on output capacitor. Since the voltage across the capacitor is  $v_{\rm out} = Q/C$ , the voltage increment is given by  $\Delta v_{\rm out} = \Delta Q/C = (Q_{\rm ch} - Q_{\rm dis})/C$  where  $Q_{\rm dis}$  is the discharge of the capacitor. Furthermore,  $\Delta v_{\rm out}$  can be regulated by  $Q_{\rm ch}$  since  $Q_{\rm dis}$  varies slow owing to the filtering effect of C. For example, when  $v_{\rm out}$  is lower than  $v_{\rm ref}$  in the kth switching cycle, the DCB controller increases  $Q_{\rm ch}$  to generate a positive  $\Delta v_{\rm out}$ . Finally, the output voltage is regulated to its reference value in the (k+2)th switching cycle.

Figure 2. Output voltage under discrete charge balance (DCB) control.

#### 2.1. Charge Compensator

The charge compensator regulates the output voltage by compensating the charge on output capacitor. For discrete-time analyses, the voltage increment  $\Delta v_{\rm out} = (Q_{\rm ch} - Q_{\rm dis})/C$  is transformed as

$$v_{\text{out}}(k+1) - v_{\text{out}}(k) = \frac{Q_{\text{ch}}(k) - Q_{\text{dis}}(k)}{C}.$$

(1)

Since the discharge is determined by  $Q_{\rm dis}(k) = v_{\rm out}(k)T/R$ , (1) is derived as

$$v_{\text{out}}(k+1) - v_{\text{out}}(k) + \frac{T}{RC}v_{\text{out}}(k) = \frac{Q_{\text{ch}}(k)}{C}.$$

(2)

Furthermore, iterating (2) gives

$$v_{\text{out}}(k+2) - 2v_{\text{out}}(k) + v_{\text{out}}(k-2) + \frac{T}{RC} \left[ v_{\text{out}}(k+1) + v_{\text{out}}(k) - v_{\text{out}}(k-1) - v_{\text{out}}(k-2) \right] = \frac{Q_{\text{ch}}(k+1) + Q_{\text{ch}}(k) - Q_{\text{ch}}(k-1) - Q_{\text{ch}}(k-2)}{C} .$$

(3)

Energies **2019**, 12, 3177 4 of 17

Nevertheless, is comparable to the output voltage ripple ratio, which is much smaller than unity in most DC-DC applications [34], thus (3) approximates

$$v_{\text{out}}(k+2) - 2v_{\text{out}}(k) + v_{\text{out}}(k-2) \approx \frac{Q_{\text{ch}}(k+1) + Q_{\text{ch}}(k) - Q_{\text{ch}}(k-1) - Q_{\text{ch}}(k-2)}{C}.$$

(4)

To regulate the output voltage to its reference value in the (k+2)th switching cycle, the charge compensator should provide a reference charge  $Q_{\rm ref}(k) = Q_{\rm ch}(k+1)$  that ensures  $v_{\rm out}(k+2) = v_{\rm ref}(k)$ . Therefore, taking  $Q_{\rm ref}(k) = Q_{\rm ch}(k+1)$ ,  $v_{\rm out}(k+2) = v_{\rm ref}(k)$  and  $Q_{\rm ch}(k) = Q_{\rm est}(k)$  into (4) gives

$$Q_{\text{ref}}(k) = -Q_{\text{est}}(k) + Q_{\text{est}}(k-1) + Q_{\text{est}}(k-2) + C[v_{\text{ref}}(k) - 2v_{\text{out}}(k) + v_{\text{out}}(k-2)].$$

(5)

Based on (5), a reference charge for the (k+1)th switching cycle is calculated, which makes the output voltage tracking the reference voltage in two switching cycles. Furthermore, to carry out the algorithm in (5), a charge estimator must be derived to estimate  $Q_{\rm ch}$ , while a charge regulator should also be provided to calculate an appropriate  $d_1$ .

# 2.2. Charge Estimator and Charge Regulator

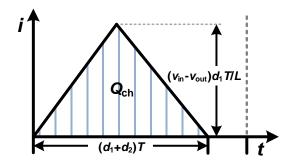

The DCB controller carries out charge estimation, charge compensation and charge regulation in serial. The charge estimator is required to estimate the output charge, while the charge regulator is needed to calculate an appropriate duty ratio. For DCM buck converter, the output charge in a switching cycle is determined by the inductor current. As shown in Figure 3, the inductor current rises linearly when the main switch is on, and it falls linearly when the main switch is off.

Figure 3. Output charge of buck converter under discontinuous conduction mode (DCM).

The output charge is the integration of inductor current, i.e., the shadow area in Figure 3. For buck converter, the inductor current peak value is  $(v_{\rm in} - v_{\rm out})d_1T/L$  while  $(d_1 + d_2)T = v_{\rm in}d_1T/v_{\rm out}$  is always valid. Therefore, the output charge is given by

$$Q_{\rm ch} = \frac{d_1^2 T^2 (v_{\rm in} - v_{\rm out}) v_{\rm in}}{2 v_{\rm out} L}.$$

(6)

Based on (6), the charge estimation and regulation algorithms are derived as

$$\begin{cases} Q_{\text{est}} = \frac{(d_1 T)^2 (v_{\text{in}} - v_{\text{out}}) v_{\text{in}}}{2 v_{\text{out}} L} \\ d_1 = \frac{1}{T} \sqrt{\frac{2 v_{\text{out}} L Q_{\text{ref}}}{(v_{\text{in}} - v_{\text{out}}) v_{\text{in}}}} \end{cases}$$

(7)

These algorithms can ensure accurate charge estimation and charge regulation under DCM operation. However, they are relatively complicated owing to the square-root and division operations. Besides, the charge compensator and charge regulator are dependent on the charge estimator, thus the calculations must be processed in serial. These not only increase the hardware cost, but also cause considerable calculation lag that limits the switching frequency.

Energies **2019**, 12, 3177 5 of 17

# 3. Linearized Discrete Charge Balance Control with Simplified Algorithm

Although conventional DCB controller can greatly optimize the control loop bandwidth and the output voltage transient response, it suffers a complicated algorithm and the serial calculations. These greatly increase the overall cost and the requirement for a high-performance digital control unit. A large calculation lag also limits the achievable switching frequency.

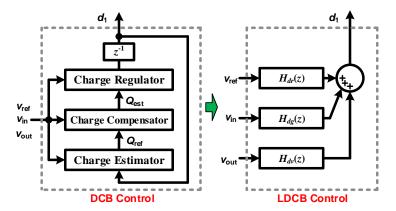

In order to solve above mentioned issues, the LDCB controller is proposed in this section. By deriving the differential functions of the DCB control algorithm, small signal relationship between the input and output of DCB controller is explored. Furthermore, the LDCB controller is formed through three independent feed loops, where the outputs are summarized as duty ratio. In this way, the LDCB controller eliminates several complicated calculations, such as divisions and square roots. Since the relationship between the input and output is explicitly revealed, all loops are carried out in parallel. Both the simplified algorithm and the parallelism help to save the hardware cost, reduce the calculation lag, and provide potential to improve the switching frequency.

# 3.1. Linearization of Conventional DCB Controller

To linearize DCB control, a partial differential function  $\hat{d}_1 = f(\hat{v}_{\text{in}}, \hat{v}_{\text{out}}, \hat{v}_{\text{ref}})$  is derived from the charge estimator, charge compensator, and charge regulator. Based on (7), differential function of the estimated charge is given by

$$\begin{cases} \hat{Q}_{\text{est}} = X_{1} \hat{d}_{1} + X_{2} \hat{v}_{\text{in}} + X_{3} \hat{v}_{\text{out}} \\ X_{1} = \frac{d_{1} T^{2} (v_{\text{in}} - v_{\text{out}}) v_{\text{in}}}{v_{\text{out}} L} = \frac{2v_{\text{out}} T}{d_{1} R} \\ X_{2} = \frac{d_{1}^{2} T^{2} (2v_{\text{in}} - v_{\text{out}})}{2v_{\text{out}} L} = \frac{v_{\text{out}} T (2v_{\text{in}} - v_{\text{out}})}{v_{\text{in}} (v_{\text{in}} - v_{\text{out}}) R} \\ X_{3} = -\frac{d_{1}^{2} T^{2} v_{\text{in}}^{2}}{2v_{\text{out}}^{2} L} = -\frac{Tv_{\text{in}}}{R (v_{\text{in}} - v_{\text{out}})} \end{cases}$$

(8)

where  $X_1$ ,  $X_2$  and  $X_3$  denote partial differential functions  $\partial Q_{\rm est}/\partial d_1$ ,  $\partial Q_{\rm est}/\partial v_{\rm in}$  and  $\partial Q_{\rm est}/\partial v_{\rm out}$ , respectively.

Since the charge controller uses  $Q_{\text{ref}}$  to calculate  $d_1$ , similar differential function is derived for the charge regulator:

$$\hat{d}_1 = \left(\frac{1}{X_1}\hat{Q}_{\text{ref}} - \frac{X_2}{X_1}\hat{v}_{\text{in}} - \frac{X_3}{X_1}\hat{v}_{\text{out}}\right)z^{-1}.$$

(9)

In (9), a unit delay  $z^{-1}$  is induced, since the duty ratio is pre-calculated for the next switching cycle. Furthermore, based on (5), differential function of  $Q_{\text{ref}}$  is given by

$$\hat{Q}_{\text{ref}} = (z^{-1} + z^{-2} - 1)\hat{Q}_{\text{est}} + C(-2 + z^{-2})\hat{v}_{\text{out}} + C\hat{v}_{\text{ref}}.$$

(10)

Finally, combining (8)–(10), a partial differential function  $\hat{d}_1 = f(\hat{v}_{in}, \hat{v}_{out}, \hat{v}_{ref})$  is derived as

$$\begin{cases}

\hat{d}_{1} = H_{dv}(z)\hat{v}_{\text{out}} + H_{dg}(z)\hat{v}_{\text{in}} + H_{dr}(z)\hat{v}_{\text{ref}} \\

H_{dv}(z) = \frac{\hat{d}_{1}}{\hat{v}_{\text{out}}} = -\frac{X_{3}}{X_{1}} \frac{2(1+C/X_{3})-z^{-1}-(1+C/X_{3})z^{-2}}{z+1-z^{-1}-z^{-2}} \\

H_{dg}(z) = \frac{\hat{d}_{1}}{\hat{v}_{\text{in}}} = -\frac{X_{2}}{X_{1}} \frac{2-z^{-1}-z^{-2}}{z+1-z^{-1}-z^{-2}} \\

H_{dr}(z) = \frac{\hat{d}_{1}}{\hat{v}_{\text{ref}}} = \frac{C}{X_{1}} \frac{1}{z+1-z^{-1}-z^{-2}}

\end{cases} (11)$$

This equation explicitly reveals the relationship between  $\hat{d}_1$  and  $\{\hat{v}_{out}, \hat{v}_{in}, \hat{v}_{ref}\}$ . Based on (11), the LDCB controller can be realized by three independent feedback and feed forward loops.

Energies **2019**, 12, 3177 6 of 17

#### 3.2. Realization of LDCB Control

Similar to conventional DCB control, the LDCB controller regulates the output voltage with three inputs, i.e.,  $v_{\text{ref}}$ ,  $v_{\text{out}}$  and  $v_{\text{in}}$ . Each of the inputs has an independent feeding loop to  $d_1$ , as shown in Figure 4.

**Figure 4.** Schemes of conventional discrete charge balance (DCB) controller and the linearized discrete charge balance (LDCB) controller.

Furthermore, since the LDCB controller maintains the same small signal model as conventional DCB controller, it achieves similar control loop bandwidth and transient performance. Besides, without calculating state variables (such as  $Q_{\rm est}$  and  $Q_{\rm ref}$ ), the LDCB controller has a simplified algorithm and features parallel calculations, as shown in Table 1.

Table 1. Comparison between the conventional DCB and LDCB control algorithms.

| Control Algorithms | DCB Algorithm                                                    | LDCB Algorithm                                                                |

|--------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Complexity         | Complex                                                          | Simple                                                                        |

| Parallelism        | Successively calculating $Q_{\rm est}$ , $Q_{\rm ref}$ and $d_1$ | Processing $H_{dr}(z)$ , $H_{dg}(z)$ and $H_{dv}(z)$ calculations in parallel |

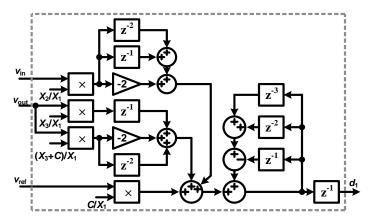

Based on (11), a further simplified implementation of LDCB controller is given in Figure 5. This implementation requires only six multipliers and nine adders. Moreover, all feeding loops calculations are processed in parallel, which greatly reduces the calculation lag. Therefore, compared with conventional DCB controller, the LDCB controller can reduce the hardware cost, while providing potential for a higher switching frequency.

**Figure 5.** Simplified implementation of the proposed linearized discrete charge balance (LDCB) controller.

Energies **2019**, 12, 3177 7 of 17

# 4. Closed-Loop Analysis and Robustness of LDCB Controller

To verify the stability under LDCB control, closed-loop small signal model is derived to investigate zeros and poles of the system. Since the LDCB controller is derived through linearizing conventional DCB controller, they share the same closed-loop small signal model at the typical operation point. However, when the operation point deviates, the system under LDCB control may fail owing the deviated model. Therefore, robustness of LDCB controller is further verified with  $\pm 30\%$  deviation of the operation point. Since the controller is digital, all analyses and simulations are carried out in discrete-time domain.

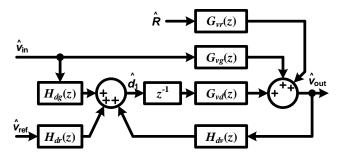

# 4.1. Closed-Loop Small Signal Model

Since  $v_{\rm in}$ ,  $d_1$  and R are independent variables in a DC-DC converter, their impacts to  $v_{\rm out}$  are modulated by three transfer functions, namely  $G_{vg}(z)$ ,  $G_{vd}(z)$  and  $G_{vl}(z)$ , respectively. Under LDCB control, the duty ratio is acquired through  $\{H_{dg}(z), H_{dv}(z), H_{dr}(z)\}$ . Therefore, the closed-loop small signal model under LDCB control is given by Figure 6.

Figure 6. Small signal model of the closed-loop system under LDCB control.

Based on transfer function of the output filtering network, the relationship between  $v_{\rm out}$  and  $Q_{\rm ch}$  is given by

$$v_{\text{out}}T = \frac{1}{sC}(Q_{\text{ch}} - \frac{v_{\text{out}}T}{R}). \tag{12}$$

Based on (12), differential function of  $v_{\text{out}}$  is given by

$$\hat{v}_{\text{out}} = \frac{1}{T} \frac{R}{sRC + 1} \hat{Q}_{\text{ch}} + \frac{v_{\text{out}}}{R} \frac{1}{sRC + 1} \hat{R}.$$

(13)

Furthermore, to derive the discrete-time transfer functions, (13) is transformed to its z domain, as shown in (14).

$$\hat{v}_{\text{out}} = \frac{1}{C} \frac{1}{z - 1 + a} \hat{Q}_{\text{ch}} + \frac{v_{\text{out}} T}{R^2 C} \frac{1}{z - 1 + a} \hat{R},\tag{14}$$

where a = T/RC. Since the charge to output is  $\hat{Q}_{ch} = X_1\hat{d}_1 + X_2\hat{v}_{in} + X_3\hat{v}_{out}$ , substituting  $\hat{Q}_{ch}$  into (14) gives

$$\begin{cases}

\hat{v}_{\text{out}} = G_{vd}(z)\hat{d}_{1} + G_{vg}(z)\hat{v}_{\text{in}} + G_{vl}(z)\hat{R} \\

G_{vd}(z) = \frac{\hat{v}_{\text{out}}}{\hat{d}_{1}} = \frac{X_{1}/C}{z-1+a-X_{3}/C} \\

G_{vg}(z) = \frac{\hat{v}_{\text{out}}}{\hat{v}_{\text{in}}} = \frac{X_{2}/C}{z-1+a-X_{3}/C} \\

G_{vl}(z) = \frac{\hat{v}_{\text{out}}}{\hat{R}} = \frac{v_{\text{out}}T}{z-1+a-X_{3}/C}

\end{cases} .$$

(15)

Energies **2019**, 12, 3177 8 of 17

Obviously, all the functions are first-order, and they share the same pole. Furthermore, based on Figure 6, closed-loop transfer functions from input voltage, reference voltage and load to the output voltage are given by

$$\begin{cases}

F_{vl}(z) = \frac{G_{vr}(z)}{1 - G_{vd}(z)H_{dv}(z)} \\

F_{vg}(z) = \frac{G_{vg}(z) + G_{vd}(z)H_{dg}(z)}{1 - G_{vd}(z)H_{dv}(z)} \\

F_{vr}(z) = H_{dr}(z) \frac{G_{vd}(z)}{1 - G_{vd}(z)H_{dv}(z)}

\end{cases} .$$

(16)

Substituting (15) and (11) into (16) gives

$$\begin{cases}

F_{vl}(z) = \frac{v_{\text{out}}T}{R^2C} \frac{z+1-z^{-1}-z^{-2}}{z^2+(a-X_3/C)z+(X_3/C+a)-az^{-1}-az^{-2}} \\

F_{vg}(z) = \frac{X_2}{C} \frac{z-1}{z^2+(a-X_3/C)z+(X_3/C+a)-az^{-1}-az^{-2}} \\

F_{vr}(z) = \frac{1}{z^2+(a-X_3/C)z+(X_3/C+a)-az^{-1}-az^{-2}}

\end{cases}$$

(17)

This discrete-time closed-loop model reveals the output voltage responses to different signals, i.e., input voltage, reference voltage and load resistance.

# 4.2. Stability Analysis

Substituting  $\{X_1, X_2, X_3\}$  into (17) gives out an explicit form of the closed-loop model, as shown below

$$\begin{cases} F_{vl}(z) = \frac{v_{\text{out}}T}{R^2C} \frac{(1-M)(z+1-z^{-1}-z^{-2})}{(1-M)z^2+a(2-M)z-aM-a(1-M)z^{-1}-a(1-M)z^{-2}} \\ F_{vg}(z) = \frac{aM(2-M)(z-1)}{(1-M)z^2+a(2-M)z-aM-a(1-M)z^{-1}-a(1-M)z^{-2}} \end{cases},$$

$$F_{vr}(z) = \frac{1-M}{(1-M)z^2+a(2-M)z-aM-a(1-M)z^{-1}-a(1-M)z^{-2}}$$

$$(18)$$

where M denotes  $v_{\rm out}/v_{\rm in}$ . Furthermore, the discrete-time responses to input voltage, reference voltage and load are solved by introducing an input of unit step signal z/(z-1), as shown below

$$\begin{cases} h_{l}(z) = F_{vl}(z)z/(z-1) \\ h_{g}(z) = F_{vg}(z)z/(z-1) \\ h_{r}(z) = F_{vr}(z)z/(z-1) \end{cases}$$

(19)

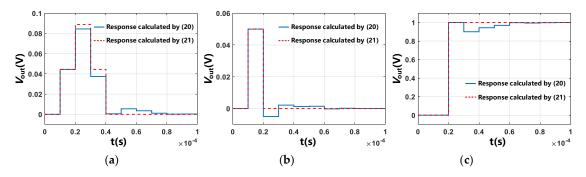

Through synthetic division, the discrete-time responses are derived as (20). Without approximation, (20) provides accurate analyses for different transients. It indicates that the output voltage will stabilize in five switching cycles during an input voltage step, five switching cycle during a reference voltage step, and seven switching cycles during a load step.

$$\begin{cases}

h_l(z) = \frac{v_{\text{out}}T}{R^2C} \left\{ z^{-1} + (2 - a\frac{2-M}{1-M})z^{-2} + (1 - a\frac{4-M}{1-M})z^{-3} + a\frac{-1+2M}{1-M}z^{-4} + a\frac{3-2M}{1-M}z^{-5} + 3az^{-6} + az^{-7} \right\} \\

h_g(z) = a\frac{M(2-M)}{(1-M)} \left\{ z^{-1} - a\frac{2-M}{1-M}z^{-2} + a\frac{M}{1-M}z^{-3} + az^{-4} + az^{-5} \right\} \\

h_r(z) = z^{-2} + (1 - a\frac{2-M}{1-M})z^{-3} + (1 - 2a)z^{-4} + (1 - a)z^{-5} + \sum_{i=6}^{+\infty} z^{-i}

\end{cases}$$

(20)

To reveal the main characteristics of the transients, most items that contains a=T/RC are neglected, since magnitude of T/RC is usually much smaller than unity. Furthermore, the discrete-time transient responses approximate

$$\begin{cases} h_{l}(z) \approx \frac{v_{\text{out}}T}{R^{2}C}(z^{-1} + 2z^{-2} + z^{-3}) \\ h_{g}(z) \approx a \frac{M(2-M)}{(1-M)}z^{-1} \\ h_{r}(z) \approx \sum_{i=2}^{\infty} z^{-i} \end{cases}$$

(21)

Energies **2019**, 12, 3177 9 of 17

Although (21) is less accurate than (20), it reveals the main characteristics of (20). According to (21), when the load steps by a unit, the output voltage deviates by  $2v_{\text{out}}T/R^2C$  maximum, and stabilizes in three switching cycles. When a unity step of input voltage occurs, the output voltage will deviate by aM(2-M)/(1-M) and it lasts for only one switching cycle. When the reference voltage steps, the output voltage tracks it and stabilizes in two switching cycles.

Furthermore, based on specifications in Section 5, different transients are calculated from (20) and (21), respectively. As shown in Figure 7, both approaches derive similar results. Comparatively, (20) is more accurate and it shows details, while (21) reveals the main characteristics of (20). During an unit R step, the output voltage deviates by 0.085 V and re-stabilizes in seven switching cycles. During an unit  $v_{\rm in}$  step, the output voltage deviates by 0.05 V, and re-stabilizes in six switching cycles. During an unit  $v_{\rm ref}$  step, the output voltage tracks  $v_{\rm ref}$  in five switching cycles.

**Figure 7.** Output voltage transient responses to (a) unit R step (b) unit  $v_{in}$  step (c) unit  $v_{ref}$  step.

#### 4.3. Robustness to Deviated Operation Point

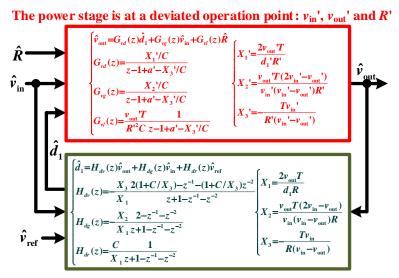

Although the LDCB and DCB controls have the same small signal model at the typical operation point, they are not equivalent when the operation point is deviated. Therefore, the robustness of LDCB controller must be verified with deviations of input voltage, output voltage and load.

Closed-loop small signal model of the system under deviated operation point is given in Figure 8. The LDCB controller is modeled at a fixed operation point of  $\{v_{\rm in}, v_{\rm out}, R\}$ , whereas the main power stage operates at a deviated point of  $\{v_{\rm in}', v_{\rm out}', R'\}$ .

The LDCB controller is at typical operation point:  $v_{in}$ ,  $v_{out}$  and R

Figure 8. Closed-loop small signal model of the system under deviated operation point.

Energies **2019**, 12, 3177 10 of 17

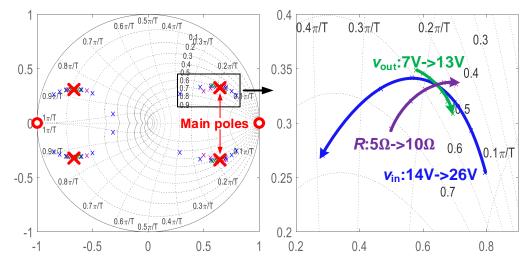

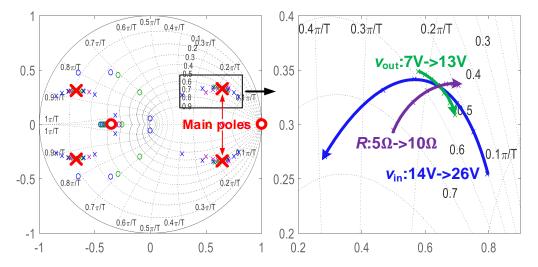

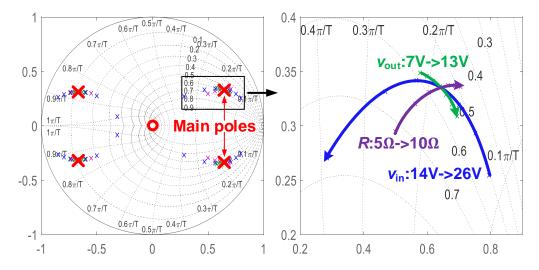

Based on specifications in Section 5, the typical operation point is at  $\{v_{\rm in}=20\,{\rm V},\,v_{\rm out}=10\,{\rm V},\,R=7.5\,\Omega\}$ , and the LDCB controller is derived with this point. However, the power stage can operate at other conditions. Thus, it is modeled with more than  $\pm 30\%$  deviations of operation point, i.e.,  $\{v_{\rm in}'\in[14\,{\rm V},26\,{\rm V}],\,v_{\rm out}'\in[7\,{\rm V},13\,{\rm V}],\,R'\in[5\,\Omega,10\,\Omega]\}$ . The mismatched operation point causes change of the closed-loop model, which is simulated to verify the robustness of LDCB controller. With deviated operation point, zeros and poles of  $F_{vl}(z)$ ,  $F_{vg}(z)$  and  $F_{vr}(z)$  are plotted in Figures 9–11 respectively.

As shown in Figure 9, two main poles of  $F_{vl}(z)$  locate at  $0.639 \pm j0.336$ , which are conjugate and they dominate the output voltage transient response to a load step. When the input voltage increases from 14 V to 26 V, migrations of the main poles indicate a higher bandwidth and damping factor. When the load resistance and output voltage changes by  $\pm 30\%$ , variations of the main poles are relatively small. A zero at z=1 shows that  $F_{vl}(z)\big|_{z=1}=0$ , which indicates zero DC gain to load. Therefore, the output voltage steady state value is not influenced by the load resistance.

Under the same deviations of operation point, zeros and poles of  $F_{vg}(z)$  are given in Figure 10. Migrations of two main poles are exactly the same as those in Figure 9. A zero at z=1 indicates that  $F_{vg}(z)|_{z=1}=0$  or differential characteristic, thus the output voltage steady state value is not influenced by the input voltage.

**Figure 9.** Zeros and poles of  $F_{vl}(z)$ .

**Figure 10.** Zeros and poles of  $F_{vg}(z)$ .

Energies **2019**, 12, 3177 11 of 17

**Figure 11.** Zeros and poles of  $F_{vr}(z)$ .

Zeros and poles of  $F_{vr}(z)$  under the same deviations are given in Figure 11. Migrations of the two main poles are exactly the same as those in Figures 9 and 10. For  $F_{vr}(z)$ , substituting z=1 into (18) gives  $F_{vr}(z)|_{z=1}=1$ , which indicates unity DC gain to the reference voltage. Therefore, the output voltage tracks  $v_{ref}$  at steady state.

All above plots share the same poles, where two main poles indicate that the achieved bandwidth is about  $0.18\pi/T$ . This bandwidth is relatively high for DC-DC applications, and it suggests a transient response time around  $0.35/(0.18\pi/T) \approx 6T$ . This matches with that of the results in Figure 7.

# 4.4. Robustness to Inductance Deviation

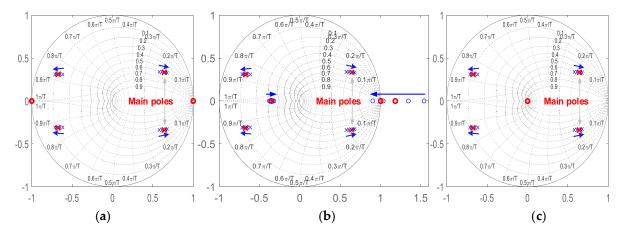

In order to verify the LDCB control robustness to inductance deviation, zero/pole trajectories are simulated when the inductance deviates from 0.8*L* to 1.2*L*, as shown in Figure 12.

**Figure 12.** Zero/pole trajectories when the inductance deviates from 0.8*L* to 1.2*L* (**a**)  $F_{vl}(z)$  (**b**)  $F_{vg}(z)$  (**c**)  $F_{vr}(z)$ .

In all simulated results, the poles remain inside the unit cycle, and the variations are relatively small. This indicates that inductance deviation has minor influences to the output voltage transient responses. For both  $F_{vl}(z)$  and  $F_{vg}(z)$ , the zero at z=1 is not changed, which indicates zero DC gain to load and line voltage. Therefore, with deviated inductance, the output voltage steady state value is still not influenced by load and line voltage. For  $F_{vg}(z)$ , a zero outside the cycle moves inside, which changes the gain at low frequency. However, the influence to line transient is minor, since line transient

Energies **2019**, 12, 3177 12 of 17

is dominated by the main poles. All results prove that LDCB control is capable to maintain the transient performance with inductance deviation of  $\pm$  20%, which is an adequate margin for most inductors.

#### 5. Experimental Results

All analyses and simulations prove the stability and robustness of the converter under LDCB control. The results indicate a fast and stable transient response. In this section, transient performance of the converter is further verified through experiments. A buck converter prototype is constructed as the power stage, and the main specifications are given in Table 2.

| <b>Parameters</b> | Values                                 |  |

|-------------------|----------------------------------------|--|

| L                 | 10 μΗ                                  |  |

| С                 | 40 μF                                  |  |

| $v_{ m in}$       | 20 V                                   |  |

| $v_{ m out}$      | 10 V                                   |  |

| R                 | $7.5 \Omega (5 \Omega \sim 10 \Omega)$ |  |

| T                 | 10 μs                                  |  |

Table 2. Main specifications of the buck converter.

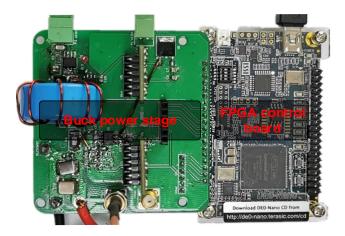

The switching frequency is 100 kHz, and the converter operates at DCM. A photograph of the prototype is shown in Figure 13. The control board adopts a FPGA (Cyclone IV EP4CE22F17C6) to carry out all control algorithms. The input and output voltages are sampled by ADC LTC2314.

Figure 13. The experimental prototype.

In the following, different transients under conventional proportion-integral (PI) control, DCB control and LDCB control are compared. Furthermore, the hardware and calculation lags under different controls are also compared.

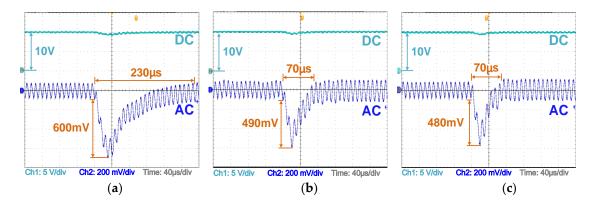

#### 5.1. Output Voltage Transient Responses under Different Controls

The output voltage transient responses to load under different controls are verified when R steps from  $10~\Omega$  to  $5~\Omega$ . According to analyses in Section 4, the output voltage under LDCB control deviates by 0.085~V maximum under a unit R step, and it re-stabilizes in seven switching cycles. Therefore, the output voltage is expected to deviate by -0.43~V maximum when R steps from  $10~\Omega$  to  $5~\Omega$ , and it should re-stabilize in  $70~\mu s$ . The experimental results are given in Figure 14. With PI control, the output voltage deviates by -0.6~V maximum, and it re-stabilizes in  $230~\mu s$ . The DCB and LDCB controls achieve similar transient performance. Under either control, the output voltage re-stabilizes in  $70~\mu s$ , while the maximum deviations are very close. The results match with that of analyses in Section 4.

Energies **2019**, 12, 3177 13 of 17

**Figure 14.** Output voltage transient responses when the load steps from 10  $\Omega$  to 5  $\Omega$  (a) PI control (b) discrete charge balance (DCB) control (c) linearized discrete charge balance (LDCB) control.

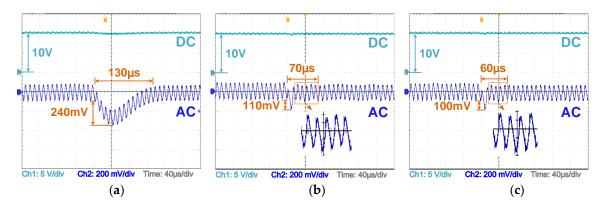

The output voltage transient responses to input voltage under different controls are verified when vg steps from 20 V to 18 V, as shown in Figure 15. With PI control, the output voltage deviates by -0.24 V maximum, and it re-stabilizes in 130  $\mu$ s. Based on analyses in Section 4, the output voltage under LDCB control should deviate by -0.1 V maximum when vin steps from 20 V to 18 V, and it should re-stabilize in 60  $\mu$ s. In the experiment, both DCB and LDCB controllers achieved very small output voltage deviations. The results highly match with that of simulations and analyses. With DCB and LDCB controls, the output voltage returns to 10 V in two switching cycles. After a minor oscillation, it re-stabilizes in 70  $\mu$ s and 60  $\mu$ s, respectively.

**Figure 15.** Output voltage transient responses when the input voltage steps from 20 V to 18 V (a) PI control (b) discrete charge balance (DCB) control (c) linearized discrete charge balance (LDCB) control.

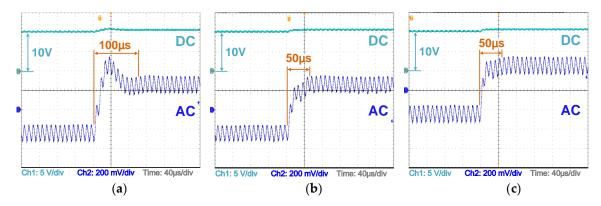

Output voltage transient responses to the reference voltage under different controls are verified when  $v_{\rm ref}$  steps from 10 V to 10.5 V, as shown in Figure 16. With PI control, the output voltage tracks  $v_{\rm ref}$  in 80  $\mu$ s, and an overshoot of 0.2 V, i.e., 40 %, is induced. The DCB and LDCB controllers achieve similar results in this transient. Both output voltages track  $v_{\rm ref}$  in 50  $\mu$ s, and the result matches with that of analyses in Section 4.

Energies **2019**, 12, 3177 14 of 17

**Figure 16.** Output voltage transient responses when the reference voltage steps from 10 V to 10.5 V (a) PI control (b) discrete charge balance (DCB) control (c) linearized discrete charge balance (LDCB) control.

# 5.2. Hardware and Lag Analyses for Different Control Algorithms

Both DCB and LDCB controllers achieve much better transient performance than that of PI controller. Compared with DCB control, advantage of the proposed LDCB controller mainly lies in its simplified algorithm and improved parallelism, which save the hardware cost and reduce the calculation lag. Detailed comparisons of hardware and calculation lags under different controls are given in Table 3. All algorithms have been optimized with the least calculations, and they are based on the same FPGA control board, i.e., Cyclone IV EP4CE22F17C6 (operating at 200 MHz).

| Control Algorithms    | PI      | DCB     | LDCB    |

|-----------------------|---------|---------|---------|

| Adds                  | 3       | 7       | 9       |

| Multiplies            | 2       | 4       | 6       |

| Divisions             | 0       | 2       | 0       |

| Square-roots          | 0       | 1       | 0       |

| Parallel calculations | 1/5     | 4/14    | 12/15   |

| Total logic elements  | 2575    | 4339    | 2964    |

| Total registers       | 1866    | 3109    | 2232    |

| Calculations lag      | 350 ns  | 600 ns  | 275 ns  |

| Sampling lag          | 300 ns  | 300 ns  | 300 ns  |

| Overall lag           | 650 ns  | 900 ns  | 575 ns  |

| Potential $f_{max}$   | 1.5 MHz | 1.1 MHz | 1.7 MHz |

Table 3. Hardware and calculation lags of different control algorithms.

Conventional PI controller induces the minimum calculations, i.e., three adds and two multiplies, which results in the least hardware cost, i.e., 2575 logic elements and 1866 registers. The DCB control algorithm is complicated owing to the division and square root calculations, which lead to the highest hardware cost, i.e., 4339 logic elements and 3109 registers. The LDCB controller requires nine adds and six multiplies, resulting in a medium hardware cost of 2964 logic elements and 2232 registers. Compared with conventional DCB controller, the LDCB controller reduces the hardware cost by 31.7% in logic elements and by 28.2% in registers. Furthermore, although LDCB controller requires 15 calculation elements, i.e., nine adds and six multiplies, 12 of them can be carried out in parallel. The parallelism of LDCB controller results in the least calculation lag of 275 ns, which is even less than that of PI controller. The overall lag is 575 ns, which provides potential for the highest switching frequency of 1.7 MHz.

As a conclusion, the proposed LDCB controller achieves similar transient performance to that of DCB controller. While algorithm of LDCB controller is simplified, resulting in a reduced hardware cost and calculation lag. Furthermore, the reduced lag provides potential for a higher switching frequency under the same hardware speed.

Energies **2019**, 12, 3177 15 of 17

#### 6. Conclusions

This paper presents a LDCB control strategy for DCM buck converter. The control algorithm and scheme are derived through linearizing conventional DCB controller. Since the LDCB controller has the same small signal model as that of DCB controller, it achieves similar control loop bandwidth and transient performance. Furthermore, benefiting from the simplified algorithm and parallel calculations, the LDCB controller provides advantages of a simplified algorithm and a reduced calculation lag. Compared with conventional DCB controller, the hardware cost is greatly reduced, where the logic elements are reduced by 31.7%, and the registers are reduced by 28.2%. Besides, the calculation lag is decreased from 600 ns to 275 ns, which provides potential for a higher switching frequency. The stability under LDCB control is verified by closed-loop analyses, while ±30% deviation of operation point and ±20% deviation of inductance are introduced. In all deviated conditions, migrations of the main poles are relatively small, which prove the robustness of LDCB control. Finally, experimental results shown that the proposed LDCB controller achieves similar transient performance to DCB controller. While compared with conventional PI controller, the LDCB controller reduces the transient response time by more than 50%.

**Author Contributions:** Methodology, Y.S.; supervision, S.C.; validation, D.L.; writing—original draft, R.M.; writing—review & editing, L.L.

Funding: This work was supported by the National Natural Science Foundation of China under Grant 61701184.

Acknowledgments: This work is supported by Huazhong University of Science and Technology.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Tian, S.; Lee, F.C.; Li, Q.; Yan, Y. Unified Equivalent Circuit Model and Optimal Design of V<sup>2</sup> Controlled Buck Converters. *IEEE Trans. Power Electron.* **2016**, *31*, 1734–1744. [CrossRef]

- 2. Liu, P.; Yan, Y.; Mattavelli, P.; Lee, F.C. Digital Constant On-Time V2Control with Hybrid Capacitor Current Ramp Compensation. *IEEE Trans. Power Electron.* **2018**, *33*, 8818–8826. [CrossRef]

- 3. Yan, Y.; Lee, F.C.; Tian, S.; Liu, P. Modeling and Design Optimization of Capacitor Current Ramp Compensated Constant On-Time V^2 Control. *IEEE Trans. Power Electron.* **2018**, *33*, 7288–7296. [CrossRef]

- 4. Caseiro, L.M.A.; Mendes, A.M.S.; Cruz, S.M.A. Cooperative and Dynamically Weighted Model Predictive Control of a 3-Level Uninterruptible Power Supply with Improved Performance and Dynamic Response. *IEEE Trans. Power Electron.* **2019**, 1. [CrossRef]

- Wang, L.; Guo, J.; Xu, C.; Wu, T.; Lin, H. Hybrid Model Predictive Control Strategy of Supercapacitor Energy Storage System Based on Double Active Bridge. *Energies* 2019, 12, 2134. [CrossRef]

- Abdollahi, H.; Arrua, S.; Roinila, T.; Santi, E. A Novel DC Power Distribution System Stabilization Method Based on Adaptive Resonance-Enhanced Voltage Controller. *IEEE Trans. Ind. Electron.* 2019, 66, 5653–5662.

[CrossRef]

- 7. Kim, S.; Ahn, C.K. Self-Tuning Proportional-Type Performance Recovery Property Output Voltage-Tracking Algorithm for DC–DC Boost Converter. *IEEE Trans. Ind. Electron.* **2019**, *66*, 3167–3175. [CrossRef]

- 8. Kang, J.; Park, J.; Jeong, M.; Yoo, C. A Time-Domain-Controlled Current-Mode Buck Converter with Wide Output Voltage Range. *IEEE J. Solid State Circuits* **2019**, *54*, 865–873. [CrossRef]

- 9. Abdelhamid, E.; Bonanno, G.; Corradini, L.; Mattavelli, P.; Agostinelli, M. Stability Properties of the 3-Level Flying Capacitor Buck Converter Under Peak or Valley Current Programmed Control. *IEEE Trans. Power Electron.* **2019**, *34*, 8031–8044. [CrossRef]

- Smithson, S.C.; Williamson, S.S. A Unified State-Space Model of Constant-Frequency Current-Mode-Controlled Power Converters in Continuous Conduction Mode. *IEEE Trans. Ind. Electron.* 2015, 62, 4514–4524. [CrossRef]

- 11. Zhou, M.; Sun, Z.; Low, Q.W.; Siek, L. Multiloop Control for Fast Transient DC–DC Converter. *IEEE Trans. Very Large Scale Integr. Syst.* **2019**, 27, 219–228. [CrossRef]

Energies **2019**, 12, 3177 16 of 17

12. Min, R.; Zhang, Q.; Tong, Q.; Zou, X.; Chen, X.; Liu, Z. Multiloop Minimum Switching Cycle Control Based on Nonaveraged Current Discrete-Time Model for Buck Converter. *IEEE Trans. Power Electron.* **2017**, 32, 3143–3153. [CrossRef]

- 13. Ling, R.; Shu, Z.; Hu, Q.; Song, Y. Second-Order Sliding-Mode Controlled Three-Level Buck DC–DC Converters. *IEEE Trans. Ind. Electron.* **2018**, *65*, 898–906. [CrossRef]

- 14. Zhao, Y.; Qiao, W.; Ha, D. A Sliding-Mode Duty-Ratio Controller for DC/DC Buck Converters with Constant Power Loads. *IEEE Trans. Ind. Appl.* **2014**, *50*, 1448–1458. [CrossRef]

- 15. Jeong, M.; Kang, J.; Park, J.; Yoo, C. A Current-Mode Hysteretic Buck Converter with Multiple-Reset RC-Based Inductor Current Sensor. *IEEE Trans. Ind. Electron.* **2019**, *66*, 8445–8453. [CrossRef]

- 16. Jafarian, M.J.; Nazarzadeh, J. Time-optimal sliding-mode control for multi-quadrant buck converters. *IET Power Electron.* **2011**, *4*, 143–150. [CrossRef]

- 17. Ghasemian, A.; Taheri, A. Constrained Near-Time-Optimal Sliding-Mode Control of Boost Converters Based on Switched Affine Model Analysis. *IEEE Trans. Ind. Electron.* **2018**, *65*, 887–897. [CrossRef]

- 18. Kapat, S.; Shenoy, P.S.; Krein, P.T. Near-Null Response to Large-Signal Transients in an Augmented Buck Converter: A Geometric Approach. *IEEE Trans. Power Electron.* **2012**, 27, 3319–3329. [CrossRef]

- 19. Peretz, M.M.; Mahdavikhah, B.; Prodić, A. Hardware-Efficient Programmable-Deviation Controller for Indirect Energy Transfer DC–DC Converters. *IEEE Trans. Power Electron.* **2015**, *30*, 3376–3388. [CrossRef]

- 20. Meyer, E.; Zhang, Z.; Liu, Y. An Optimal Control Method for Buck ConvertersUsing a Practical Capacitor ChargeBalance Technique. *IEEE Trans. Power Electron.* **2008**, 23, 1802–1812. [CrossRef]

- 21. Meyer, E.; Liu, Y. A Practical Minimum Time Control Method for Buck Converters Based on Capacitor Charge Balance. In Proceedings of the 2008 Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition, Austin, TX, USA, 24–28 February 2008; pp. 10–16.

- 22. Jia, L.; Wang, D.; Liu, Y.; Sen, P.C. A novel analog implementation of capacitor charge balance controller with a practical extreme voltage detector. In Proceedings of the 2011 Twenty-Sixth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX, USA, 6–11 March 2011; pp. 245–252.

- 23. Jia, L.; Liu, Y. Voltage-Based Charge Balance Controller Suitable for Both Digital and Analog Implementations. *IEEE Trans. Power Electron.* **2013**, *28*, 930–944. [CrossRef]

- 24. Jia, L.; Liu, Y. Low Cost Microcontroller Based Implementation of Robust Voltage Based Capacitor Charge Balance Control Algorithm. *IEEE Trans. Ind. Inform.* **2013**, *9*, 869–879. [CrossRef]

- 25. Meyer, E.; Zhang, Z.; Liu, Y. Digital Charge Balance Controller to Improve the Loading/Unloading Transient Response of Buck Converters. *IEEE Trans. Power Electron.* **2012**, 27, 1314–1326. [CrossRef]

- 26. Chen, H.; Chang-Chien, L. Charge Balance Control for Improving the Load Transient Response on Dynamic Voltage Scaling (DVS) Buck Converter. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5.

- 27. Nguyen, H.V.; Huynh, A.H.; Kim, S.; Song, H. Active EMI Reduction Using Chaotic Modulation in a Buck Converter with Relaxed Output LC Filter. *Electronics* **2018**, *7*, 254. [CrossRef]

- 28. Pareschi, F.; Rovatti, R.; Setti, G. EMI Reduction via Spread Spectrum in DC/DC Converters: State of the Art, Optimization, and Tradeoffs. *IEEE Access* **2015**, *3*, 2857–2874. [CrossRef]

- 29. Wang, J.; Xu, J. Peak Current Mode Bifrequency Control Technique for Switching DC–DC Converters in DCM with Fast Transient Response and Low EMI. *IEEE Trans. Power Electron.* **2012**, 27, 1876–1884. [CrossRef]

- 30. Gurbina, M.; Ciresan, A.; Lascu, D.; Lica, S.; Pop-Calimanu, I.M. A New Exact Mathematical Approach for Studying Bifurcation in DCM Operated dc-dc Switching Converters. *Energies* **2018**, *11*, 663. [CrossRef]

- 31. Qiu, Y.; Chen, X.; Liu, H. Digital Average Current-Mode Control Using Current Estimation and Capacitor Charge Balance Principle for DC–DC Converters Operating in DCM. *IEEE Trans. Power Electron.* **2010**, 25, 1537–1545.

- 32. Min, R.; Tong, Q.; Zhang, Q.; Zou, X.; Yu, K.; Liu, Z. Digital Sensorless Current Mode Control Based on Charge Balance Principle and Dual Current Error Compensation for DC–DC Converters in DCM. *IEEE Trans. Ind. Electron.* **2016**, *63*, 155–166. [CrossRef]

Energies **2019**, 12, 3177

33. Zhang, X.; Min, R.; Zhang, D.; Wang, Y. An Optimized Sensorless Charge Balance Controller Based on a Damped Current Model for Flyback Converter Operating in DCM. *Energies* **2018**, *11*, 3478. [CrossRef]

34. Erickson, R.W.; Maksimović, D. *Fundamentals of Power Electronics*, 2nd ed.; Springer-Verlag: New York, NY, USA, 2001; pp. 15–33.

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).