Article

# Structural and Electronic Properties of Polycrystalline InAs Thin Films Deposited on Silicon Dioxide and Glass at Temperatures below 500 °C

Anya Curran <sup>1,2,\*</sup>, Agnieszka Gocalinska <sup>1</sup>, Andrea Pescaglini <sup>1</sup>, Eleonora Secco <sup>1</sup>, Enrica Mura <sup>1</sup>, Kevin Thomas <sup>1</sup>, Roger E. Nagle <sup>1</sup>, Brendan Sheehan <sup>1</sup>, Ian M. Povey <sup>1,2</sup>, Emanuele Pelucchi <sup>1</sup>, Colm O'Dwyer <sup>1,2,3</sup>, Paul K. Hurley <sup>1,2,3</sup> and Farzan Gity <sup>1</sup>

- <sup>1</sup> Tyndall National Institute, Dyke Parade, T12 R5CP Cork, Ireland; agnieszka.gocalinska@tyndall.ie (A.G.); andreapescaglini@gmail.com (A.P.); secco.eleonora@gmail.com (E.S.); enrica.mura@tyndall.ie (E.M.); kevin.thomas@tyndall.ie (K.T.); roger.e.nagle@intel.com (R.E.N.); brendan.sheehan@tyndall.ie (B.S.); ian.povey@tyndall.ie (I.M.P.); emanuele.pelucchi@tyndall.ie (E.P.); c.odwyer@ucc.ie (C.O.); paul.hurley@tyndall.ie (P.K.H.); farzan.gity@tyndall.ie (F.G.)

- School of Chemistry, University College Cork, T12 YN60 Cork, Ireland

- Advanced Materials and BioEngineering Research Centre (AMBER), Trinity College Dublin, D02 PN40 Dublin 2, Ireland

- \* Correspondence: anya.curran@tyndall.ie; Tel.: +353-86-338-3584

**Abstract:** Polycrystalline indium arsenide (poly InAs) thin films grown at 475 °C by metal organic vapor phase epitaxy (MOVPE) are explored as possible candidates for low-temperature-grown semiconducting materials. Structural and transport properties of the films are reported, with electron mobilities of ~100 cm²/V·s achieved at room temperature, and values reaching 155 cm²/V·s for a heterostructure including the polycrystalline InAs film. Test structures fabricated with an aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) top-gate dielectric show that transistor-type behavior is possible when poly InAs films are implemented as the channel material, with maximum  $I_{ON}/I_{OFF} > 250$  achieved at -50 °C and  $I_{ON}/I_{OFF} = 90$  at room temperature. Factors limiting the  $I_{ON}/I_{OFF}$  ratio are investigated and recommendations are made for future implementation of this material.

Keywords: polycrystalline; InAs; thin films

Citation: Curran, A.; Gocalinska, A.; Pescaglini, A.; Secco, E.; Mura, E.; Thomas, K.; Nagle, R.E.; Sheehan, B.; Povey, I.M.; Pelucchi, E.; et al. Structural and Electronic Properties of Polycrystalline InAs Thin Films Deposited on Silicon Dioxide and Glass at Temperatures below 500 °C. Crystals 2021, 11, 160. https://doi.org/10.3390/cryst11020160

Academic Editor: Simona Binetti Received: 11 January 2021 Accepted: 2 February 2021 Published: 5 February 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

Low-temperature-grown (<500 °C) semiconducting materials have garnered much attention in recent years for a number of applications such as display technologies, sensors integrated above integrated circuits (IC), and back-end-of-line integration. For these applications, high-temperature processing may not be compatible with the substrate type or previously deposited layers [1]. During conventional semiconductor device processing, dopant activation is often the highest-temperature step, indicating a need for semiconducting materials which do not require a high-temperature dopant activation step. A number of different materials are being explored for these purposes, including InGaZnO [2], InSnO [3], and 2D materials [4,5]. InAs is known to exhibit a high surface electron density in the absence of any intentional doping. This 2D electron gas on the surface of crystalline InAs has been postulated to originate from In adatoms and adsorption of H adatoms [6]. The 2D electron gas reported for crystalline InAs suggests that polycrystalline InAs may be a potential semiconductor candidate for low-temperature processing. Further to this, if a dopant is required, n- and p-type dopant activation energies in InAs are very low (0.02 eV for Si and 0.01 eV Zn, which are n- and p-type dopants, respectively) [7]. III-V materials have the added benefit of higher carrier velocities than Si: in InAs, electron mobilities are  $\geq$ 40,000 cm<sup>2</sup>/V·s, resulting in the potential to allow for a decrease in the operating voltage without compromising the switching speed [8]. Although a 2D electron gas marks

Crystals **2021**, 11, 160 2 of 11

a departure from traditional transistor physics, functional InAs thin-film transistors have been demonstrated through a process of bonding crystalline InAs to a Si substrate [9,10]. It has been shown that poly InAs can be grown at low temperatures on amorphous substrates (SiO<sub>2</sub> and glass) and, through Zn doping, can achieve p-type mobilities of >5 cm²/ $V \cdot s$ , with no optimization [11]. This is an important consideration if this material is to be implemented in CMOS architectures in the future. In this paper, we investigate the properties of this material system as grown, and whether low-temperature-grown (max temperature <500 °C) poly InAs also exhibits a high electron density on the surface without intentional doping. In addition, transistor test structures utilizing the low-temperature-grown poly InAs as a channel material are fabricated and characterized to assess the suitability of the material system for use as a MOSFET channel material in the future.

#### 2. Materials and Methods

Poly InAs thin films (nominally 10–100 nm thick) were grown by MOVPE (or MOCVD, as it is often referred to) at low pressure (80 mbar) in a commercial horizontal Aixtron 200 reactor with purified N<sub>2</sub> as the carrier gas [12,13], on corning "smartphone-grade" glass and Si/SiO<sub>2</sub> substrates at 475 °C, with In droplets serving as nucleation sites. Different thicknesses were achieved by different growth times, with the growth rate remaining constant. Precursors used were trimethylindium (TMIn) and arsine (AsH<sub>3</sub>). For selected samples, a polycrystalline GaAs buffer layer was added to form GaAs/InAs heterostructures. The same droplet epitaxy technique was employed, using trimethylgallium or triethylgallium (TMGa or TEGa) and arsine (AsH<sub>3</sub>) precursors. For samples containing zinc or phosphorous, diethylzinc (DEZn) or phosphine (PH<sub>3</sub>) precursors were used [11]. Samples were prepared for cross-sectional transmission electron microscopy (XTEM) using a Dual Beam Focused Ion Beam (FIB) FEI Helios NanoLab 600i. Carbon and platinum protective layers were deposited before the lamella was removed and thinned to <200 nm thickness. Transmission electron microscopy (TEM) analysis was performed using a JEOL JEM-2100. Hall effect measurements presented in this paper were performed at room temperature unless otherwise stated and were measured on LakeShore Model 8404 AC/DC Hall effect measurement system. Samples for Hall effect measurements were  $\sim 1 \times 1$  cm<sup>2</sup> and van der Pauw configuration was used. Top-gated transistor test devices were fabricated, utilizing the poly InAs films as their channel material. Patterning of contacts was achieved using photolithography. Source/drain contact metal Au(14 nm):Ge(14 nm):Au(14 nm):Ni(11 nm):Au(200 nm) was deposited by e-beam evaporation and defined using the standard lift-off process. The definition of the channel and source/drain regions was achieved through wet etching using 20:1 C<sub>6</sub>H<sub>8</sub>O<sub>7</sub>:H<sub>2</sub>O<sub>2</sub> (etch rate > 2 nm/s). Surface passivation was achieved using a 10 min dip in 10% (NH<sub>4</sub>)<sub>2</sub>S [14]. Following the surface treatment, 15 nm Al<sub>2</sub>O<sub>3</sub> gate oxide was deposited by atomic layer deposition (ALD) at 300 °C using trimethyl aluminum (TMA) precursor and H<sub>2</sub>O, followed by 200 nm palladium (Pd) gate contact deposited by e-beam evaporation. Electrical characteristics of the devices, both at room temperature and variable temperatures, were extracted using a semiconductor device parameter analyzer, the Agilent B1500, and a semi-automatic Cascade probe station.

# 3. Results

# 3.1. Poly InAs Film Properties

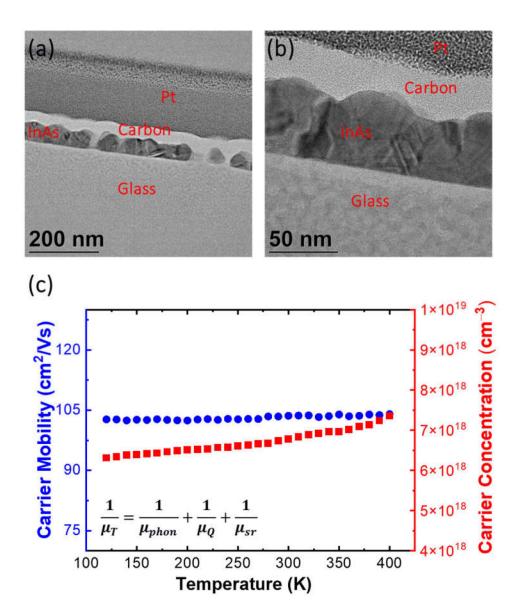

The expected polycrystalline nature of the InAs film was confirmed by XTEM, and energy-dispersive X-ray analysis (EDX) was used to confirm that the composition of the lamella was InAs. Figure 1a shows a cross-section, with a lamella thickness of  $\leq 200$  nm. The poly InAs film appears continuous, with some local areas where the film does not have complete closure, possibly resulting in the difference in contrast seen towards the right-hand side of Figure 1a. The area shown in Figure 1b was used to determine the average thickness of the film deposited. Maximum and minimum thicknesses were 55.5 and 40.9 nm, respectively, with the average thickness determined to be 49.5 nm. The grain size can be determined from the XTEM image and is seen to be in the order of 10s of nanometers.

Crystals **2021**, 11, 160 3 of 11

**Figure 1.** (a,b) Cross-sectional TEM images of polycrystalline InAs film grown at  $475\,^{\circ}$ C directly on a glass substrate. (c) Temperature-dependent Hall effect measurements of a nominally 25 nm poly InAs film on glass (inset: contributions to the overall electron mobility, see text). Measurements taken in AC mode with magnetic field of 0.6 T.

Despite the film not being entirely uniform in the cross-sectional image of the TEM lamella, it was possible to measure an electron mobility of ~100 cm²/V·s at room temperature, suggesting that there are percolation paths present in the 3D geometry. Figure 1c shows the temperature dependence of the carrier mobility and concentration in poly InAs, determined by Hall effect measurements over a temperature range of 125–400 K. As expected, the majority carrier type are electrons, and the carrier mobility in the poly InAs film is seen to be almost independent of temperature. Based on the Matthiessen rule [15], the equation governing the total mobility ( $\mu_T$ ) can be expressed as shown in Figure 1, where the mobility contributions are comprised of: phonon scattering ( $\mu_{phon}$ ), Coulomb interactions ( $\mu_Q$ ), and surface roughness ( $\mu_{sr}$ ). As surface roughness is the only factor of the three which is not strongly temperature-dependent, we can conclude that this is the dominant factor limiting the electron mobility in the poly InAs film [16]. It is well known that the mobility of polycrystalline Si is limited by grain boundary scattering. It is observed that a poly Si film with lower doping shows an increase in mobility with temperature (due to thermionic emission over potential barriers at grain boundaries), while for a poly Si film with higher doping, a decrease

*Crystals* **2021**, *11*, 160 4 of 11

in mobility with temperature (phonon-limited) is shown as the grain boundary defects are saturated and the potential barrier at the grain boundary regions tends to zero [17]. If our unintentionally doped poly InAs behaved in the same way, we would expect the mobility to increase with temperature in the lower temperature range and begin to decrease with temperature at the higher temperature range as the potential barrier is removed and the mobility becomes phonon-limited. However, we do not observe this, as, due to our high electron concentration (and smaller bandgap than Si), the grain boundaries are saturated and the dominant factor limiting the mobility is surface roughness, with the mobility remaining relatively constant over the entire measurement range of temperatures as a result.

Hall effect measurements of films with varying thicknesses (10–100 nm nominal thickness) showed the expected scaling of the sheet carrier concentration with thickness (data shown in Supplementary Materials, Table S1), meaning that there was not exclusively a surface charge present as had been seen in the literature, but also a contribution from a bulk charge in the poly InAs film. Table 1 shows the carrier mobility and concentration results obtained from room-temperature Hall effect measurements performed on differing poly InAs films. The nominally 10 nm InAs film grown directly on glass was not capable of being measured using the Hall effect apparatus, as it lacked sufficient continuity to obtain reliable data. The three other samples in Table 1 showed an increase in mobility and sheet carrier concentration with an increase in poly InAs film thickness.

**Table 1.** Room-temperature Hall effect measurement results of poly InAs films 10 or 25 nm in nominal thickness, with or without prior 25 nm poly GaAs buffer layer, grown on glass. Carrier type for all films was found to be electrons.

|                         | Carrier Mobility (cm <sup>2</sup> /Vs) | Carrier Density (cm <sup>-3</sup> ) | Sheet Carrier Density (cm <sup>-2</sup> ) |

|-------------------------|----------------------------------------|-------------------------------------|-------------------------------------------|

| 25 nm InAs              | 73                                     | $7 \times 10^{18}$                  | $1.75 \times 10^{11}$                     |

| 25 nm GaAs + 10 nm InAs | 29                                     | $9.6 \times 10^{18}$                | $9.6 \times 10^{10}$                      |

| 25 nm GaAs + 25 nm InAs | 155                                    | $8 \times 10^{18}$                  | $2 	imes 10^{11}$                         |

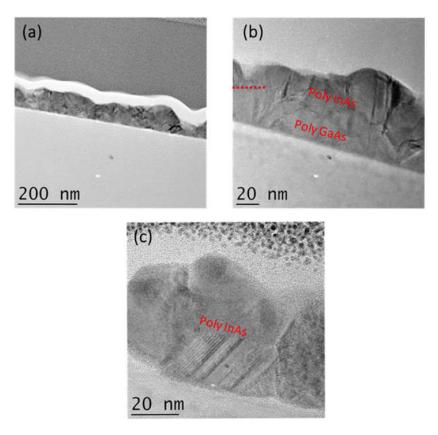

Several efforts were made to increase the electron mobility and improve the uniformity of the poly InAs thin films, with a view to implementation in transistor test devices. The benefits of depositing a polycrystalline GaAs (poly GaAs) layer prior to poly InAs such as minimizing roughness and improving continuity have been discussed elsewhere [11]. These benefits are evident as the mobility and concentration could be determined for the 10 nm InAs layer with a GaAs buffer layer, but not for the sample without. Figure 2 shows XTEM images of a 25 nm poly GaAs + 25 nm poly InAs film on glass, with InAs directly on glass as a comparison. Figure 2a shows greater uniformity than the film shown in Figure 1a, and Figure 2b,c illustrate the difference in the thickness of the poly InAs, despite having the same nominal thickness value. It is noted that a contribution to the carrier concentration and mobility from the 25 nm GaAs buffer layer can be discarded, as this layer measured in isolation yields a carrier concentration of  $1\times10^{16}~\text{cm}^{-3}$  and electron mobility of 0.14 cm<sup>2</sup>/V·s. Secondly, as these films were intended for use in a junctionless transistor architecture [18], there was concern that the carrier concentrations measured in the InAs film  $(10^{18}-1019 \text{ cm}^{-3})$  would be too high to allow full depletion of the InAs channel of the transistor [19]. For this reason, Zn was incorporated as a p-type dopant into the poly InAs film during growth. This Zn incorporation effectively modulated the carrier concentration in the poly InAs thin films by ~three orders of magnitude with no reduction in mobility evident [11]. The observation that the electron mobility was not degraded by additional doping is consistent with a mobility limited by surface roughness.

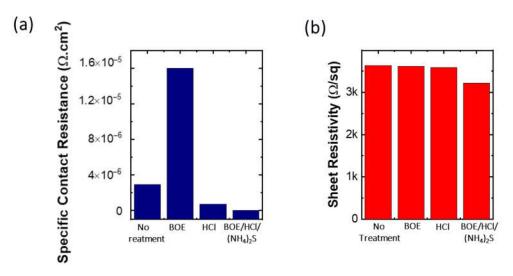

Exposure of the InAs surface to air is expected to result in oxide formation on the surface and subsequent Fermi level pinning, with detrimental effects for contact resistance and gate oxide formation. The effect of a number of surface treatments designed to remove native oxides and/or passivate the poly InAs surface prior to metal contact deposition was studied (Figure 3). Post-treatment properties were extracted from circular transmission line model (cTLM) measurements. Buffered oxide etch (BOE) (which is a mixture of a buffering

Crystals **2021**, 11, 160 5 of 11

agent and HF) caused the specific contact resistance to increase compared to a sample which had received no treatment. HCl treatment achieved a clear improvement in electrical characteristics; however, a combination of BOE/HCl/(NH<sub>4</sub>)<sub>2</sub> S resulted in consistently superior electrical results than those of the sample which received no treatment and the samples which received BOE or HCl treatments in isolation.

**Figure 2.** XTEM images of (a,b) 25 nm poly GaAs + 25 nm poly InAs (dotted line in (b) indicates the position of the interface at the left-hand side of the image) and (c) 25 nm poly InAs on glass.

**Figure 3.** Effect of surface treatments on (a) specific contact resistance and (b) sheet resistivity of nominally 25 nm poly InAs (transfer length measurements shown in Supplementary Materials, Figure S1).

Crystals **2021**, 11, 160 6 of 11

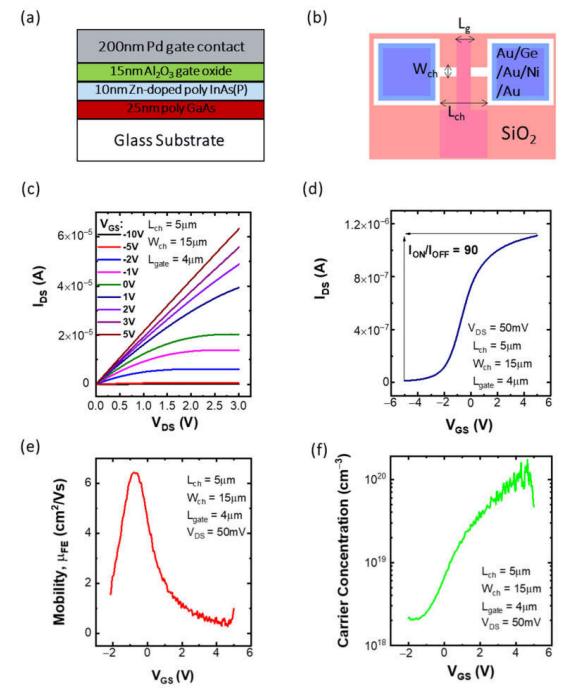

#### 3.2. Transistor Test Structures

Top-gated transistor test devices were fabricated using a heterostructure consisting of 25 nm poly GaAs + 10 nm Zn-doped poly InAs(P) as the channel material. As discussed previously [11], phosphorous was included as a surfactant during the growth process. Based on previous research, 10% (NH<sub>4</sub>)<sub>2</sub>S for 10 min at room temperature was used prior to gate oxide deposition during the top-gated transistor device fabrication [14]. Ammonium sulfide, (NH<sub>4</sub>)<sub>2</sub>S, has been shown to remove InAs surface oxides; however, it can have deleterious effects, damaging the patterns previously etched, and forming an undercut. These effects are mitigated through the sulfurization of the surface by (NH<sub>4</sub>)<sub>2</sub>S itself and dilution of the (NH<sub>4</sub>)<sub>2</sub>S solution before use [20]. For this reason, a 10% (NH<sub>4</sub>)<sub>2</sub>S solution only was used for surface treatment of poly InAs films [12]. Following the etching of the InAs/GaAs to form the active area of the device, and 10% (NH<sub>4</sub>)<sub>2</sub>S surface passivation, the Al<sub>2</sub>O<sub>3</sub> (15 nm) top-gate oxide was formed by ALD. The ALD process is also reported to be effective in reducing or removing native oxides present on the III-V surface [21].

Electrical characterization was performed on the top-gated transistor test devices. Output characteristics, Figure 4c, show classical transistor behavior. Transfer characteristics are shown in Figure 4d. The clockwise hysteresis observed in transfer characteristics (Supplementary Materials, Figure S2) originates from electron trapping and de-trapping in the Al<sub>2</sub>O<sub>3</sub> gate oxide [22]. It is evident that the drain-source current can be modulated using the gate voltage, and  $I_{ON}/I_{OFF}$  of ~90 is achieved. The threshold voltage was determined by extrapolation from the maximum transconductance,  $g_m = \frac{\partial I_{DS}}{\partial V_{GS}}$ , and was found to be -2.16 V.

Carrier mobility and concentration values for this film were measured through Hall effect measurements prior to device processing and were found to be  $18~\rm cm^2/V\cdot s$  and  $7.7\times 10^{15}~\rm cm^{-3}$ , respectively. Field-effect mobility, Figure 4e, peaks at ~7 cm²/V·s, exhibiting a reduction from the Hall mobility as expected for the transistor structure. While the carrier concentration had been effectively controlled through Zn doping, it is noted that the carrier concentration, Figure 4f, is in excess of the  $7.7\times 10^{15}~\rm cm^{-3}$  determined from Hall analysis. This increase in the electron concentration is consistent with the observation from other works that ALD-deposited Al<sub>2</sub>O<sub>3</sub>, prior to any post-deposition annealing, exhibits a net positive fixed oxide charge density for film thickness values in excess of ~5 nm. Based on values previously reported [22], the 15 nm Al<sub>2</sub>O<sub>3</sub> would exhibit an equivalent net positive charge density of ~5.5  $\times 10^{12}~\rm cm^{-2}$  at the InAs/Al<sub>2</sub>O<sub>3</sub> interface. The corresponding electrostatically induced negative charge in the InAs of  $5.5\times 10^{12}~\rm cm^{-2}$  is equivalent to  $5.5\times 10^{18}\rm cm^{-3}$  based on the nominal thickness of 10 nm for the InAs. This is consistent with the levels of channel charge determined for the InAs transistor around the threshold voltage.

While the drain-source current values above the threshold voltage are in good agreement with the Hall mobility value prior to device processing, the off-state current limits the  $I_{ON}/I_{OFF}$  ratio of the device. The origin of the off-state current was investigated by varying the substrate and InAs parameters. MOSFETs with varying InAs thicknesses, substrate types (Si/SiO<sub>2</sub> vs. glass), and absence/presence of the poly GaAs buffer layer were tested to rule out any of these variables as detrimental to the  $I_{ON}/I_{OFF}$  ratio. All samples exhibited comparable gate modulation, hysteresis in transfer characteristics, and a similar  $I_{ON}/I_{OFF}$  value, ruling out the substrate and parasitic conduction through the GaAs buffer layer as the cause of the off-state current (corresponding device characteristics are shown in Supplementary Materials, Figure S3).

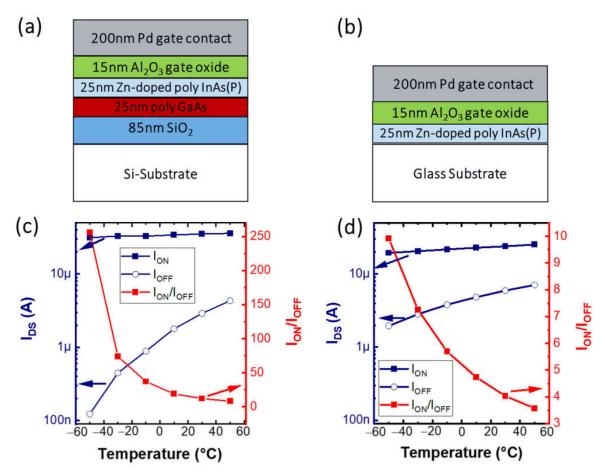

Temperature-dependent current-voltage measurements were performed to gain further understanding of the physical process limiting the  $I_{ON}/I_{OFF}$  ratio. Results are presented for InAs channel MOSFETs on a silicon substrate (Figure 5a) and a glass substrate (Figure 5b), with the corresponding variation in  $I_{ON}$ ,  $I_{OFF}$ , and  $I_{ON}/I_{OFF}$  with device temperature shown in Figure 5c,d. From Figure 5c,d it is noted that the  $I_{ON}/I_{OFF}$  ratio is more strongly temperature-dependent for the sample with a poly GaAs layer than that without, with the highest values for each being >250 and ~10, respectively. When components of the

Crystals **2021**, 11, 160 7 of 11

ratio are separated out, the difference in the final ratio is seen to be due to a lower  $I_{OFF}$  for the sample with a poly GaAs buffer layer, with  $I_{ON}$  for both samples being relatively comparable. One explanation of this is potential Ga incorporation into the poly InAs channel during growth, widening the energy gap and allowing for a lower  $I_{OFF}$  to be achieved. The presence of a low level of Ga in the InAs channel is confirmed through secondary ion mass spectrometry (SIMS) (see Supplementary Materials, Figure S4).

Figure 4. (a) Schematic cross-section of film structure in the channel region of the device where gate oxide  $Al_2O_3$  and gate metal Pd were used. (b) Plan-view of device layout. (c) Device output and (d) transfer characteristics at room temperature. (e) Field-effect mobility, and (f) carrier concentration extracted from transconductance (method in Supplementary Materials). Hall mobility prior to device fabrication =  $18 \text{ cm}^2/\text{V} \cdot \text{s}$ .

Crystals **2021**, 11, 160 8 of 11

**Figure 5.** Schematic structure of (a) sample with GaAs/InAs heterostructure on Si/SiO<sub>2</sub> and (b) sample with InAs directly on glass. (c)  $I_{ON}$ ,  $I_{OFF}$ , and  $I_{ON}/I_{OFF}$  vs. temperature for sample in Figure 6a, (d)  $I_{ON}$ ,  $I_{OFF}$ , and  $I_{ON}/I_{OFF}$  ratio vs. temperature for sample in Figure 6b.  $V_{DS} = 1.5 \text{ V}$ ,  $I_{ON}$  was taken at  $V_{GS} = 5 \text{ V}$ , and  $I_{OFF}$  was taken at  $V_{GS} = -5 \text{ V}$  for Figure 4c,d.

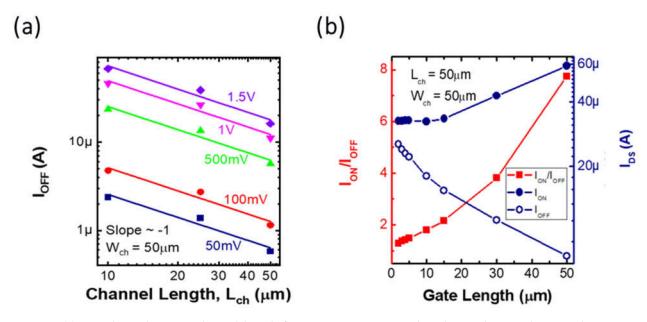

Figure 6. (a)  $I_{OFF}$  dependence on channel length for 25 nm InAs grown directly on glass, with  $V_{DS}$  values next to corresponding line ( $V_{GS} = -5 \text{ V}$ ). (b)  $I_{ON}$ ,  $I_{OFF}$ , and  $I_{ON}/I_{OFF}$  vs. gate length for the same sample ( $V_{DS} = 1 \text{ V}$ ,  $I_{ON} V_{GS} = 5 \text{ V}$ ,  $I_{OFF} V_{GS} = -5 \text{ V}$ ), shown in Figure 5b.

Crystals **2021**, 11, 160 9 of 11

Both of the nominally 25 nm films shown in Figure 5 failed to achieve similarly high room temperature  $I_{ON}/I_{OFF}$  ratios to the 10 nm film shown in Figure 4 (~5–15 for 25 nm films compared to  $\sim\!90$  for 10 nm film). Due to the decrease in  $I_{ON}/I_{OFF}$  with increasing InAs film thickness, the possibility that the channel was not being fully depleted was investigated. If the InAs layer is not fully depleted, this would leave a resistive conduction path at the InAs/glass or InAs/GaAs interface, which is not modulated by the top-gate voltage. Figure 6a shows the I<sub>OFF</sub> dependence on the channel length for the 25 nm InAs sample on glass. The I<sub>OFF</sub> vs. L relationship shows a slope  $\approx -1$ , implying a 1/L relationship which would be expected for a resistor. The same I<sub>OFF</sub> proportional to the 1/L relationship is obtained for the 25 nm In As sample on the GaAs buffer layer. As can be seen from the device architecture shown in Figure 4b, the ratio of gate length to channel length can be varied. Measurements were conducted over a range of gate lengths with a fixed channel length and width to determine how efficiently the gate was controlling the channel. Results from the sample of 25 nm InAs grown directly on glass, shown in Figure 5b, are plotted in Figure 6b below. Figure 6b shows that the greater the proportion of the channel that is gated, the greater the  $I_{ON}/I_{OFF}$  ratio, with both ION and IOFF components being affected. However, when the entirety of the channel is gated, i.e., both  $L_{ch}$  and  $L_{gate} = 50 \mu m$ ,  $I_{OFF}$  is still significantly higher than expected for this film. Due to this, and the fact that neither of the 25 nm films in Figure 5 could achieve the same room temperature  $I_{\mbox{ON}}/I_{\mbox{OFF}}$  ratio as the 10 nm film in Figure 4, it can be concluded that the entirety of the channel is not being depleted. This also explains the resistor-like behavior observed in Figure 6a.

# 4. Discussion

We have shown the ability of low-temperature-grown (<500 °C) poly InAs thin films to achieve remarkable electron mobilities when measured at room temperature ( $\sim 100 \text{ cm}^2/\text{V} \cdot \text{s}$ ), despite appearing non-uniform. The room-temperature Hall electron mobility of 155 cm<sup>2</sup>/V·s achieved for a heterostructure consisting of 25 nm poly GaAs + 25 nm poly InAs grown on glass (Table 1) exceeds the reported Hall mobility values of a number of other low-temperaturegrown thin-film materials, such as polycrystalline silicon [23], Hf-doped In<sub>2</sub> O<sub>3</sub> [24], ITO [25], and ZnO [26,27]. Temperature-dependent Hall effect measurements showed that surface roughness is the dominant factor limiting the electron mobility in the films, which points towards developing a planarization method for poly InAs films. Surface treatments and device processing methods were developed, resulting in functional top-gated transistor test structures. Through temperature-dependent measurements, it was found that IOFF limits the final I<sub>ON</sub>/I<sub>OFF</sub> ratio. Moving forward, it is advised to employ thinner poly InAs films to maximize the performance of this semiconductor channel for applications where the thermal budget is restricted. While the transistor test structures demonstrated in this paper have a relatively low I<sub>ON</sub>/I<sub>OFF</sub>, this marks a significant step towards achieving poly InAs channel MOSFETs grown at a suitable temperature for above IC integration. Finally, it is noted that there is great scope for III-V heterostructure designs which implement these high-mobility, low-temperature-grown poly InAs thin films while being optimized for applications including display technologies, sensors integrated above IC, and back-end-of-line integration.

**Supplementary Materials:** The following are available online at https://www.mdpi.com/2073-435 2/11/2/160/s1, Table S1: Room-temperature Hall effect measurement results for different thicknesses of Zn-doped InAs(P) grown on Si/SiO<sub>2</sub> with 25 nm poly GaAs seed layer. Figure S1: (a) cTLM structure layout from which measurements were taken for Figure 2 in the main paper. (b) Linear IVs from which the parameters in Figure 2 in main paper were extracted. (c) Transfer length, and (d) resistivity results for 25 nm poly InAs film which received each of the surface treatments, and reference sample which received no surface treatment. Figure S2: Clockwise hysteresis observed for transfer characteristics of 10 nm Zn-doped poly InAs(P) with 25 nm poly GaAs seed layer grown on a glass substrate with junctionless transistor device structure. Figure S3: Transfer characteristics of (a) 25 nm Zn-doped InAs(P) with 25 nm poly GaAs seed layer grown on Si/SiO<sub>2</sub> substrate, (b) 25 nm Zn-doped InAs(P) grown directly on glass substrate, and (c) 25 nm Zn-doped InAs(P) grown directly on Si/SiO<sub>2</sub> substrate. Structures through channel region shown below each corresponding to IV.

Crystals **2021**, 11, 160 10 of 11

Figure S4: TOF-SIMS results showing level of (a) Ga, (b) In, and (c) As present vs. depth from surface, for sample consisting of nominally 25 nm poly GaAs buffer layer + 25 nm Zn-doped poly InAs(P).

**Author Contributions:** A.C., lead author, concept, experimental planning, device processing, characterization, analysis; E.S., III-V growth and Hall analysis; A.P., III-V growth; A.G., III-V growth and analysis; E.M., Hall analysis; K.T., III-V growth; R.E.N., structural analysis; B.S., TEM analysis; I.M.P., ALD oxide growth; E.P., concept, design of experiments; C.O., analysis, supervision; P.K.H., analysis, supervision; F.G., concept, experimental planning, device processing, supervision, Hall analysis. All authors have read and agreed to the published version of the manuscript.

**Funding:** The authors acknowledge the Irish Research Council (EPSPG/2017/356) and Science Foundation Ireland (12/RC/2278\_P2, 15/IA/2864, 12/RC/2276, and 12/RC/2276-P2) for financial support of this work.

Institutional Review Board Statement: Not applicable.

**Informed Consent Statement:** Not applicable.

Data Availability Statement: Data available from corresponding author upon reasonable request.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- Datta, S.; Dutta, S.; Grisafe, B.; Smith, J.; Srinivasa, S.; Ye, H. Back-End-of-Line Compatible Transistors for Monolithic 3-D Integration. IEEE Micro 2019, 39, 8–15. [CrossRef]

- 2. Troughton, J.; Atkinson, D. Amorphous InGaZnO and metal oxide semiconductor devices: An overview and current status. *J. Mater. Chem. C* **2019**, *7*, 12388–12414. [CrossRef]

- 3. Kim, C.E.; Yun, I. Device characteristics of Ti–InSnO thin film transistors with modulated double and triple channel structures. *Thin Solid Films* **2013**, *537*, 275–278. [CrossRef]

- 4. Yang, R.; Li, H.; Smithe, K.K.H.; Kim, T.R.; Okabe, K.; Pop, E.; Fan, J.A.; Wong, H.P. 2D molybdenum disulfide (MoS<sub>2</sub>) transistors driving RRAMs with 1T1R configuration. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 19.5.1–19.5.4. [CrossRef]

- 5. Zheng, J.; Yan, X.; Lu, Z.; Qiu, H.; Zhou, X.; Wang, P.; Pan, X.; Liu, K.; Jiao, L. High-Mobility Multilayered MoS<sub>2</sub> Flakes with Low Contact Resistance Grown by Chemical Vapor Deposition. *Adv. Mater.* **2017**, 29, 1604540. [CrossRef]

- 6. Weber, J.R.; Janotti, A.; Van de Walle, C.G. Intrinsic and extrinsic causes of electron accumulation layers on InAs surfaces. *Appl. Phys. Lett.* **2010**, *97*, 192106. [CrossRef]

- 7. Guseva, M.I.; Zotova, N.V.; Koval, A.V.; Nasledov, D.N. Behavior of Group IV Elements Introduced into Indium Arsenide by Ion Implantation. 1974. Available online: https://www.osti.gov/biblio/4274586 (accessed on 16 December 2020).

- 8. Del Alamo, J.A. Nanometre-scale electronics with III–V compound semiconductors. *Nature* 2011, 479, 317. [CrossRef]

- 9. Takei, K.; Kapadia, R.; Fang, H.; Plis, E.; Krishna, S.; Javey, A. High quality interfaces of InAs-on-insulator field-effect transistors with ZrO<sub>2</sub> gate dielectrics. *Appl. Phys. Lett.* **2013**, *102*, 153513. [CrossRef]

- Kim, S.; Yokoyama, M.; Nakane, R.; Ichikawa, O.; Osada, T.; Hata, M.; Takenaka, M.; Takagi, S. High Performance Tri-Gate Extremely Thin-Body InAs-On-Insulator MOSFETs With High Short Channel Effect Immunity and V<sub>th</sub> Tunability. *IEEE Trans. Electron. Devices* 2014, 61, 1354–1360. [CrossRef]

- 11. Gocalinska, A.; Pescaglini, A.; Secco, E.; Mura, E.; Thomas, K.; Curran, A.; Gity, F.; Nagle, R.; Schmidt, M.; Michałowski, P.P.; et al. Next generation low temperature polycrystalline materials for above IC electronics. High mobility n- and p-type III-V MOVPE thin films on amorphous substrates. *J. Phys. Photonics* **2020**, *2*, 025003. [CrossRef]

- Dimastrodonato, V.; Mereni, L.O.; Young, R.J.; Pelucchi, E. AlGaAs/GaAs/AlGaAs quantum wells as a sensitive tool for the MOVPE reactor environment. J. Cryst. Growth 2010, 312, 3057–3062. [CrossRef]

- 13. Thompson, A.G. MOCVD technology for semiconductors. Mater. Lett. 1997, 30, 255–263. [CrossRef]

- 14. O'Connor, É.; Brennan, B.; Djara, V.; Cherkaoui, K.; Monaghan, S.; Newcomb, S.B.; Contreras, R.; Milojevic, M.; Hughes, G.; Pemble, M.E.; et al. A systematic study of (NH<sub>4</sub>)<sub>2</sub>S passivation (22%, 10%, 5%, or 1%) on the interface properties of the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP system for n-type and p-type In<sub>0.53</sub>Ga<sub>0.47</sub>As epitaxial layers. *J. Appl. Phys.* **2011**, *109*, 024101. [CrossRef]

- 15. Matthiessen, A.; Vogt, C., IV. On the influence of temperature on the electric conducting-power of alloys. *Philos. Trans. R. Soc. Lond.* **1864**, *154*, 167–200. [CrossRef]

- 16. Ando, T.; Fowler, A.B.; Stern, F. Electronic properties of two-dimensional systems. Rev. Mod. Phys. 1982, 54, 437–672. [CrossRef]

- 17. Seto, J.Y.W. The electrical properties of polycrystalline silicon films. J. Appl. Phys. 1975, 46, 5247–5254. [CrossRef]

- 18. Colinge, J.-P.; Lee, C.-W.; Afzalian, A.; Akhavan, N.D.; Yan, R.; Ferain, I.; Razavi, P.; O'Neill, B.; Blake, A.; White, M.; et al. Nanowire transistors without junctions. *Nat. Nanotechnol.* **2010**, *5*, 225–229. [CrossRef]

- 19. Colinge, J.P.; Kranti, A.; Yan, R.; Lee, C.W.; Ferain, I.; Yu, R.; Akhavan, N.D.; Razavi, P. Junctionless Nanowire Transistor (JNT): Properties and design guidelines. *Solid State Electron.* **2011**, 65–66, 33–37. [CrossRef]

Crystals **2021**, 11, 160 11 of 11

20. Gin, A.; Wei, Y.; Hood, A.; Bajowala, A.; Yazdanpanah, V.; Razeghi, M.; Tidrow, M. Ammonium sulfide passivation of Type-II InAs/GaSb superlattice photodiodes. *Appl. Phys. Lett.* **2004**, *84*, 2037–2039. [CrossRef]

- 21. Monaghan, S.; O'Mahony, A.; Cherkaoui, K.; O'Connor, É.; Povey, I.M.; Nolan, M.G.; O'Connell, D.; Pemble, M.E.; Hurley, P.K.; Provenzano, G.; et al. Electrical analysis of three-stage passivated In<sub>0.53</sub>Ga<sub>0.47</sub>As capacitors with varying HfO<sub>2</sub> thicknesses and incorporating an Al<sub>2</sub>O<sub>3</sub> interface control layer. *J. Vac. Sci. Technol. B* **2011**, *29*, 01A807. [CrossRef]

- 22. Lin, J.; Gomeniuk, Y.Y.; Monaghan, S.; Povey, I.M.; Cherkaoui, K.; O'Connor, É.; Power, M.; Hurley, P.K. An investigation of capacitance-voltage hysteresis in metal/high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor capacitors. *J. Appl. Phys.* **2013**, *114*, 144105. [CrossRef]

- 23. Lee, S.-H.; Jung, J.-S.; Lee, S.-S.; Lee, S.-B.; Hwang, N.-M. Low temperature deposition of polycrystalline silicon thin films on a flexible polymer substrate by hot wire chemical vapor deposition. *J. Cryst. Growth* **2016**, 453, 151–157. [CrossRef]

- 24. Wang, G.H.; Shi, C.Y.; Zhao, L.; Diao, H.W.; Wang, W.J. Transparent conductive Hf-doped In<sub>2</sub>O<sub>3</sub> thin films by RF sputtering technique at low temperature annealing. *Appl. Surf. Sci.* **2017**, 399, 716–720. [CrossRef]

- 25. Ban, S.-G.; Kim, K.-T.; Choi, B.-D.; Jo, J.-W.; Kim, Y.-H.; Facchetti, A.; Kim, M.-G.; Park, S.-K. Low-Temperature Postfunctionalization of Highly Conductive Oxide Thin-Films toward Solution-Based Large-Scale Electronics. *ACS Appl. Mater. Interfaces* **2017**, *9*, 26191–26200. [CrossRef]

- 26. Tsankonas, C.; Kuznetsov, V.L.; Cranton, W.M.; Kalfagiannis, N.; Abusabee, K.M.; Koutsogeorgis, D.C.; Abeywickrama, N.; Edwards, P.P. Low temperature sputter-deposited ZnO films with enhanced Hall mobility using excimer laser post-processing. *J. Phys. D Appl. Phys.* **2017**, *50*, 485306. [CrossRef]

- Mahdhi, H.; Djessas, K.; Ayadi, Z.B. Synthesis and characteristics of Ca-doped ZnO thin films by rf magnetron sputtering at low temperature. *Mater. Lett.* 2018, 214, 10–14. [CrossRef]