MDPI

Article

# A Theoretical Modeling of Adaptive Mixed CNT Bundles for High-Speed VLSI Interconnect Design

Abu Bony Amin <sup>1,\*</sup>, Syed Muhammad Shakil <sup>2</sup> and Muhammad Sana Ullah <sup>2</sup>

- Department of Electrical and Computer Engineering, University of Massachusetts Amherst (UMass), 100 Natural Resources Road, Amherst, MA 01003, USA

- Department of Electrical and Computer Engineering, Florida Polytechnic University, 4700 Research Way, Lakeland, FL 33805, USA; sshakil2152@floridapoly.edu (S.M.S.); mullah@floridapoly.edu (M.S.U.)

- \* Correspondence: abonyamin5908@floridapoly.edu

**Abstract:** The aroused quest to reduce the delay at the interconnect level is the main urge of this paper, so as to come across a configuration of carbon nanotube (CNT) bundles, namely, squarely packed bundles of mixed CNTs. The demonstrated approach in this paper makes the mixed CNT bundle adaptable to adopt for high-speed very-large-scale integration (VLSI) interconnects with technology shrinkage. To reduce the delay of the proposed configuration of the mixed CNT bundle, the behavioral change of resistance (*R*), inductance (*L*), and capacitance (*C*) has been observed with respect to both the width of the bundle and the diameter of the CNTs in the bundle. Consequently, the performance of the modified bundle configuration is compared with a previously developed configuration, namely, squarely packed bundles of dimorphic MWCNTs in terms of propagation delay and crosstalk delay at local-, semiglobal-, and global-level interconnects. The proposed bundle configuration is, ultimately, enacted as the better one for 32-nm and 16-nm technology nodes, and is suitable for 7-nm nodes as well.

Keywords: mixed CNT bundle; crosstalk delay; interconnect; propagation delay; RLC model

Citation: Amin, A.B.; Shakil, S.M.; Ullah, M.S. A Theoretical Modeling of Adaptive Mixed CNT Bundles for High-Speed VLSI Interconnect Design. *Crystals* **2022**, *12*, 186. https://doi.org/10.3390/ cryst12020186

Academic Editors: Walid M. Daoush, Fawad Inam, Mostafa Ghasemi Baboli and Maha M. Khayyat

Received: 14 November 2021 Accepted: 24 January 2022 Published: 27 January 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

#### 1. Introduction

The overwhelming exploitation of interconnects to the device delay makes researchers weigh Carbon Nanotubes (CNTs) for the possession pertinent to long mean free path [1], electrical properties [1,2], thermal properties [2,3], electromigration, and current density [4]. Moreover, crosstalk delay is a potential stymie for CNTs due to capacitive coupling between adjacent bundles [5]. While it is brought up, in previous literature [1], that the performance will be meliorated with further technology scaling, CNTs can render much better performance based on the exploration of some features.

It is claimed in [5,6] that mutual inductance does not have a considerable impact on crosstalk-induced delay and glitches; instead, coupling capacitance with electrostatic and quantum capacitance makes the main contribution. It is also noticed in [7] that the graphitized electron beam-induced deposition (EBID) carbon has the capability to produce a low-resistance ohmic contact to multiple shells of MWCNT, in the context of making high-performance electrical interconnect structures for next-generation electronic circuits. Although the densely packed configuration of bundled CNTs is seizing attention for improving performance, a trade-off between propagation delay and crosstalk delay is conspicuous [8]. Having noticed, from earlier work [5], that SWCNT and DWCNT shows poorer performance than Cu-based interconnects, owing to higher coupling capacitances, we endeavored to avoid putting any SWCNTs and DWCNTs on the edge of the bundle in our configuration.

To improve the crosstalk delay along with propagation delay, some works [6,9–12] are conducted by introducing different bundle configurations and by combining both MWCNT and SWCNT in the bundle. Rai et al. claimed that the structure with MWCNTs surrounded

Crystals **2022**, 12, 186 2 of 14

by SWCNTs yields better performance by considering the tunnelling and intershell coupling between adjacent shells by depicting four different structures in [10]. The same group, subsequently, showed that the structure with SWCNTs and MWCNTs possessing equal halves vertically was the best one in terms of frequency noise amplitude by delineating the same four structures in another work [11]. However, it is demonstrated in [6,9] that, by varying the relative position of MWCNTs and SWCNTs in the bundle, CNTs with spatial distribution, putting the SWCNTs entirely wrapped up by the MWCNTs in the bundle, indulges lower crosstalk delay than those with random arrangements. A delay-efficient configuration of a mixed bundle is proposed in [12] as well, though the crosstalk delay performance of this configuration is not well-proved since this work opposes the fact, mentioned in [6,9], that SWCNTs are mounted over the boundary of the bundle.

The aim of this paper is to present an innovative diameter-controlled configuration to alleviate the propagation delay and crosstalk delay of size shrinking interconnects, which is feasible from the fabrication aspect. This configuration is presented here with a detailed theoretical and mathematical model analysis and comparison results to assure better enquiries of its performance and enlighten its advantages. To analyze the delay performance, the analytical delay model has been obtained using the parameters from previous works [13–16].

The rest of this paper is organized in the following manner. A modified configuration of a mixed CNT bundle is proposed and illustrated in Section 2. Section 3 is used to develop the mathematical models for *RLC* elements for isolated CNTs, and eventually for a mixed bundle based on the configuration introduced in Section 2. Section 4 is dedicated to the interest of simulating and analyzing the performance indicators, propagation delay, and crosstalk noise for different technology nodes, and depicting a graphical comparison with the previously well-developed research work [17,18]. Section 5 comes up with the conclusion by appending the future work potentialities and improvements.

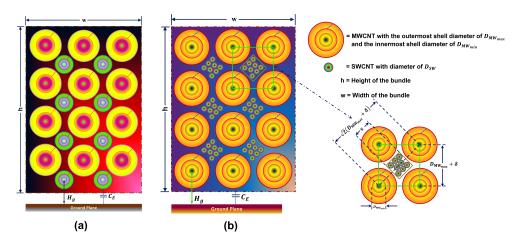

## 2. Modified Mixed CNT Bundle Configuration

Our endeavor in this paper is to enhance the performance by altering the configuration, shown in Figure 1a. In this newly introduced configuration, illustrated in Figure 1b, the replacement of smaller MWCNTs takes place with a bunch of SWCNTs, which are wrapped up by the larger MWCNTs. This modified approach is a virtue of increasing the number of CNTs in the bundle so that we can fill up the unoccupied space with SWCNTs more efficiently and densely. The spacing between shells of MWCNTs and adjacent CNTs, equivalent to the van der Waals distance ( $\delta \approx 0.34$  nm) between graphene layers in graphite, is maintained concurrently [19,20].

**Figure 1.** (*a*,*b*) In both architectures, the size of the larger MWCNTs are the same. The main modification happened in the introduced configuration by means of smaller MWCNTs replaced by a bunch of SWCNTs with the same predefined diameter, according to the space available based on the technology nodes.

Crystals 2022, 12, 186 3 of 14

The proposed configuration is inspired by the geometric pattern previously proposed in the works [17,21], to accommodate a greater number of CNTs in the bundle. In addition to every four larger MWCNTs forming a square by taking the vertices of the square in the center of those MWCNTs, another square forms in the center of the square. A certain number of SWCNTs is accommodated in this newly formed square, which will follow the hexagonally packed pattern. The number of larger MWCNTs and the number of SWCNTs in the bundle are calculated using Equation (1).

By considering one-third of the shells of the MWCNTs as metallic [22], the average number of conducting channels for a shell can be calculated by:

$$N_{\rm c}(i) \approx \begin{cases} \alpha T D_i + \beta & \text{if } D_i > \frac{D_{\rm T}}{T}; \\ \frac{2}{3} & \text{if } D_i \leq \frac{D_{\rm T}}{T}; \end{cases}$$

(1)

where  $\alpha = 2.04 \times 10^{-4} \text{ nm}^{-1} \text{K}^{-1}$ ,  $\beta = 0.425$ ,  $D_{\text{T}} = 1300 \text{ nm} \cdot \text{K}$ , and  $D_i$  is the diameter of the *i*th shell of the MWCNT.

To assure the simplicity of the calculation and to show the relation among all parameters, we are going to pursue further by considering a constant 'a', which is the side of the square formed by the MWCNTs in Figure 1. Thus, the diameter of the outermost shell of the MWCNT is:

$$D_{\rm MW_{\rm max}} = a - \delta. \tag{2}$$

The number of shells of MWCNTs can be calculated using the following Formula (3), according to [9,12,23]:

$$n = \left\lceil \frac{D_{\text{MW}_{\text{max}}} - D_{\text{MW}_{\text{min}}}}{2\delta} \right\rceil. \tag{3}$$

According to the geometry of circle, we know that the diagonal of the bigger square from Figure 1 is  $\sqrt{2}a$ . Hence, we may calculate the side (*s*) of the smaller square from Figure 1 by:

$$s = \sqrt{2}a - (a+\delta) = \left(\sqrt{2} - 1\right)a - \delta. \tag{4}$$

To calculate the plausible number of accommodated SWCNTs in the smaller square of Figure 1:

$$N_{\rm SW} = \left(N_{\rm SW_H} N_{\rm SW_V} - \left\lfloor \frac{N_{\rm SW_V}}{2} \right\rfloor\right) \tag{5}$$

where

$$N_{\text{SW}_{\text{H}}} = \left[\frac{s - D_{\text{SW}}}{D_{\text{SW}} + \delta}\right]$$

; and  $N_{\text{SW}_{\text{V}}} = \left[\frac{2(s - D_{\text{SW}})}{\sqrt{3}(D_{\text{SW}} + \delta)}\right]$ .

The number of MWCNTs in Figure 1 is, thus:

$$N_{\rm MW_h} = \left[ \frac{w - D_{\rm MW_{max}}}{D_{\rm MW_{max}} + \delta} \right] \tag{6}$$

$$N_{\rm MW_{\rm v}} = \left[ \frac{h - D_{\rm MW_{\rm max}}}{D_{\rm MW_{\rm max}} + \delta} \right],\tag{7}$$

where  $\lfloor X \rfloor$  and  $\lceil X \rceil$  signifies that each element of X has been rounded to the nearest integer less than or equal to that element, and to more than or equal to that element, respectively.

The number of smaller squares ( $N_{Sq}$ ) in Figure 1 can be estimated by the following expression:

$$N_{\rm Sq} = (N_{\rm MW_h} - 1)(N_{\rm MW_v} - 1). \tag{8}$$

Crystals 2022, 12, 186 4 of 14

The total number of SWCNTs in the bundle is given here:

$$N_{\rm SW_{\Sigma}} = N_{\rm Sq} N_{\rm SW}. \tag{9}$$

## 3. Improved Mathematical Models

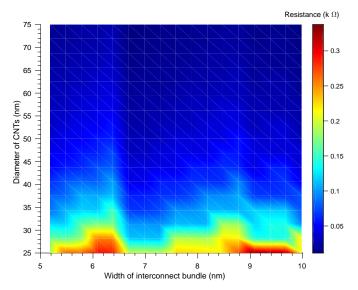

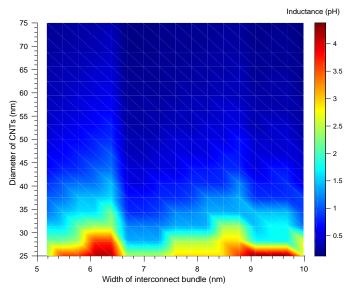

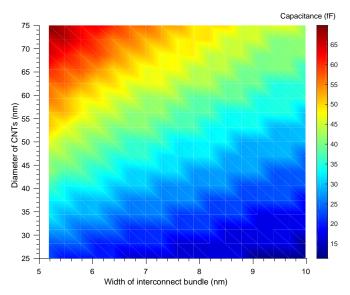

After obtaining the total number of CNTs (both MWCNT and SWCNT) from Section 2, we develop and extract the diameter-controlled RLC elements for the mixed bundle of dimorphic CNTs at different technology nodes in this section. In Figures 2–4, the diameter of the MWCNTs is yielded as a function of 'a', the diameter of SWCNTs is presumed to be the constant value of 1 nm, and the length of the interconnect and aspect ratio are considered as 100  $\mu$ m and 2, respectively.

### 3.1. Resistance in Mixed CNT Bundle

The mathematical approach to determine the equivalent resistance of the mixed bundle is the extraction of the resistance components for isolated CNTs and, eventually, the total resistance of the bundle. To pursue the calculation, we will consider the equivalent single-conductor (ESC) model, where the resistance of the shells of the MWCNTs are in parallel, and adjacent CNTs are also in parallel [24]. According to [25], the quantum resistance ( $R_q$ ) of SWCNTs can be estimated using the conductance  $G = \left(\frac{2e^2}{\hbar}\right)MT$ , where e is the electron charge with the value of  $1.62 \times 10^{-19}$  C, and  $\hbar = 6.6262 \times 10^{-34}$  Js is the Planck constant:

$$R_q = \frac{\hbar}{4\rho^2} \approx 6.45 \,\mathrm{k}\Omega. \tag{10}$$

On the other hand, in the case of a single-wall nanotube length (l) exceeding the mean free path of electrons ( $\lambda_{SWCNT}$ ), another resistance ( $R_s$ ) comes up along with the former one, owing to scattering, which can be computed from the following expression:

$$R_{s} = \frac{\hbar}{4e^{2}} \left( \frac{1}{\lambda_{\text{SWCNT}}} \right). \tag{11}$$

Finally, the total resistance, emerging from the previous two components of the resistance, for an isolated SWCNT, is denoted by (12):

$$R_{\text{SWCNT}} = \begin{cases} R_{\text{c}} + R_{\text{q}} & \text{if } l << \lambda_{\text{CNT}}; \\ R_{\text{c}} + R_{\text{q}} + lR_{\text{s}} & \text{if } l \ge \lambda_{\text{CNT}}; \end{cases}$$

(12)

The lump resistance ( $R_{lump}$ ), having the quantum or intrinsic resistance from Equation (10), caused by the quantum detainment of electrons in a nano-wire and imperfect metal–nanotube contact resistance ( $R_c$ ), may vary from a few to several hundreds of kilo-ohms, based on the fabrication process [9,12,26]. The lump resistance for different isolated MWCNTs of the proposed bundle configuration using (13) has been acquired from [4,9,23,24,26,27]:

$$R_{\text{lump}} = \left[ \sum_{i=1}^{n} \left( \frac{R_{\text{q}}}{N_{\text{c}}(i)} + R_{\text{c}} \right)^{-1} \right]^{-1}.$$

(13)

The per-unit length (p.u.l) scattering resistance ( $R_s$ ) emerges for the length of the nanowire surpassing the effective mean free path of the electron [24]. The scattering resistance ( $R_s$ ) for different isolated MWCNTs of the proposed bundle configuration is estimated from Equation (14), based on [4,9,26]:

$$R_{\rm s} = \sum_{i=1}^{n} \frac{R_{\rm q}}{N_{\rm c}(i)\lambda_i}.$$

(14)

Crystals 2022, 12, 186 5 of 14

The equivalent resistance of the bundle including both MWCNTs and SWCNTs can be reckoned by the following expression:

$$R_{\text{bundle}} = \left[ \left( \frac{R_{\text{q}}}{N_{\text{MW}}} + l \frac{R_{\text{s}}}{N_{\text{MW}}} \right)^{-1} + \frac{R_{\text{SW}}}{N_{\text{SW}_{\Sigma}}} \right]^{-1}. \tag{15}$$

The characteristics of resistance (R) depend on both the width of the interconnect wire based on the technology node and the diameter of the used CNTs in the bundle. The simultaneous impact of both factors is observed in Figure 2. It is obvious that the lower resistance for the bundle is attainable by increasing the width of the bundle along with the diameter of the CNTs. Since it is taken into account that all the CNTs in the bundle are in parallel with each other, the increased number of CNTs can be obtained by increasing the width in a given space of the bundle, and can reduce the resistance significantly. Moreover, the increased diameter of the MWCNTs increases the number of shells, which are also in parallel to each other.

**Figure 2.** Synchronal variation of resistance of the squarely packed bundle of mixed CNTs from altering the width of the bundle and the diameter of the CNTs.

### 3.2. Inductance in Mixed CNT Bundle

To determine the overall inductance for our proposed configuration of the mixed bundle, we will first calculate the inductance for isolated SWCNT and then for the isolated MWCNT, and finally, the equivalent inductance for the entire bundle will be demonstrated, as given in Equation (20). The inductance of the SWCNT consists of two components, which are denoted as kinetic inductance ( $L_k$ ) and magnetic inductance ( $L_m$ ). Considering the ballistic conduction for a 1D conductor, the kinetic inductance ( $L_k$ ) can be obtained by:

$$L_{\mathbf{k}} = \frac{\hbar}{2e^2 v_{\mathbf{F}}},\tag{16}$$

where  $v_{\rm F}$  is the Fermi velocity of an electron with the value of approximately  $8 \times 10^5 \, {\rm ms}^{-1}$ . Since  $L_{\rm k}$  is the function of some constant values, the approximate per-unit length (p.u.l.) value is 16 nH/µm [28]. On the other hand, the stored energy of carriers in a magnetic field engenders magnetic inductance ( $L_m$ ) in SWCNTs [28] which is approximated by:

$$L_{\rm m} = \frac{\mu_0}{2\pi} \ln\left(\frac{y}{d}\right),\tag{17}$$

Crystals **2022**, 12, 186 6 of 14

with  $\mu_0 = 4\pi \times 10^{-7}$  Hm<sup>-1</sup>. Now, in the case of MWCNTs, the magnetic inductance for the *i*th shell can be approximated by the following expression:

$$L_{\mathrm{m_{MW}}}(i) = \frac{\mu_0}{2\pi} \cosh\left(\frac{2h}{D_{\mathrm{MW}}(i)}\right), \ \{i \in \mathbb{N} : 1 \le i \le n\}. \tag{18}$$

The magnetic and kinetic inductance of the isolated MWCNT in the proposed bundle is calculated using Equations (18) and (19), respectively:

$$L_{k_{MW}}(i) = \sum_{i=1}^{n} \frac{L_k}{2N_c(i)}.$$

(19)

Finally, the overall equivalent inductance of the bundle is estimated in (20), which indicates that the kinetic inductance component of SWCNT exists when the length of the interconnect wire exceeds the electron mean free path:

$$L_{\text{bundle}} = \begin{cases} \left(\frac{N_{\text{MW}}}{L_{\text{m}_{\text{MW}}} + L_{\text{k}_{\text{MW}}}} + \frac{N_{\text{SW}_{\Sigma}}}{L_{\text{m}_{\text{SW}}} + L_{\text{k}_{\text{SW}}}}\right)^{-1} & \text{if } l \leq \lambda_{\text{CNT}};\\ \left(\frac{N_{\text{MW}}}{L_{\text{m}_{\text{MW}}} + L_{\text{k}_{\text{MW}}}} + \frac{N_{\text{SW}_{\Sigma}}}{L_{\text{m}_{\text{SW}}}}\right)^{-1} & \text{if } l > \lambda_{\text{CNT}}; \end{cases}$$

(20)

The inductance of the bundle also exhibits the same phenomena as the resistance does. The behavioral change of the inductance of the bundle, with the width and diameter of the CNTs in the bundle, is depicted in Figure 3. Based on the attained diameter, we estimate the delay of the bundle in Section 4.

**Figure 3.** Concurrent extraction of inductance of the squarely packed bundle of mixed CNTs by varying the width of the bundle and the diameter of the CNTs.

## 3.3. Capacitance in Mixed CNT Bundle

The p.u.l. quantum capacitance for a CNT is estimated in Equation (21) by taking the analogy of the required energy to enclose an extra electron at an acquirable quantum state level beyond the Fermi energy level and effective capacitance. This capacitance comes into notification due to the quantum electrostatic energy stored in the nanotube while carrying the current [28]:

$$C_{\rm q} = \frac{2e^2}{\hbar v_{\rm F}} \approx 0.1 \text{ fF/}\mu\text{m}. \tag{21}$$

Crystals 2022, 12, 186 7 of 14

It has already been mentioned that, to estimate the inductance for a isolated SWCNT, that SWCNT must have four conducting channels, and these channels should form a parallel combination [28]. As a result, the equivalent effective quantum capacitance of an isolated SWCNT can be approximated here:

$$C_{\rm SW} = 4C_{\rm q} \approx 0.4 \, \rm fF/\mu m. \tag{22}$$

The electrostatic capacitance is expressed in the following expression by considering the SWCNT as a thin wire with the diameter  $D_{SW}$  putting, at a distance of 'y', away from the ground [28]:

$$C_{\rm e}(SWCNT) = \frac{2\pi\epsilon_0\epsilon_r}{\cosh^{-1}\left(\frac{y}{D_{\rm SW}}\right)},\tag{23}$$

with absolute dielectric permittivity ( $\epsilon_0$ ) = 8.854 × 10<sup>-12</sup> Fm<sup>-1</sup>. Now, the capacitance for an isolated MWCNT is calculated using the recursive model. It is recommended in [6] that it is mandatory to determine the quantum capacitance of each shell before estimating the effective capacitance of a single MWCNT. The quantum capacitance is basically the estimation of the finite density of electronic states of quantum wire [24].

$$C_{\rm q} = \frac{4e^2}{\hbar v_{\rm F}} \sum_{i=1}^{n} N_{\rm c}(i). \tag{24}$$

According to the ESC model of MWCNTs, it can be inferred from [27] that a shell-to-shell mutual capacitance between two adjacent shells of MWCNT is:

$$C_{s}(i+1,i) = \frac{2\pi\epsilon_{0}\epsilon_{r}}{\ln\left(\frac{D_{i}+2\delta}{D_{i}}\right)}, \{i \in \mathbb{N} : 1 \le i \le n\},$$

(25)

where  $D_i$  is the diameter of the ith shell of any isolated MWCNT. At first, in the case of the outermost shell, the equivalent capacitance ( $C_{ESC}$ ), expressed in Equation (26), represents only the quantum capacitance of that shell. As much as we move toward the inner shell, the quantum capacitance of that particular shell makes a parallel combination with the equivalent capacitance ( $C_{q-s}$ ), as shown in expression (28); a series combination of the capacitance of any shell and the mutual capacitance between that shell and previous shell obtained in (27), will continue until reaching the innermost shell.

$$C_{\rm ESC}(1) = C_{\rm q}(1) \tag{26}$$

$$C_{q-s}(i-1) = \left(\frac{1}{C_{ESC}(i-1)} + \frac{1}{C_s(i+1,i)}\right)^{-1} \text{where, } \{i \in \mathbb{N} : 2 \le i \le n\}$$

(27)

$$C_{\text{ESC}}(i) = C_{q}(i) + C_{q-s}(i-1) \text{ where, } \{i \in \mathbb{N} : 2 \le i \le n\}.$$

(28)

The electrostatic capacitance demonstrates the potential difference between the ground and the CNT over the ground plane [24]. The p.u.l. electrostatic capacitance can be approximated in (29):

$$C_{\rm E} = \frac{2\pi\epsilon_0\epsilon_{\rm r}}{\ln\left(\frac{D_i + 2\delta}{D_i}\right)}. (29)$$

The conglomerate capacitance of the proposed mixed bundle is obtained in (30) by considering the overall effect of the SWCNTs and MWCNTs in the bundle. To estimate this, we considered the effect of electrostatic capacitance of MWCNTs over the ground plane on the effective capacitance in series:

Crystals **2022**, 12, 186 8 of 14

$$C_{\text{bundle}} = \frac{N_{\text{MW}_{\text{H}}} C_{\text{E}} \left( N_{\text{MW}} C_{\text{ESC}_{\text{MW}}} + N_{\text{SW}_{\Sigma}} C_{\text{SW}} \right)}{N_{\text{MW}} C_{\text{ESC}_{\text{MW}}} + N_{\text{SW}_{\Sigma}} C_{\text{SW}} + N_{\text{MW}_{\text{H}}} C_{\text{E}}}.$$

(30)

Unlike the resistance and inductance, capacitance shows a descending behavior, with a lower diameter of CNTs in the bundle. We can also notice, from Figure 4, that capacitance decreases further in higher-technology nodes. The reason behind this phenomenon is that the capacitance components rising from parallel CNTs magnify the equivalent capacitance in the bundle.

**Figure 4.** Contemporaneous denouement of capacitance of the squarely packed bundle of mixed CNTs by varying the width of the bundle and the diameter of CNTs.

## 4. Simulation Results

This section illustrates the performance comparison of a squarely packed bundle of dimorphic MWCNTs and that of mixed CNTs to exploit the feature of using mixed CNTs in the interconnect bundle. To observe the performance in terms of propagation delay, we simulate the Kahng's model, obtained from earlier work [13], using the extracted equivalent value of *RLC* and the optimized dimensions of CNTs in Section 3. Having the *RLC* value of our model, we validate the extracted conductance, inductance and capacitance rising in our configuration by comparing them with those in the previously discussed mixed CNT model in [18]. Subsequently, we assess the performance of the proposed configuration in terms of crosstalk delay, excerpted from [4], using the optimized size of particular CNTs and extracted *RLC* in Section 3, and the number of CNTs in Section 2.

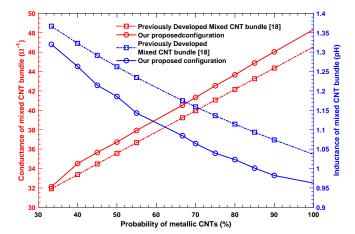

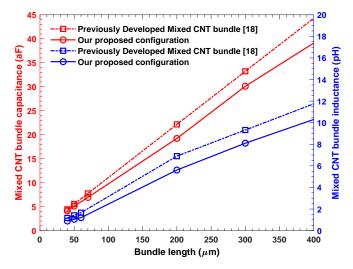

To validate the *RLC* value of the proposed model, the conductance and inductance of the mixed CNT bundle is observed by varying the probability of metallic CNT (%) using Equation (1). We observe, from Figure 5, that the conductance of our mixed CNT bundle configuration varies proportionally with the percentage of metallic CNTs in the bundle. It can be deduced from expression (1) that the number of channels per shell increases with an increase in the percentage of metallic CNTs, which, in turn, reduces the resistance and increases the conductance of the bundle. As our proposed configuration is densely packed and geometrically organized, its capacity to hold a noticeably higher number of CNTs in the bundle makes the conductance of our configuration, as depicted in Figure 5, much higher than that of the mixed CNT bundle in [18]. For the same reason, our proposed configuration comes up with a lower inductance than the previous mixed CNT models in both Figures 5 and 6. Figure 6, meanwhile, demonstrates that the capacitance of the proposed model increases with increasing interconnect lengths, though our configuration still sustains better performance by generating lower capacitances. In this circumstance, we

Crystals 2022, 12, 186 9 of 14

can infer that by increasing the percentage of metallic CNTs and delimiting the interconnect length, we can reduce the extracted *RLC* parameter and, eventually, the delay.

**Figure 5.** Impact of increasing metallic CNTs on the conductance and inductance and comparison of the results of the proposed configuration and the earlier mixed CNT bundle configuration. Overall conductance and inductance of the mixed CNT bundle is obtained, considering the interconnect length of 40 nm.

**Figure 6.** Findings of overall bundle inductance (L) and capacitance (C) for different interconnect lengths to observe the comparative parameter illustration of the proposed configuration and the previous model by considering that  $\frac{2}{3}$  of the CNTs are metallic in the bundle.

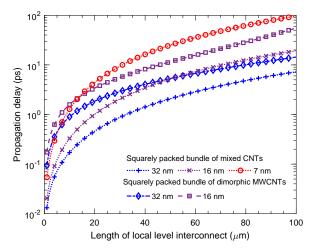

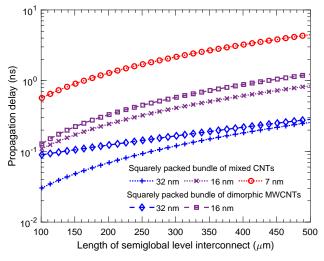

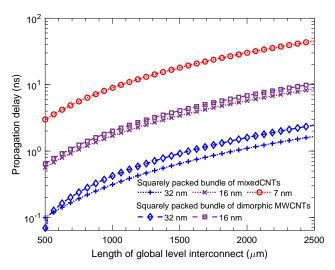

It is demonstrable from Figures 7–9 that our proposed configuration yields a lower propagation delay than the preceding configuration in [17] does. It is conspicuous, from Table 1. that we can increase the number of CNTs without distorting the overall configuration of the squarely packed bundle using the proposed approach. As a consequence, the resistance and inductance decreases while the capacitance increases for any specific technology node. Finally, the overall impact decreases the propagation delay for the squarely packed bundle of mixed CNTs, which is represented in the Figures 7–9 for the local, semiglobal, and global levels, respectively. However, the preceding squarely packed bundle configuration does not seem suitable for 7-nm technology nodes, because of the unavailability of space to accommodate CNTs of various sizes. Hence, the simulation illustrations don not include the delay of a squarely packed bundle of dimorphic MWCNTs for 7-nm technology. In comparison with [18], the unique contribution of our proposed configuration is the feasibility for 32-nm, 16-nm, and 7-nm technology nodes, along with performance enhancements.

Crystals **2022**, 12, 186 10 of 14

| <b>Table 1.</b> Diameter and number of pertinent CNTs accommodated in the bundle during simulation to |

|-------------------------------------------------------------------------------------------------------|

| obtain propagation delay and crosstalk delay.                                                         |

| Interconnect<br>Length (μm) | Technology<br>Node (nm) | Squarely Packed Dimorphic                            |               |                               |               | Squarely Packed Mixed              |             |                      |                         |

|-----------------------------|-------------------------|------------------------------------------------------|---------------|-------------------------------|---------------|------------------------------------|-------------|----------------------|-------------------------|

|                             |                         | $\frac{D_{\text{MW}_{\text{max}}}^{L}}{(\text{nm})}$ | $N_{ m MW}^L$ | $D^s_{ m MW_{max}} \  m (nm)$ | $N_{ m MW}^s$ | D <sub>MW<sub>max</sub></sub> (nm) | $N_{ m MW}$ | D <sub>SW</sub> (nm) | $N_{	extsf{SW}_\Sigma}$ |

| Local (0–100)               | 32 nm                   | 10                                                   | 32            | 4.31                          | 21            | 10                                 | 21          | 1                    | 96                      |

|                             | 16 nm                   | 8.5                                                  | 8             | 3.72                          | 3             | 8.5                                | 8           | 1                    | 15                      |

|                             | 7 nm                    | -                                                    | -             | -                             | -             | 4.5                                | 3           | 1                    | 8                       |

| Semiglobal (101–500)        | 32 nm                   | 10                                                   | 32            | 4.31                          | 21            | 10                                 | 21          | 1                    | 96                      |

|                             | 16 nm                   | 8.5                                                  | 8             | 3.72                          | 3             | 8.5                                | 8           | 1                    | 15                      |

|                             | 7 nm                    | -                                                    | -             | -                             | -             | 4.5                                | 3           | 1                    | 8                       |

| Global<br>(501–2500)        | 32 nm                   | 10                                                   | 48            | 4.31                          | 33            | 10                                 | 33          | 1                    | 160                     |

|                             | 16 nm                   | 8.5                                                  | 14            | 3.72                          | 6             | 8.5                                | 12          | 1                    | 25                      |

|                             | 7 nm                    | -                                                    | -             | -                             | -             | 4.5                                | 12          | 1                    | 5                       |

**Figure 7.** Comparison of delay performance of a squarely packed bundle of mixed CNTs and that of dimorphic MWCNTs for local-level interconnect lengths. The size and number of accommodated CNTs for different technology nodes are mentioned in Table 1.

**Figure 8.** Illustration of comparative delay performance of a squarely packed bundle of mixed CNTs and that of dimorphic MWCNTs for semiglobal-level interconnect lengths. The size and number of accommodated CNTs for different technology nodes are mentioned in Table 1.

Crystals 2022, 12, 186 11 of 14

**Figure 9.** Demonstration of comparison between the propagation delay performance of a squarely packed bundle of mixed CNTs and that of dimorphic MWCNTs for global-level interconnect lengths. The size and number of accommodated CNTs for different technology nodes are mentioned in Table 1.

The crosstalk delay, basically, arises from the capacitance formed between the CNTs from different bundles, while it is considered that all CNTs in the bundles are in parallel [4]. The inter-bundle capacitance, the function of spacing between the the centers of two adjacent CNTs, the average diameter of the adjacent CNTs, and the relative permittivity based on the level of interconnect length, is estimated by Equation (31), where  $D_{\rm MW_{max}}$  is used as the diameter because we placed MWCNTs on the edge of the bundle to reduce the overall crosstalk impact, having been motivated by previous works [6,9]:

$$C_{\rm cm_{ESC}} = \frac{\pi \epsilon_0 \epsilon_{\rm r}}{\cosh^{-1} \left(\frac{S_{\rm p}}{D_{\rm MW_{\rm max}}}\right)} N_{\rm MW_h}. \tag{31}$$

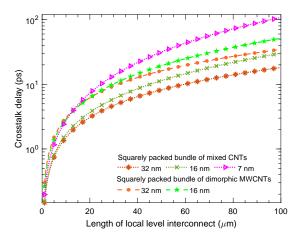

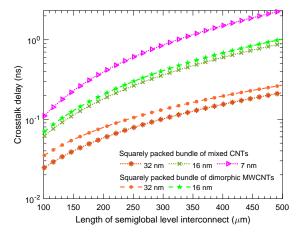

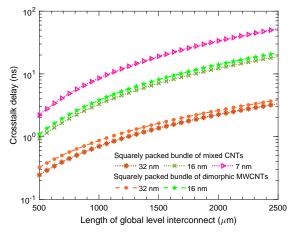

Eventually, the crosstalk performance of our proposed configuration is depicted in Figures 10–12 for local-, semiglobal-, and global-level interconnects by comparing with the preceding configuration from [17]. It is noticeable from Figure 11 that the crosstalk performance of the proposed configuration is substantial for both the 32-nm and 16-nm technology nodes. On the other hand, Figure 11 illustrates significant crosstalk performance betterment in the 32-nm technology node, compared with that in the 16-nm technology node. In the case of the global-level interconnect, the amount of crosstalk delay performance enhancement of our proposed configuration for both 32-nm and 16-nm technology nodes is almost the same, as is illustrated in Figure 12. It is also demonstrable that our proposed configuration is appropriate for 7-nm technology nodes.

Crystals **2022**, 12, 186 12 of 14

**Figure 10.** Comparative exhibition of the crosstalk delay of the proposed and previously developed bundle configurations for different technology nodes at local-level interconnect lengths. The dimension of the used CNTs are the same as those used in the simulation for obtaining propagation delays at the local level.

**Figure 11.** Comparative analysis of the crosstalk delay of the proposed and previously developed bundle configurations for different technology nodes at semiglobal-level interconnect lengths. The dimension of the used CNTs are the same as those used in the simulation for obtaining propagation delays at the semiglobal level.

**Figure 12.** Comparative illustration of the crosstalk delay of the proposed and previously developed bundle configurations for different technology nodes at global-level interconnect lengths. The diameter and number of the used CNTs are the same as those used in the simulation for obtaining propagation delays at the global level.

Crystals 2022, 12, 186 13 of 14

#### 5. Conclusions

A modified configuration of the squarely packed bundle of mixed CNTs is presented to assure the high speed VLSI interconnect with less area possession. By proposing this configuration, the simultaneous applicability of both MWCNTs and SWCNTs for scaled interconnects in future VLSI-integrated circuits is analyzed abstractly. The propagation delay and crosstalk delay performance are extracted and analyzed using an *RLC* model and a delay model. As a result, it exhibits the transcendence of squarely packed bundles of mixed CNTs for local-, semiglobal-, and global-level interconnects at 32-nm, 16-nm, and 7-nm technology nodes. In this approach, CNTs with only two different sizes are used. In the upcoming endeavor, our intention is to advance the work by adding the CNTs with various sizes to make the configuration more convenient in terms of fabrication process.

**Author Contributions:** Conceptualization, A.B.A.; methodology, A.B.A.; software, A.B.A.; validation, A.B.A.; formal analysis, A.B.A.; investigation, A.B.A.; resources, S.M.S.; data curation, A.B.A.; writing—original draft preparation, A.B.A.; writing—review and editing, A.B.A.; visualization, A.B.A.; supervision, M.S.U.; project administration, M.S.U.; funding acquisition, M.S.U. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

Institutional Review Board Statement: Not applicable.

**Informed Consent Statement:** Not applicable.

Data Availability Statement: Not applicable.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

1. Li, H.; Yin, W.Y.; Banerjee, K.; Mao, J.F. Circuit modeling and performance analysis of multi-walled carbon nanotube interconnects. *IEEE Trans. Electron Devices* **2008**, *55*, 1328–1337. [CrossRef]

- 2. Kabir, M.S. Controlled Growth of a Nanostructure on a Substrate, and Electron Emission Devices Based on the Same. U.S. Patent 7,977,761, 12 July 2011.

- 3. Liew, K.; Wong, C.; He, X.; Tan, M. Thermal stability of single and multi-walled carbon nanotubes. *Phys. Rev. B* **2005**, *71*, 075424. [CrossRef]

- 4. Kaushik, B.K.; Majumder, M.K. Carbon Nanotube Based VLSI Interconnects: Analysis and Design; Springer: Berlin/Heidelberg, Germany, 2015.

- 5. Pu, S.; Yin, W.; Mao, J.; Liu, Q.H. Crosstalk Prediction of Single- and Double-Walled Carbon-Nanotube (SWCNT/DWCNT) Bundle Interconnects. *IEEE Trans. Electron Devices* **2009**, *56*, 560–568. [CrossRef]

- 6. Subash, S.; Kolar, J.; Chowdhury, M.H. A new spatially rearranged bundle of mixed carbon nanotubes as VLSI interconnection. *IEEE Trans. Nanotechnol.* **2011**, 12, 3–12. [CrossRef]

- 7. Kim, S.; Kulkarni, D.D.; Rykaczewski, K.; Henry, M.; Tsukruk, V.V.; Fedorov, A.G. Fabrication of an ultralow-resistance ohmic contact to MWCNT-metal interconnect using graphitic carbon by electron beam-induced deposition (EBID). *IEEE Trans. Nanotechnol.* **2012**, *11*, 1223–1230. [CrossRef]

- 8. Amin, A.B.; Ullah, M.S. Mathematical Framework of Tetramorphic MWCNT Configuration for VLSI Interconnect. *IEEE Trans. Nanotechnol.* **2020**, *19*, 749–759. [CrossRef]

- 9. Majumder, M.K.; Kaushik, B.K.; Manhas, S.K. Analysis of delay and dynamic crosstalk in bundled carbon nanotube interconnects. *IEEE Trans. Electromagn. Compat.* **2014**, *56*, 1666–1673. [CrossRef]

- 10. Rai, M.K.; Garg, H.; Kaushik, B. Temperature-dependent modeling and crosstalk analysis in mixed carbon nanotube bundle interconnects. *J. Electron. Mater.* **2017**, *46*, 5324–5337. [CrossRef]

- 11. Sharma, M.; Rai, M.K.; Khanna, R. Temperature-dependent crosstalk and frequency spectrum analyses in adjacent interconnects of a mixed CNT bundle. *J. Comput. Electron.* **2020**, *19*, 177–190. [CrossRef]

- 12. Sandha, K.S.; Thakur, A. Comparative Analysis of Mixed CNTs and MWCNTs as VLSI Interconnects for Deep Sub-micron Technology Nodes. *J. Electron. Mater.* **2019**, *48*, 2543–2554. [CrossRef]

- 13. Kahng, A.B.; Muddu, S. An analytical delay model for RLC interconnects. *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.* **1997**, *16*, 1507–1514. [CrossRef]

- 14. Ullah, M.S.; Chowdhury, M.H. Analytical models of high-speed RLC interconnect delay for complex and real poles. *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.* **2017**, 25, 1831–1841. [CrossRef]

Crystals 2022, 12, 186 14 of 14

Sanaullah, M.; Chowdhury, M.H. Analysis of RLC interconnect delay model using second order approximation. In Proceedings of the 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne, VIC, Australia, 1–5 June 2014; pp. 2756–2759.

[CrossRef]

- Sanaullah, M.; Chowdhury, M.H. A new real pole delay model for RLC interconnect using second order approximation. In Proceedings of the 2014 IEEE 57th International Midwest Symposium on Circuits and Systems (MWSCAS), College Station, TX, USA, 3–6 August 2014; pp. 238–241. [CrossRef]

- 17. Amin, A.B.; Ullah, M.S. Performance Analysis of Squarely Packed Dimorphic MWCNT Bundle for High Speed VLSI Interconnect. In Proceedings of the 2020 IEEE Canadian Conference on Electrical and Computer Engineering (CCECE), London, ON, Canada, 30 August–2 September 2020; pp. 1–6. [CrossRef]

- 18. Subash, S.; Chowdhury, M.H. Mixed carbon nanotube bundles for interconnect applications. *Int. J. Electron.* **2009**, *96*, 657–671. [CrossRef]

- 19. Li, H.; Lu, W.; Li, J.; Bai, X.; Gu, C. Multichannel ballistic transport in multiwall carbon nanotubes. *Phys. Rev. Lett.* **2005**, 95, 086601. [CrossRef]

- 20. Naeemi, A.; Meindl, J.D. Compact physical models for multiwall carbon-nanotube interconnects. *IEEE Electron Device Lett.* **2006**, 27, 338–340. [CrossRef]

- Amin, A.B.; Ullah, M.S. Performance Analysis of Squarely Packed Polymorphic SWCNT Interconnect. In Proceedings of the 2019 IEEE 10th Annual Ubiquitous Computing, Electronics Mobile Communication Conference (UEMCON), New York, NY, USA, 10–12 October 2019; pp. 1199–1203. [CrossRef]

- 22. Naeemi, A.; Meindl, J.D. Physical modeling of temperature coefficient of resistance for single-and multi-wall carbon nanotube interconnects. *IEEE Electron Device Lett.* **2007**, *28*, 135–138. [CrossRef]

- 23. Das, D.; Rahaman, H. Analysis of crosstalk in single-and multiwall carbon nanotube interconnects and its impact on gate oxide reliability. *IEEE Trans. Nanotechnol.* **2011**, *10*, 1362–1370. [CrossRef]

- 24. Majumder, M.K.; Das, P.K.; Kaushik, B.K. Delay and crosstalk reliability issues in mixed MWCNT bundle interconnects. *Microelectron. Reliab.* **2014**, *54*, 2570–2577. [CrossRef]

- 25. Srivastava, N.; Li, H.; Kreupl, F.; Banerjee, K. On the applicability of single-walled carbon nanotubes as VLSI interconnects. *IEEE Trans. Nanotechnol.* **2009**, *8*, 542–559. [CrossRef]

- Sahoo, M.; Ghosal, P.; Rahaman, H. Modeling and analysis of crosstalk induced effects in multiwalled carbon nanotube bundle interconnects: An ABCD parameter-based approach. *IEEE Trans. Nanotechnol.* 2015, 14, 259–274. [CrossRef]

- 27. Sarto, M.S.; Tamburrano, A. Single-conductor transmission-line model of multiwall carbon nanotubes. *IEEE Trans. Nanotechnol.* **2009**, *9*, 82–92. [CrossRef]

- 28. Banerjee, K.; Srivastava, N. Are carbon nanotubes the future of VLSI interconnections? In Proceedings of the 43rd annual Design Automation Conference, San Francisco, CA, USA, 24–28 July 2006; pp. 809–814.