Article

# The Role of III-V Substrate Roughness and Deoxidation Induced by Digital Etch in Achieving Low Resistance Metal Contacts

Florent Ravaux, Irfan Saadat and Mustapha Jouiad \*

Department of Mechanical & Materials Science and Electrical Engineering & Computer Science, Masdar Institute of Science and Technology, A part of Khalifa University of Science and Technology, P.O. Box 54224, Abu Dhabi 54224, UAE; fravaux@masdar.ac.ae (F.R.); isaadat@masdar.ac.ae (I.S.)

\* Correspondence: mjouiad@masdar.ac.ae; Tel.: +971-02-810-9235

Academic Editor: Shujun Zhang

Received: 2 May 2017; Accepted: 13 June 2017; Published: 19 June 2017

**Abstract:** To achieve low contact resistance between metal and III-V material, transmission-line-model (TLM) structures of molybdenum (Mo) were fabricated on indium phosphide (InP) substrate on the top of an indium gallium arsenide (InGaAs) layer grown by molecular beam epitaxy. The contact layer was prepared using a digital etch procedure before metal deposition. The contact resistivity was found to decrease significantly with the cleaning process. High Resolution Transmission & Scanning Electron Microscopy (HRTEM & HRSTEM) investigations revealed that the surface roughness of treated samples was increased. Further analysis of the metal-semiconductor interface using Energy Electron Loss Spectroscopy (EELS) showed that the amount of oxides ( $In_xO_y$ ,  $Ga_xO_y$  or  $As_xO_y$ ) was significantly decreased for the etched samples. These results suggest that the low contact resistance obtained after digital etching is attributed to the combined effects of the induced surface roughness and oxides removal during the digital etch process.

Keywords: III-V materials; digital etch; low contact resistance; HRTEM; EELS

#### 1. Introduction

Since the emergence of the semiconductor industry in the 1950s, research orientations have been driven by the downscaling of Metal Oxide Semiconductor Field Effect Transistor (MOSFET) dimensions, as described by Moore's law and Dennard's scaling rules. As the gate dimensions are approaching a single digit node, new MOSFET performance boosters have been successfully introduced to overcome scaling issues due to lithography challenges. Thus, the integration of new materials, such as strained semiconductors, new gate materials, and high mobility channel materials, as well as new transistor architectures such as ultra-thin body, FinFet, or gate all around architectures are valuable solutions to increase MOSFET performances [1].

In this context, the integration of a IIII-V semiconductor is considered as a tangible solution for the replacement of a silicon channel. Due to its exceptional mobility, this technology is targeted for the 5–7 nm technology nodes, thanks to the successful integration of a high mobility active area on the silicon substrate (by localized epitaxial growth) [2]. Thus, the optimization of III-V semiconductor MOSFET characteristics in term of low contact resistance, doping profile, or oxide integration has attracted great interest. In light of this, the integration of performing source/drain contacts is a critical aspect of the success of III-V semiconductors for extreme dimensions/technology nodes. Historically, multilayered contacts based on gold were usually used in III-V semiconductors [3]. With this renewed interest, several techniques have been explored to overcome this technological obstacle. For instance, Ni-III-V semiconductor compounds showed low contact resistance but poor thermal stability. Nevertheless,

Crystals **2017**, 7, 177 2 of 7

the integration of an interlayer between the metal and the semiconductor resulted in thermal stability improvement while availing the self-aligned advantage of this technology [4–6]. In addition, non-alloyed Mo contacts to III-V semiconductors have been also identified as a possible solution [7]. To further improve this performance, several techniques have been developed [8]. For example, the insertion of a good quality, high-k dielectric layer between the metal and silicon was found to reduce Fermi level pinning, leading to a lower specific contact resistance. This method was applied to InGaAs with relatively great success [9].

Moreover, doping was also found to decrease contact resistance once appropriately tuned [10]. Indeed, silicon implantation has historically been used for III-V MOSFET implementation, but this technique suffers from two main disadvantages: (1) the surface and the crystal are damaged during the implantation, and (2) the doping level is limited to  $1 \times 10^{19}$  atoms/cm³ due to the amphoteric behavior of silicon [11]. For these reasons, two other unconventional solutions have been explored to further improve source/drain characteristics: (1) sulfur monolayer doping, which was successfully combined with Mo contacts to overcome the crystal damage induced by the implantation [12]. This technique has the advantage of giving a sharp doping profile but struggles against short channel effects. (2) Tellerium doping, which was performed during the chemical vapor deposition (CVD) growth, allows for the prevention of the crystal damage and amphoteric issues [13].

In this study, we conducted in-depth characterization investigations using advanced analytical tools to describe the role of the digital etch method as a novel surface treatment prior to metal deposition over III-V semiconductors in achieving low resistance metal contacts. Digital etching is a self-limiting etching process developed for the fabrication of optoelectronic devices, quantum devices, and nanostructures. This process allows one to control the etching rate with near-monolayer accuracy, which makes it very interesting compared to other technologies. Moreover, the monolayer self-limiting etching of silicon has been demonstrated using a four-step process (dry oxidation using chlorine gas, followed by a dry etching using argon gas) [14]. A similar technique was commonly used with III-V semiconductors, mainly for gate recess etching during the fabrication of high-electron-mobility transistors (HEMTs). As for silicon technology, a surface oxidation step, which can be dry [15,16] or wet [17,18], is followed by a wet oxide removal step.

# 2. Materials and Methods

The semiconductor surface treatment consists of performing an atomic layer etching of InGaAs prior to Mo deposition. In this study, the digital etch process was performed using low power  $O_2$  plasma (100 watts) in an Asher system and wet etching at room temperature using a solution of  $H_2SO_4$ : $H_2O = 1:1$  for 30 s [19]. TEM lamella, used for High Resolution Transmission Electron Microscopy and Energy Electron Loss Spectroscopy (HRTEM & EELS) investigations, were then prepared using a dual beam system consisting of Focused Ion Beam and Scanning Electron Microscopy (FIB/SEM) Helios Nano Lab FEI<sup>TM</sup>, using the standard method [20]. HRTEM & EELS analyses were performed using Cs corrected Titan FEI<sup>TM</sup> and Gatan<sup>TM</sup> filter, respectively.

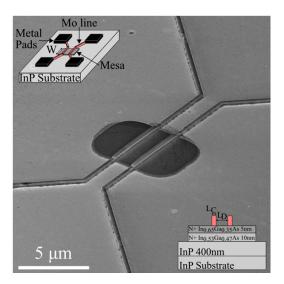

To evaluate the effect of the digital etch process, the electrical characterization of Transmission-Line-Model (TLM) structure was carried out on two different devices prepared respectively with and without the digital etch procedure [21]. Both TLM structures were processed on a bilayer heterostructure grown on InP substrate. The bilayer heterostructure contained two main layers: 150 Å InGaAs conductive active layer and 4000 Å InP conductive buffer layer, as described in the insert of Figure 1. The cap layer consisted of two layers of heavily N-doped InGaAs ( $3.0 \times 10^{19}$ ): 50 Å layer of In<sub>0.65</sub>Ga<sub>0.35</sub>As, and 100 Å thick layer of In<sub>0.53</sub>Ga<sub>0.47</sub>As.

## 3. Results and Discussion

Figure 1 illustrates the TLM structure geometry consisting of an active mesa of InGaAs overlaid by two lines of Mo, separated by a distance  $L_D$ . The width  $L_C$  of the lines is equal to 220 nm. Two metal contact pads (gold) are present at these lines ends. The function of these metal pads is to force the

*Crystals* **2017**, *7*, 177 3 of 7

current flowing through the Mo/InGaAs interface and mesa while probing the voltage difference between the two Mo lines. The resistance is then calculated for different devices with various  $L_D$  values [22].

**Figure 1.** SEM image of the Transmission-Line-Model (TLM) device. The inserts represent the TLM structure scheme (**top**) and the cross-section showing different layers of the active area (**bottom**).

## 3.1. Resistivity

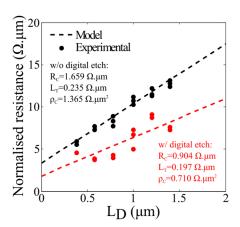

Figure 2 provides the electrical characterization of the two different devices. The normalized resistance is given as a function of  $L_D$  (the distance separating the Mo lines). The specific contact resistance is then extracted by fitting the model with experimental data for structures processed with and without digital etch [21]. The use of the digital etch procedure allows one to obtain an 84% decrease of the specific contact resistance, namely dropping from 1.365  $\Omega \cdot \mu m^2$  to 0.710  $\Omega \cdot \mu m^2$ . These results are lower than those obtained by Zhang [7] (10  $\Omega \cdot \mu m^2$  for Mo/InGaAs), but higher than those obtained by Liao [9] (0.67  $\Omega \cdot \mu m^2$  for Al/ZnO/InGaAs).

**Figure 2.** Variation of normalized resistance as a function of contact spacing L<sub>D</sub>.

## 3.2. Device Conformity

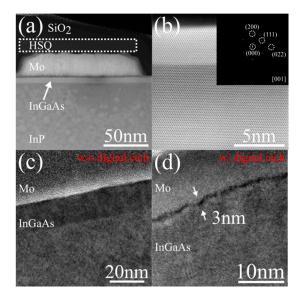

Figure 3a,b show the High Resolution Scanning Transmission Electron Microscope (HRSTEM) micrographs of the device and the metal/semiconductor interface, which are the most convenient to check the different steps of the process flow. Based on these images, two main remarks can be made

Crystals **2017**, 7, 177 4 of 7

regarding the structure of the device. First, the SiO<sub>2</sub> deposition seems to be conformal because the covering of the line is uniform at the edges at a very high magnification. The hard mask thickness appears to be sufficient to protect the InGaAs layer during the mesa patterning by plasma etching. Hence, lateral etching is observed to be below the hydrogen silsesquioxane (HSQ) negative resist during the Reactive Ion Etching (RIE) Mo lines patterning. Despite this isotropy, the etching presents good selectivity over InGaAs because the layer thickness seems to be constant over the whole mesa. The dark field STEM image (cf. Figure 3b) highlights the InGaAs layer, which is also present along the whole interface, meaning that the metal deposition was efficient and nondestructive.

## 3.3. Interface Probing

Figure 3c,d give HRTEM images of the Mo/InGaAs interface for both samples with and without digital etch. The interfaces quality was first checked along the 3-µm Mo lines on multiple samples treated with digital etching. The deposited Mo lines exhibit good uniformity and a uniform thickness. One can clearly notice (Figure 3d) the presence of the surface roughness, which was generated by digital etching during the contact surface preparation, whereas this contact surface appears flat in Figure 3c for the untreated sample. A maximum height of 3 nm was measured in all observed samples. This effect is generally observed on the surface morphology during the digital etch process for different materials and different wet etchants [23]. Therefore, we believe that these serrated lines present in the interface due to the surface roughness allow one to obtain a large contact surface of the Mo layer over the InGaAs surface, leading to a significant decrease in the contact resistance.

**Figure 3.** (a) STEM-HAADF (High-Annular Angle Dark Filed) cross-sectional image; (b) HR-STEM of the InGaAs layer (insert shows the Fast Fourier Transform FFT); TEM images of (c) the untreated sample and (d) the sample prepared with digital etch.

It is worth noting that the HRTEM investigations provided us with one possible reason (surface roughness) behind the low contact resistance obtained for the treated sample; nevertheless, additional investigations were performed to further comprehend such a low value. Therefore, the correlation between the digital etch process and its effect on local chemistry, especially at the interface, attracted great interest. To screen the chemical composition at this fine region, we combined both HR-STEM and EELS techniques. These techniques allow one to probe the interface quality in terms of defects and at the same time it provides the local chemistry to evaluate the reactivity of Mo with InGaAs [24,25].

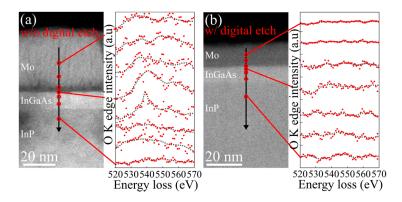

Figure 4a,b show the line scans across the Mo/InGaAs interfaces using EELS for the untreated sample and the digital etched sample, respectively. The EELS spectra were recorded along the black

*Crystals* **2017**, *7*, 177 5 of 7

arrows. The energy window was decreased and limited to 520–570 eV range to increase the resolution of the oxygen k-edge detection.

**Figure 4.** STEM-HAADF image of the metal/semiconductor interface of sample (a) without the digital etch treatment and (b) with the digital etch treatment. The arrow represents the localization of the EELS spectra recorded point-by-point.

Close inspection of the energy spectra, especially around the peak value of 535 eV, which is the signature of the oxygen k-edge, reveals the presence of this peak for the untreated sample. This peak appears broad in the upper and bottom layers, but it is more acute and sharp when crossing the interface. In the contrast, for the digital etched sample, the peaks remain flat for all scanned regions; this shows the absence of oxygen atoms at the interface for the treated sample. This result suggests then that oxides such as  $In_xO_y$ ,  $As_xO_y$ , and the more energetically favored oxide  $Ga_xO_y$  may be present at the interface between Mo and the InGaAs layers [26,27], but that they had been successfully removed by the digital etch process. This finding brings an additional fact that can be considered as another reason behind the low contact resistance measured in digital etched samples.

#### 4. Conclusions

Thanks to the digital etch process, we obtained contact resistance values as low as  $0.710~\Omega\cdot\mu\text{m}^2$  for InGaAs compound. This low resistance is attributed to two main factors generated by the digital etch process, namely: (1) large contact surface due to the surface roughness, and (2) the oxides removal during the etch process.

**Acknowledgments:** Authors are grateful to SRC MEESII and Masdar Institute of Science and Technology for Micro/Nano Fabrication and Electron Microscopy Facilities. Authors express their acknowledgments to Jesus del Alamo (MIT) for his collaboration with digital etch technique and fruitful discussions.

**Author Contributions:** Florent Ravaux and Irfan Saadat designed and fabricated the devices. Florent Ravaux and Mustapha Jouiad characterized the devices and analyzed the data. Florent Ravaux and Mustapha Jouiad wrote the paper.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- Skotnicki, T.; Hutchby, J.A.; King, T.; Wong, H.S.P.; Boeuf, F. The end of CMOS scaling: Toward the introduction of new materials and structural changes to improve MOSFET performance. *IEEE Circuits Devices Mag.* 2005, 21, 16–26. [CrossRef]

- 2. Del Alamo, J.A. Nanometre-scale electronics with III-V compound semiconductors. *Nature* **2011**, 479, 317–323. [CrossRef] [PubMed]

- 3. Hu, C.Y.; Hashizume, T.; Ohi, K.; Tajima, M. Trapping effect evaluation of gateless AlGaN/GaN heterojunction field-effect transistors using transmission-line-model method. *Appl. Phys. Lett.* **2010**, *97*, 222103. [CrossRef]

Crystals **2017**, 7, 177 6 of 7

4. Kim, S.H.; Yokoyama, M.; Taoka, N.; Iida, R.; Lee, S.; Nakane, R.; Urabe, Y.; Miyata, N.; Yasuda, T.; Yamada, H.; et al. Self-aligned metal source/drain In<sub>x</sub>Ga<sub>1-x</sub>As n-MOSFETs using Ni-InGaAs alloy. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 6–8 December 2010; pp. 596–599.

- 5. Zhang, X.; Guo, H.; Ko, C.H.; Wann, C.H.; Cheng, C.C.; Lin, H.Y.; Chin, H.C.; Gong, X.; Lim, P.S.Y.; Luo, G.L.; et al. III-V MOSFETs with a new self-aligned contact. In Proceedings of the 2010 Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2010; pp. 233–234.

- Yuan, Z.; Kumar, A.; Chen, C.Y.; Nainani, A.; Bennett, B.R.; Boos, J.B.; Saraswat, K.C. Antimonide-Based Heterostructure p-Channel MOSFETs with Ni-Alloy Source/Drain. *IEEE Electron Device Lett.* 2013, 34, 1367–1369. [CrossRef]

- 7. Zhang, X.; Guo, H.X.; Zhu, Z.; Gong, X.; Yeo, Y.C. In<sub>0.53</sub>Ga<sub>0.47</sub>As FinFETs with self-aligned molybdenum contacts and HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> gate dielectric. *Solid State Electron.* **2013**, *84*, 83–89. [CrossRef]

- 8. Lee, R.T.P.; Loh, W.Y.; Tieckelmann, R.; Orzali, T.; Huffman, C.; Vert, A.; Huang, G.; Kelman, M.; Karim, Z.; Hobbs, C.; et al. Technology Options to Reduce Contact Resistance in Nanoscale III-V MOSFETs. *ECS Trans.* **2015**, *66*, 125–134. [CrossRef]

- Liao, M.H.; Chen, P.K. Experimental demonstration on the ultra-low source/drain resistance by metal-insulator-semiconductor contact structure in In<sub>0.53</sub>Ga<sub>0.47</sub>As field-effect transistors. AIP Adv. 2013, 3, 092118. [CrossRef]

- 10. Law, J.J.M.; Carter, A.D.; Lee, S.; Huang, C.Y.; Lub, H.; Rodwell, M.J.W.; Gossard, A.C. Co-doping of In<sub>x</sub>Ga<sub>1-x</sub>As with silicon and tellurium for improved ultra-low contact resistance. *J. Cryst. Growth* **2013**, 378, 92–95. [CrossRef]

- 11. Jones, K.S.; Lind, A.G.; Hatem, C.; Moffatt, S.; Ridgeway, M.C. A Brief Review of Doping Issues in III-V Semiconductors. *ECS Trans.* **2013**, *53*, 97–105. [CrossRef]

- 12. Barnett, J.; Hill, R.; Loh, W.Y.; Hobbs, C.; Majhi, P.; Jammy, R. Advanced techniques for achieving ultra-shallow junctions in future CMOS devices. In Proceedings of the 2010 International Workshop on Junction Technology, Shanghai, China, 10–11 May 2010; pp. 1–4.

- 13. Orzali, T.; Vert, A.; Lee, R.T.P.; Norvilas, A.; Huang, G.; Herman, J.L.; Hill, R.J.W.; Papa Rao, S.S. Heavily tellurium doped n-type InGaAs grown by MOCVD on 300 mm Si wafers. *J. Cryst. Growth* **2007**, 426, 243–247. [CrossRef]

- 14. Athavalea, S.D.; Economoub, D.J. Realization of atomic layer etching of silicon. *J. Vac. Sci. Technol. B* **1996**, 14, 3702–3805. [CrossRef]

- 15. Ko, K.K.; Pang, S.W. Controllable layer-by-layer etching of III–V compound semiconductors with an electron cyclotron resonance source. *J. Vac. Sci. Technol. B* **1993**, *11*, 2275–2279. [CrossRef]

- 16. Lin, J.; Zhao, X.; Yu, T.; Antoniadis, D.A.; del Alamo, J.A. A new self-aligned quantum-well MOSFET architecture fabricated by a scalable tight pitch process. In Proceedings of the 2013 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 9–11 December 2013; pp. 421–424.

- 17. DeSalvo, G.C.; Bozada, C.A.; Ebel, J.L.; Look, D.C.; Barrette, J.P.; Cerny, C.L.A.; Dettmer, R.W.; Gillespie, J.K.; Havasy, C.K.; Jenkins, T.J.; et al. Wet Chemical Digital Etching of GaAs at Room Temperature. *J. Electrochem. Soc.* 1996, 143, 3652–3656. [CrossRef]

- 18. Alian, A.; Merckling, C.; Brammertz, G.; Meuris, M.; Heyns, M.; De Meyer, K. InGaAs MOS transistors fabricated through a digital-etch gate-recess process and the influence of forming gas anneal on their electrical behavior. *ECS J. Solid State Sci. Technol.* **2012**, *6*, 310–314. [CrossRef]

- 19. Lin, J.; Zhao, X.; Antoniadis, D.A.; del Alamo, J.A. A Novel Digital Etch Technique for Deeply Scaled III-V MOSFETs. *IEEE Electron Device Lett.* **2014**, 35, 440–442. [CrossRef]

- 20. Rajput, N.S.; Kim, S.G.; Chou, J.B.; Abed, J.; Viegas, J.; Jouiad, M. Electron beam induced rapid crystallization of water splitting nanostructures. *MRS Adv.* **2015**, *1*, 825–830. [CrossRef]

- 21. Ravaux, F.; Alnuaimi, K.S.; Jouiad, M.; Saadat, I. Characterization of metal contact to III–V materials (Mo/InGaAs). *Microelectron. Eng.* **2015**, *145*, 1–4. [CrossRef]

- 22. Lu, W.; Guo, A.; Vardi, A.; del Alamo, J.A. A Test Structure to Characterize Nano-Scale Ohmic Contacts in III-V MOSFETs. *IEEE Electron Device Lett.* **2014**, *35*, 178–180. [CrossRef]

- Buttari, D.; Heikman, S.; Keller, S.; Mishra, U.K. Digital Etching for Highly Reproducible Low Damage Gate Recessing on AlGaN/GaN HEMTs. In Proceedings of the 2002 IEEE Lester Eastman Conference, Newark, DE, USA, 8 August 2002; pp. 461–469.

Crystals **2017**, 7, 177 7 of 7

24. Muller, D.A.; Sorsch, T.; Moccio, S.; Baumann, F.H.; Evans-Lutterodt, K.; Timp, G. The electronic structure at the atomic scale of ultrathin gate oxides. *Nature* **1999**, 399, 758–761. [CrossRef]

- 25. Verleysen, E.; Bender, H.; Richard, O.; Schryvers, D.; Vandervorst, W. Characterization of nickel silicides using EELS-based methods. *J. Microsc.* **2010**, 240, 75–82. [CrossRef] [PubMed]

- 26. Hussey, R.J.; Sproule, G.I.; McCaffrey, J.P.; Graham, M.J. Characterization of Oxides Formed on InP, InGaAs, InAlAs, and InGaAs/InAlAs Heterostructures at 300–500 °C. Oxid. Met. 2002, 57, 427–447. [CrossRef]

- 27. Brennan, B.; Hughes, G. Identification and thermal stability of the native oxides on InGaAs using synchrotron radiation based photoemission. *J. Appl. Phys.* **2010**, *108*, 053516. [CrossRef]

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).