Germanium Quantum-Dot Array with Self-Aligned Electrodes for Quantum Electronic Devices

Abstract

:1. Introduction

2. Experimental Methods and Procedures

3. Results

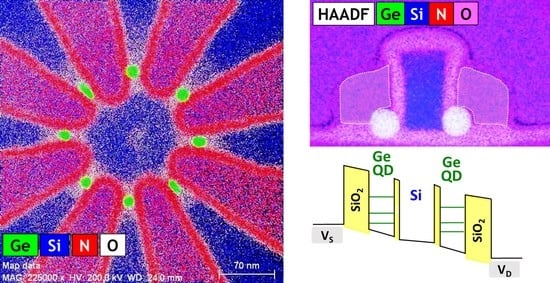

3.1. Formation of Self-Assembled, Closely-Coupled Ge QDs Arrays

3.2. Arrays of Ge QDs with Scalable Numbers and Tunable Diameters

3.3. Arrays of Ge QDs with Self-Aligned Electrodes

4. Discussion

4.1. Self-Organized, Crystalline Ge QD/SiO2-Shell with Si3N4/c-Si Coupling-Barrier Layers

4.2. Ge QD Mediated Densification of Proximal Si3N4 Barriers

4.3. Process-Controlled Placement of Spherical-Shaped Ge QDs at Designated Spatial Locations

4.4. Process-Controlled Size Tunability of Ge Spherical QDs for Operation in Few-Charge Regimes

4.5. Ge QD Array for Qubits and Charge Readout Sensors

4.6. Proof-of-Principle Ge-QD Single-Hole Transistors Operation

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Nomenclature

| Abbreviations | Full names |

| BG | barrier gate |

| CMOS | complementary metal-oxide-semiconductor |

| CB | coupling barrier |

| DQDs | double quantum dots |

| EBL | electron-beam lithography |

| EELS | electron energy loss spectroscopy |

| EDS | energy dispersive x-ray spectroscopy |

| Dit | interface trap density |

| LPCVD | low-pressure chemical vapor deposition |

| OQDs | octuple QDs |

| PL | photoluminescence |

| PG | plunger gate |

| QQDs | quadruple QDs |

| qubit | quantum bit |

| QD | quantum dot |

| SEM | scanning electron microscopy (SEM) |

| STEM | scanning transmission electron microscopy |

| SAED | selected area electron diffraction |

| SOI | silicon-on-insulator |

| SET | single-electron transistor |

| SHT | single-hole transistor |

| TEM | transmission electron microscopy |

| TQDs | triple quantum dots |

| 2DEG | two-dimensional electron gas |

| 2DHG | two-dimensional hole gas |

| VLSI | very large scale integrated circuits |

| XRD | X-ray diffraction |

References

- Mi, X.; Benito, M.; Putz, S.; Zajac, D.M.; Taylor, J.M.; Burkard, G.; Petta, J.R. A coherent spin–photon interface in silicon. Nature 2018, 555, 599–603. [Google Scholar] [CrossRef] [Green Version]

- Mehta, K.K.; Bruzewicz, C.D.; McConnell, R.; Ram, R.J.; Sage, J.M.; Chiaverini, J. Integrated optical addressing of an ion qubit. Nat. Nanotechnol. 2016, 11, 1066–1070. [Google Scholar] [CrossRef]

- Devoret, M.H.; Schoelkopf, R.J. Superconducting Circuits for Quantum Information: An Outlook. Science 2013, 339, 1169–1174. [Google Scholar] [CrossRef] [Green Version]

- London, P.; Scheuer, J.; Cai, J.; Schwarz, I.; Retzker, A.; Plenio, M.B.; Katagiri, M.; Teraji, T.; Koizumi, S.; Isoya, J.; et al. Detecting and Polarizing Nuclear Spins with Double Resonance on a Single Electron Spin. Phys. Rev. Lett. 2013, 111, 067601. [Google Scholar] [CrossRef]

- Li, H.-O.; Cao, G.; Yu, G.-D.; Xiao, M.; Guo, G.-C.; Jiang, H.-W.; Guo, G.-P. Conditional rotation of two strongly coupled semiconductor charge qubits. Nat. Commun. 2015, 6, 7681. [Google Scholar] [CrossRef] [Green Version]

- Samkharadze, N.; Zheng, G.; Kalhor, N.; Brousse, D.; Sammak, A.; Mendes, U.C.; Blais, A.; Scappucci, G.; Vandersypen, L.M.K. Strong spin-photon coupling in silicon. Science 2018, 359, 1123–1127. [Google Scholar] [CrossRef] [Green Version]

- Tosi, G.; Mohiyaddin, F.A.; Schmitt, V.; Tenberg, S.; Rahman, R.; Klimeck, G.; Morello, A. Silicon quantum processor with robust long-distance qubit couplings. Nat. Commun. 2017, 8, 1–11. [Google Scholar] [CrossRef] [Green Version]

- Pillarisetty, R.; Thomas, N.; George, H.; Singh, K.; Roberts, J.; Lampert, L.; Amin, P.; Watson, T.; Zheng, G.; Torres, J.; et al. In Proceedings of the Qubit Device Integration Using Advanced Semiconductor Manufacturing Process Technology, San Francisco, CA, USA, 1–5 December 2018. [CrossRef]

- Veldhorst, M.; Eenink, H.G.J.; Yang, H.; Dzurak, A.S. Silicon CMOS architecture for a spin-based quantum computer. Nat. Commun. 2017, 8, 1–8. [Google Scholar] [CrossRef]

- Yoneda, J.; Takeda, K.; Otsuka, T.; Nakajima, T.; Delbecq, M.; Allison, G.; Honda, T.; Kodera, T.; Oda, S.; Hoshi, Y.; et al. A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than 99.9%. Nat. Nanotechnol. 2017, 13, 102–106. [Google Scholar] [CrossRef]

- Watson, T.F.; Philips, S.G.J.; Kawakami, E.; Ward, D.; Scarlino, P.; Veldhorst, M.; Savage, D.; Lagally, M.G.; Friesen, M.; Coppersmith, S.; et al. A programmable two-qubit quantum processor in silicon. Nature 2018, 555, 633–637. [Google Scholar] [CrossRef] [Green Version]

- Maurand, R.; Jehl, X.; Kotekar-Patil, D.; Corna, A.; Bohuslavskyi, H.; Laviéville, R.; Hutin, L.; Barraud, S.; Vinet, M.; Sanquer, M.; et al. A CMOS silicon spin qubit. Nat. Commun. 2016, 7, 13575. [Google Scholar] [CrossRef] [PubMed]

- Meunier, T.; Hutin, L.; Bertrand, B.; Thonnart, Y.; Pillonnet, G.; Billiot, G.; Jacquinot, H.; Casse, M.; Barraud, S.; Kim, Y.-J.; et al. In Proceedings of the Towards Scalable Quantum Computing based on Silicon Spin, Kyoto, Japan, 9–14 June 2019. [CrossRef]

- Pillarisetty, R.; George, H.C.; Watson, T.F.; Lampert, L.; Thomas, N.; Bojarski, S.; Amin, P.; Caudillo, R.; Henry, E.; Kashani, N.; et al. High volume electrical characterization of semiconductor qubits. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 737–740. [Google Scholar]

- Masruroh, H.; Diniaty, A. Development of Chem in Action instructional media based on drill and practice in chemical equilibrium material for students in senior high school. AIP Conf. Proc. 2020, 2229, 020005. [Google Scholar] [CrossRef]

- Yang, C.H.; Leon, R.C.C.; Hwang, J.C.C.; Saraiva, A.; Tanttu, T.; Huang, W.; Lemyre, J.C.; Chan, K.W.; Tan, K.Y.; Hudson, F.E.; et al. Operation of a silicon quantum processor unit cell above one kelvin. Nature 2020, 580, 350–354. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Zwanenburg, F.A.; Dzurak, A.; Morello, A.; Simmons, M.; Hollenberg, L.; Klimeck, G.; Rogge, S.; Coppersmith, S.; Eriksson, M.A. Silicon quantum electronics. Rev. Mod. Phys. 2013, 85, 961–1019. [Google Scholar] [CrossRef]

- Angus, S.J.; Ferguson, A.J.; Dzurak, A.S.; Clark, R.G. Gate-Defined Quantum Dots in Intrinsic Silicon. Nano Lett. 2007, 7, 2051–2055. [Google Scholar] [CrossRef] [PubMed]

- Klos, J.; Sun, B.; Beyer, J.; Kindel, S.; Hellmich, L.; Knoch, J.; Schreiber, L.R. Spin Qubits Confined to a Silicon Nano-Ridge. Appl. Sci. 2019, 9, 3823. [Google Scholar] [CrossRef] [Green Version]

- Zajac, D.M.; Hazard, T.M.; Mi, X.; Wang, K.; Petta, J.R. A reconfigurable gate architecture for Si/SiGe quantum dots. Appl. Phys. Lett. 2015, 106, 223507. [Google Scholar] [CrossRef] [Green Version]

- Andrews, R.W.; Jones, C.; Reed, M.D.; Jones, A.M.; Ha, S.D.; Jura, M.P.; Kerckhoff, J.; Levendorf, M.; Meenehan, S.; Merkel, S.T.; et al. Quantifying error and leakage in an encoded Si/SiGe triple-dot qubit. Nat. Nanotechnol. 2019, 14, 747–750. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Takakura, T.; Noiri, A.; Obata, T.; Otsuka, T.; Yoneda, J.; Yoshida, K.; Tarucha, S. Single to quadruple quantum dots with tunable tunnel couplings. Appl. Phys. Lett. 2014, 104, 113109. [Google Scholar] [CrossRef] [Green Version]

- Volk, C.; Zwerver, A.M.J.; Mukhopadhyay, U.; Eendebak, P.T.; Van Diepen, C.J.; Dehollain, J.P.; Hensgens, T.; Fujita, T.; Reichl, C.; Wegscheider, W.; et al. Loading a quantum-dot based “Qubyte” register. npj Quantum Inf. 2019, 5, 29. [Google Scholar] [CrossRef] [Green Version]

- Thorbeck, T.; Zimmerman, N.M. Formation of strain-induced quantum dots in gated semiconductor nanostructures. AIP Adv. 2015, 5, 087107. [Google Scholar] [CrossRef] [Green Version]

- Brauns, M.; Amitonov, S.V.; Spruijtenburg, P.-C.; Zwanenburg, F.A. Palladium gates for reproducible quantum dots in silicon. Sci. Rep. 2018, 8, 1–8. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Tarucha, S.; Austing, D.G.; Honda, T.; van der Hage, R.J.; Kouwenhoven, L.P. Shell Filling and Spin Effects in a Few Electron Quantum Dot. Phys. Rev. Lett. 1996, 77, 3613–3616. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Horibe, K.; Kodera, T.; Oda, S. Lithographically defined few-electron silicon quantum dots based on a silicon-on-insulator substrate. Appl. Phys. Lett. 2015, 106, 083111. [Google Scholar] [CrossRef]

- Mizokuchi, R.; Oda, S.; Kodera, T. Physically defined triple quantum dot systems in silicon on insulator. Appl. Phys. Lett. 2019, 114, 073104. [Google Scholar] [CrossRef]

- Zhou, Y.; Han, W.; Chang, L.-T.; Xiu, F.; Wang, M.; Oehme, M.; Fischer, I.A.; Schulze, J.; Kawakami, R.K.; Wang, K.L. Electrical spin injection and transport in germanium. Phys. Rev. B 2011, 84, 125323. [Google Scholar] [CrossRef] [Green Version]

- Hendrickx, N.; Franke, D.P.; Sammak, A.; Scappucci, G.; Veldhorst, M. Fast two-qubit logic with holes in germanium. Nature 2020, 577, 487–491. [Google Scholar] [CrossRef] [Green Version]

- Froning, F.N.M.; Rehmann, M.K.; Ridderbos, J.; Brauns, M.; Zwanenburg, F.; Li, A.; Bakkers, E.P.A.M.; Zumbühl, D.M.; Braakman, F.R. Single, double, and triple quantum dots in Ge/Si nanowires. Appl. Phys. Lett. 2018, 113, 073102. [Google Scholar] [CrossRef] [Green Version]

- 32. Vukusic, L.; Kukucka, J.; Watzinger, H.; Katsaros, G. Fast hole tunneling times in germanium hut wires probed by single-shot reflectometry. Nano Lett. 2017, 17, 5706. [Google Scholar] [CrossRef] [Green Version]

- Scappucci, G.; Kloeffel, C.; Zwanenburg, F.A.; Loss, D.; Myronov, M.; Zhang, J.-J.; De Franceschi, S.; Katsaros, G.; Veldhorst, M. The germanium quantum information route. Nat. Rev. Mater. 2020, 6, 926–943. [Google Scholar] [CrossRef]

- Hendrickx, N.W.; Veldhorst, M. An array of four germanium qubits. Nature 2021. [Google Scholar] [CrossRef]

- Kuo, M.H.; Wang, C.C.; Lai, W.T.; George, T.; Li, P.W. Designer Ge quantum dots on Si: A heterostructure configuration with enhanced optoelectronic performance. Appl. Phys. Lett. 2012, 101, 223107. [Google Scholar] [CrossRef]

- Liao, P.H.; Kuo, M.H.; Tien, C.W.; Chang, Y.L.; Hong, P.Y.; George, T.; Lin, H.C.; Li, P.W. In Proceedings of the Self-Organized Gate Stack of Ge Nanosphere/SiO2/Si1-xGex Enables Ge-Based Monolithically-Integrated Electronics and Photonics on Si Platform, Honolulu, HI, USA, 18–22 June 2018; pp. 157–158. [CrossRef]

- Huang, T.-L.; Peng, K.-P.; Chen, C.-L.; Lin, H.-C.; George, T.; Li, P.-W. Tunable diameter and spacing of double Ge quantum dots using highly-controllable spacers and selective oxidation of SiGe. Sci. Rep. 2019, 9, 1–8. [Google Scholar] [CrossRef] [Green Version]

- Peng, K.-P.; Chen, C.-L.; Tang, Y.-T.; Kuo, D.; George, T.; Lin, H.-C.; Li, P.-W. In Proceedings of the Self-Organized Pairs of Ge Double Quantum Dots with Tunable Sizes and Spacings Enable Room-Temperature Operation of Qubit and Single-Electron Devices, San Francisco, CA, USA, 7–11 December 2019. [CrossRef]

- Chen, K.-H.; Wang, C.-C.; George, T.; Li, P.-W. The role of Si interstitials in the migration and growth of Ge nanocrystallites under thermal annealing in an oxidizing ambient. Nanoscale Res. Lett. 2014, 9, 339. [Google Scholar] [CrossRef] [Green Version]

- George, T.; Li, P.W.; Chen, K.H.; Peng, K.P.; Lai, W.T. ‘Symbiotic’ semiconductors: Unusual and counter-intuitive Ge/Si/O interactions. J. Phys. D: Appl. Phys. 2017, 50, 105101. [Google Scholar] [CrossRef]

- Chen, K.H.; Wang, C.C.; George, T.; Li, P.W. The pivotal role of SiO formation in the migration and Ostwald ripening of Ge quantum dots. Appl. Phys. Lett. 2014, 105, 122102. [Google Scholar] [CrossRef]

- Chen, G.-L.; Kuo, D.M.T.; Lai, W.-T.; Li, P.-W. Tunneling spectroscopy of a germanium quantum dot in single-hole transistors with self-aligned electrodes. Nanotechnology 2007, 18. [Google Scholar] [CrossRef]

- Chen, I.-H.; Chen, K.-H.; Lai, W.-T.; Li, P.-W. Single Germanium Quantum-dot Placement Along With Self-Aligned Electrodes for Effective Management of Single Charge Tunneling. IEEE Trans. Electron Devices 2012, 59, 3224–3230. [Google Scholar] [CrossRef]

- Chen, I.H.; Lai, W.T.; Li, P.W. Realization of solid-state nanothermometer using Ge quantum-dot single-hole transistor in few-hole regime. Appl. Phys. Lett. 2014, 104, 243506. [Google Scholar] [CrossRef]

- Chen, K.-H.; Chien, C.-Y.; Li, P.-W. Precise Ge quantum dot placement for quantum tunneling devices. Nanotechnology 2009, 21, 055302. [Google Scholar] [CrossRef] [PubMed]

- Liao, P.H.; Hsu, T.C.; Chen, K.H.; Cheng, T.H.; Hsu, T.M.; Wang, C.C.; George, T.; Li, P.W. Size-tunable strain engineering in Ge nanocrystals embedded within SiO2 and Si3N4. Appl. Phys. Letts. 2014, 105, 172106. [Google Scholar] [CrossRef]

- Kuo, Y.-H.; Chiu, S.-H.; Tien, C.-W.; Lin, S.-D.; Chang, W.-H.; George, T.; Lin, H.-C.; Li, P.-W. Nitride-stressor and quantum-size engineering in Ge quantum-dot photoluminescence wavelength and exciton lifetime. Nano Futur. 2020, 4, 015001. [Google Scholar] [CrossRef]

- Kuo, M.H.; Chou, S.K.; Pan, Y.W.; Lin, S.D.; George, T.; Li, P.W. “Embedded Emitters”: Direct bandgap Ge nanodots within SiO2. J. Appl. Phys. 2016, 120, 233106. [Google Scholar] [CrossRef]

- Peng, K.-P.; Kuo, Y.-H.; Chang, L.-H.; Hsiao, C.-N.; Chung, T.-F.; George, T.; Lin, H.-C.; Li, P.-W. Silicon nitride engineering: Role of hydrogen-bonding in Ge quantum dot formation. Semicond. Sci. Technol. 2020, 35, 105018. [Google Scholar] [CrossRef]

- Gurvich, L.V.; Iorish, V.S.; Yungman, V.S.; Dorofeeva, O.V. Thermodynamic Properties as a Function of Temperature. In CRC Handbook of Chemistry and Physics, 84th ed.; Lide, D.R., Ed.; CRC Press: Boca Raton, FL, USA, 2003; pp. 575–584. [Google Scholar]

- Chien, C.Y.; Chang, Y.J.; Chen, K.H.; Lai, W.T.; George, T.; Scherer, A.; Li, P.W. Nanoscale, catalytically enhanced local oxidation of silicon-containing layers by ’burrowing’ Ge quantum dots. Nanotechnology 2011, 22, 435602. [Google Scholar] [CrossRef] [PubMed]

- Peng, K.-P.; Huang, T.-L.; George, T.; Lin, H.-C.; Li, P.-W.; George, T. Ge nanodot-mediated densification and crystallization of low-pressure chemical vapor deposited Si3N4 for advanced complementary metal-oxide-semiconductor photonics and electronics applications. Nanotechnology 2019, 30, 405201. [Google Scholar] [CrossRef] [PubMed]

- Lai, W.T.; Yang, K.C.; Liao, P.H.; George, T.; Li, P.W. Gate-stack engineering for self-organized Ge-dot/SiO2/SiGe-shell MOS capacitors. Frontiers in Materials 2016, 3, 00005. [Google Scholar] [CrossRef] [Green Version]

- Chen, H.-Y.; Peng, K.-P.; George, T.; Lin, H.-C.; Li, P.-W. Coordinated and Simultaneous Formation of Paired Ge Quantum Dots by Thermal Oxidation of Designer Poly-SiGe Spacer Structures. IEEE Trans. Nanotechnol. 2020, 19, 436–438. [Google Scholar] [CrossRef]

- Stekolnikov, A.A.; Bechstedt, F. Shape of free and constrained group-IV crystallites: Influence of surface energies. Phys. Rev. B 2005, 72, 125326. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, I.-H.; Hong, P.-Y.; Peng, K.-P.; Lin, H.-C.; George, T.; Li, P.-W. Germanium Quantum-Dot Array with Self-Aligned Electrodes for Quantum Electronic Devices. Nanomaterials 2021, 11, 2743. https://0-doi-org.brum.beds.ac.uk/10.3390/nano11102743

Wang I-H, Hong P-Y, Peng K-P, Lin H-C, George T, Li P-W. Germanium Quantum-Dot Array with Self-Aligned Electrodes for Quantum Electronic Devices. Nanomaterials. 2021; 11(10):2743. https://0-doi-org.brum.beds.ac.uk/10.3390/nano11102743

Chicago/Turabian StyleWang, I-Hsiang, Po-Yu Hong, Kang-Ping Peng, Horng-Chih Lin, Thomas George, and Pei-Wen Li. 2021. "Germanium Quantum-Dot Array with Self-Aligned Electrodes for Quantum Electronic Devices" Nanomaterials 11, no. 10: 2743. https://0-doi-org.brum.beds.ac.uk/10.3390/nano11102743