Low Power Design for Future Wearable and Implantable Devices

Abstract

:1. Introduction

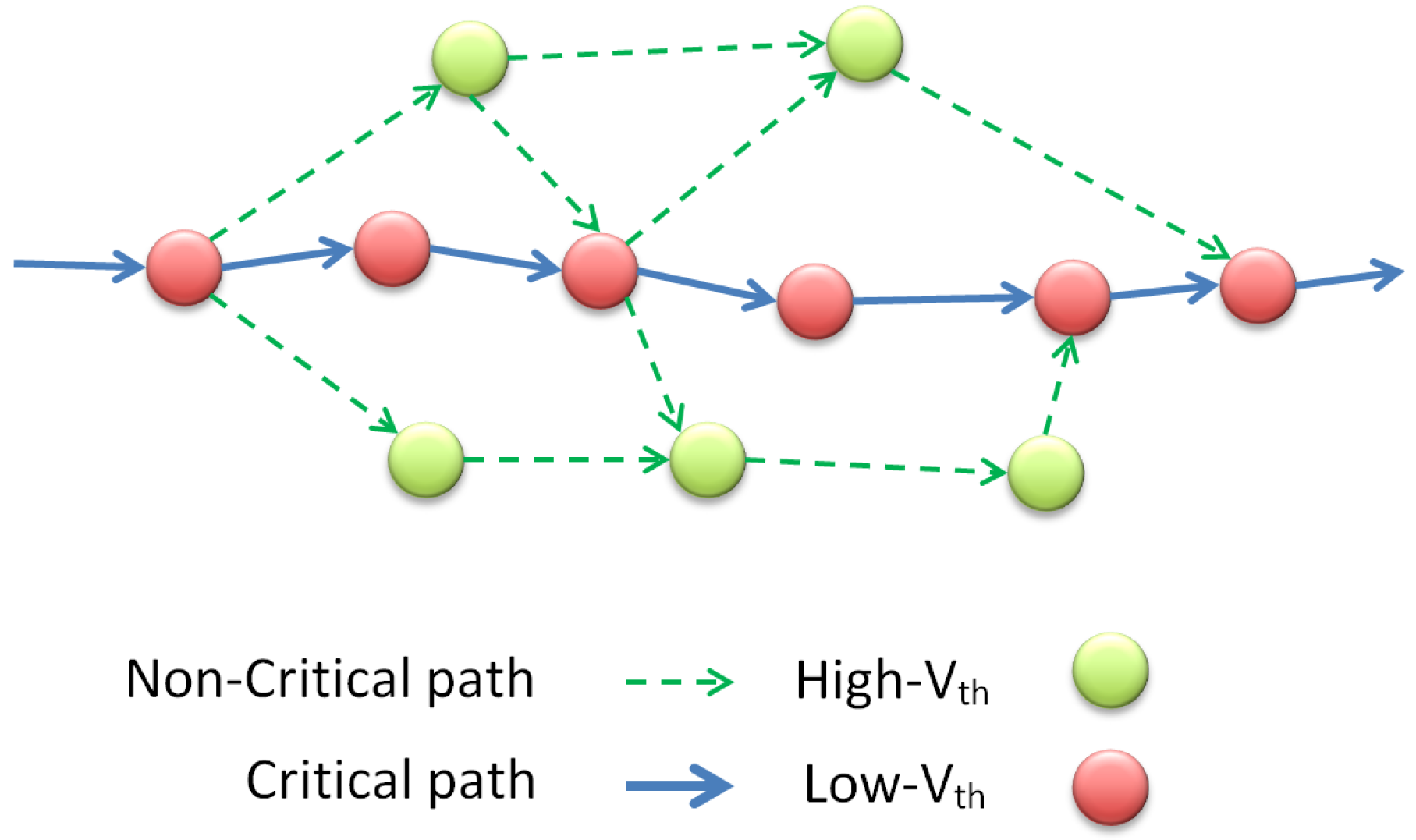

2. Low Power Digital Circuit Design

2.1. Circuit Techniques

2.2. Device Scaling

Performance of Bulk CMOS versus FinFET

2.3. Device Circuit Co-Design

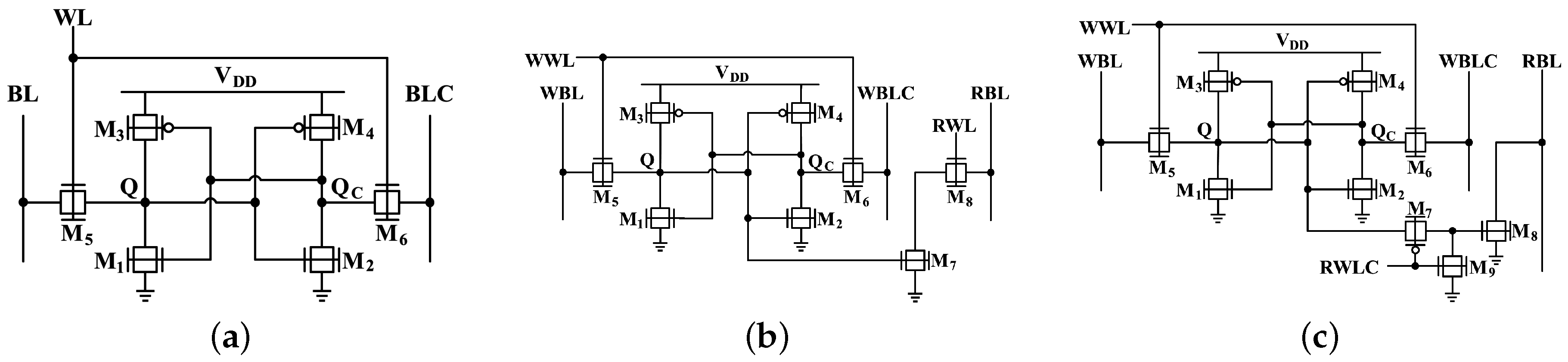

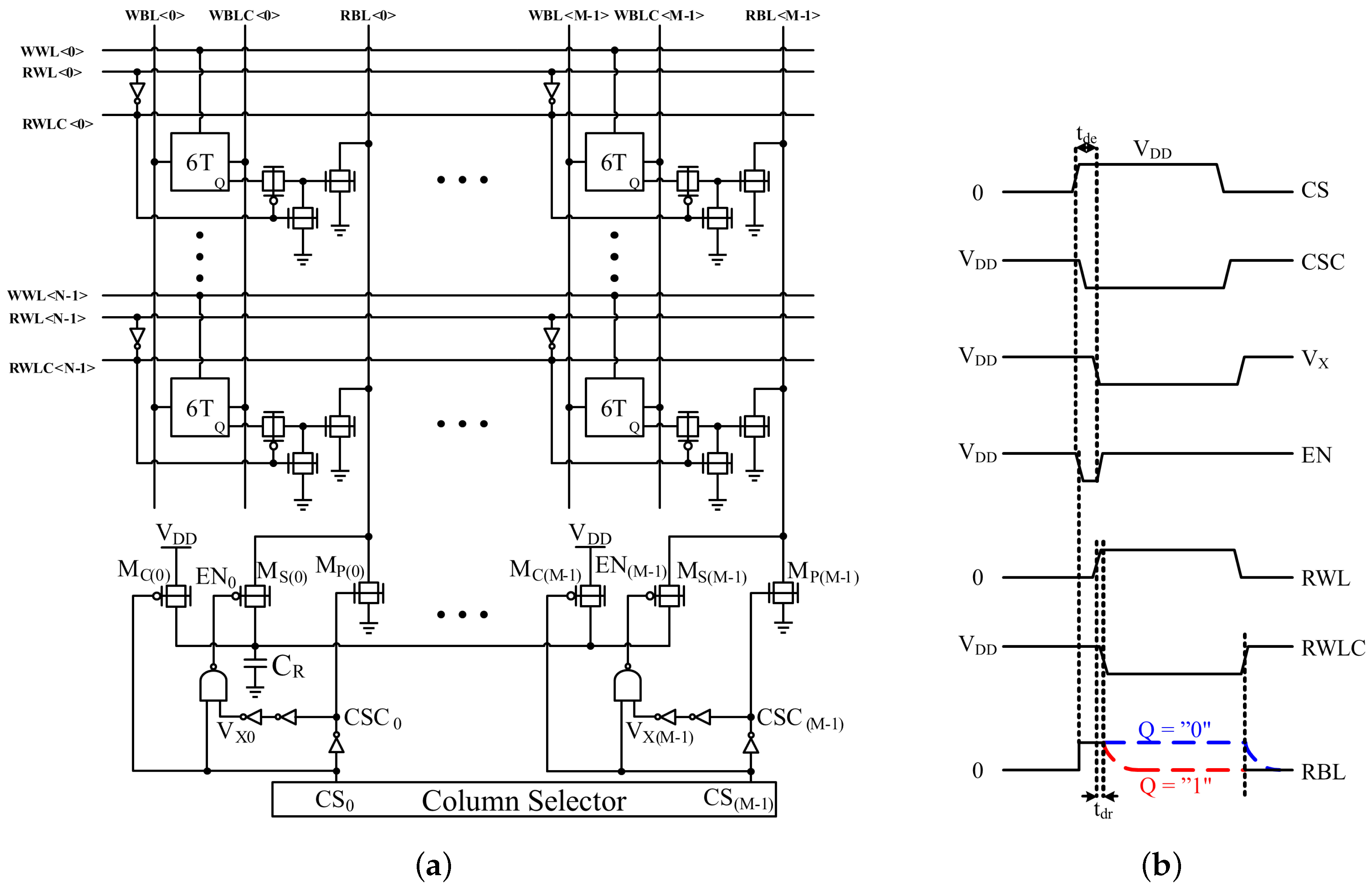

2.4. FinFET-Based SRAM

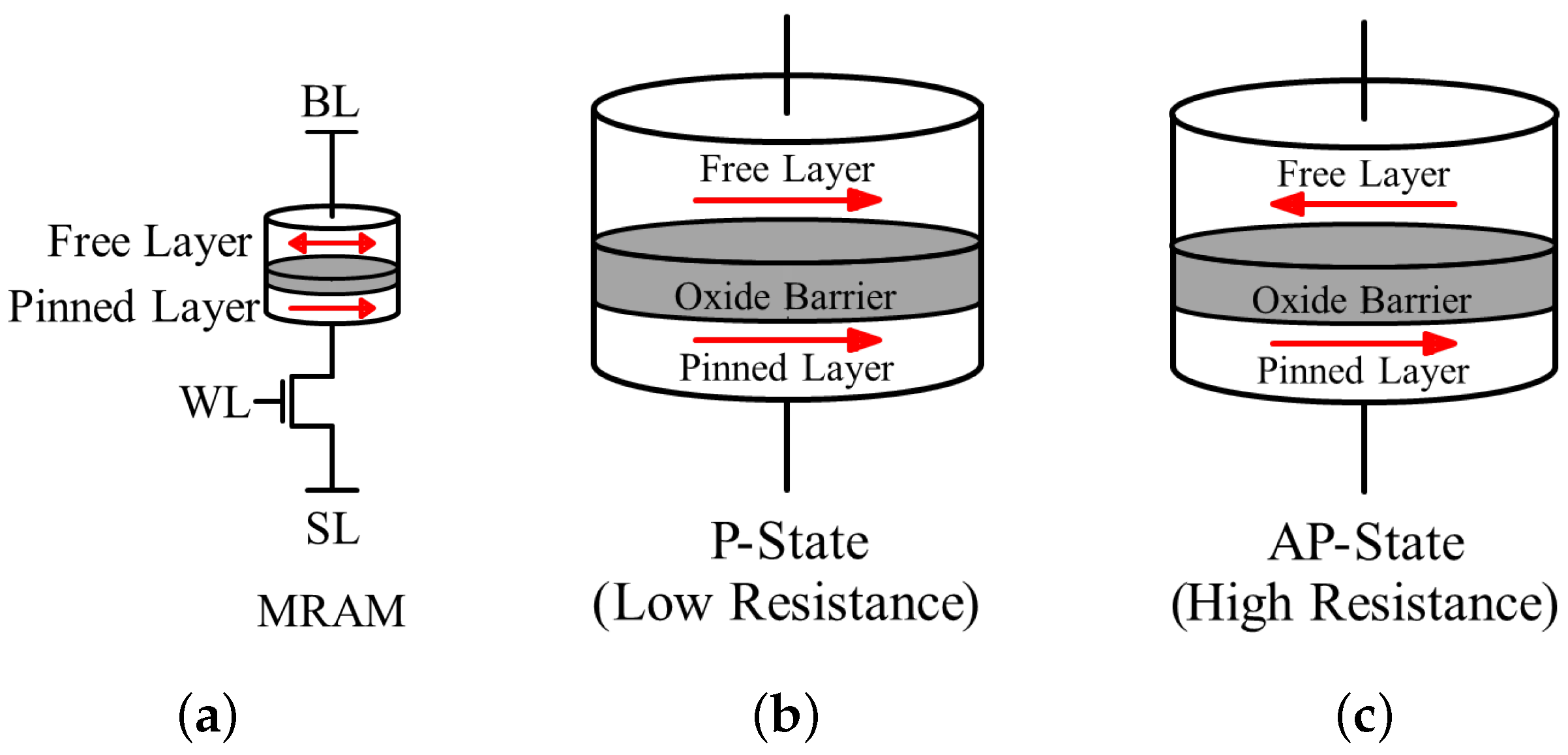

2.5. STT-RAM

3. Low Power Analog Design

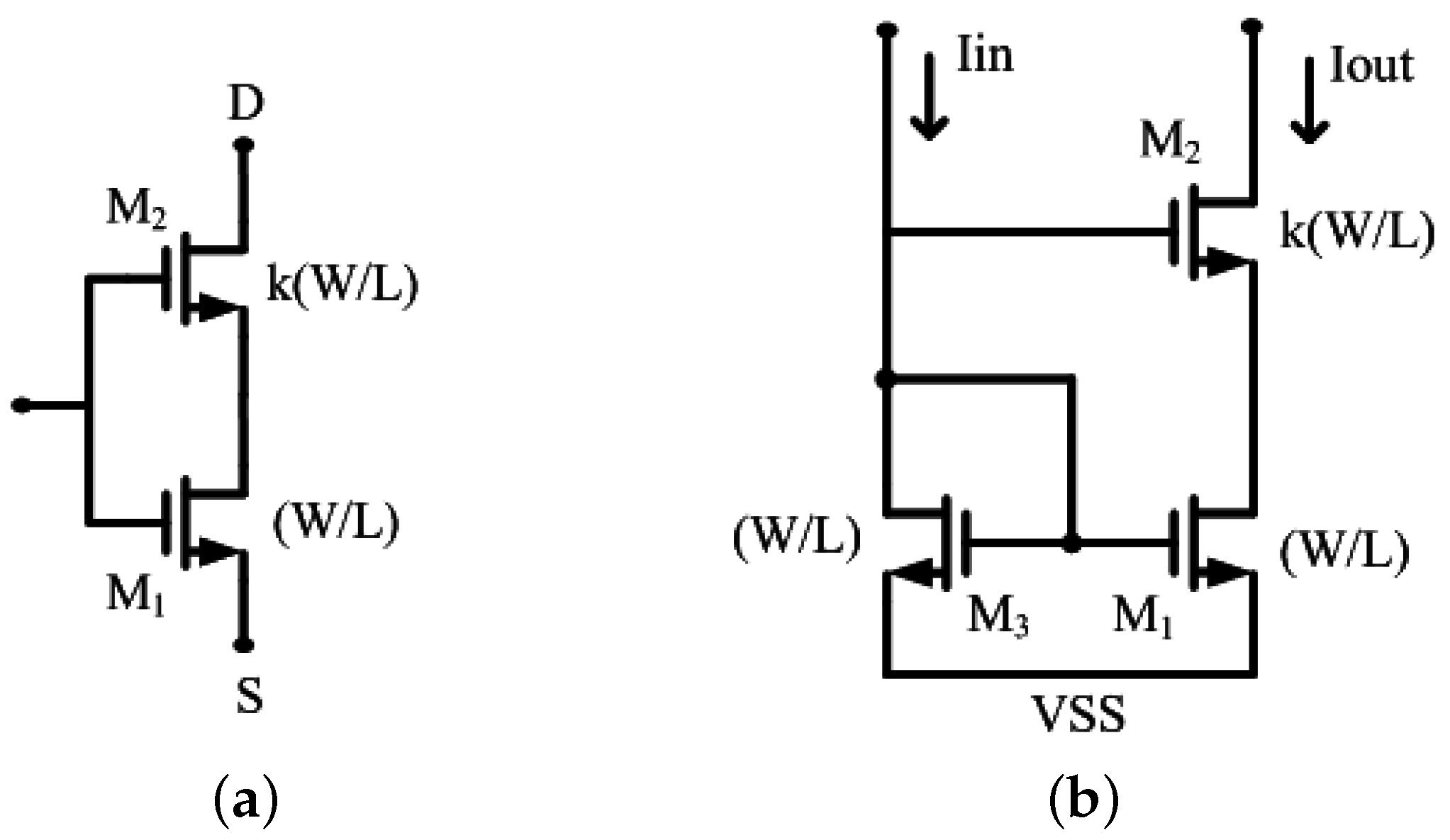

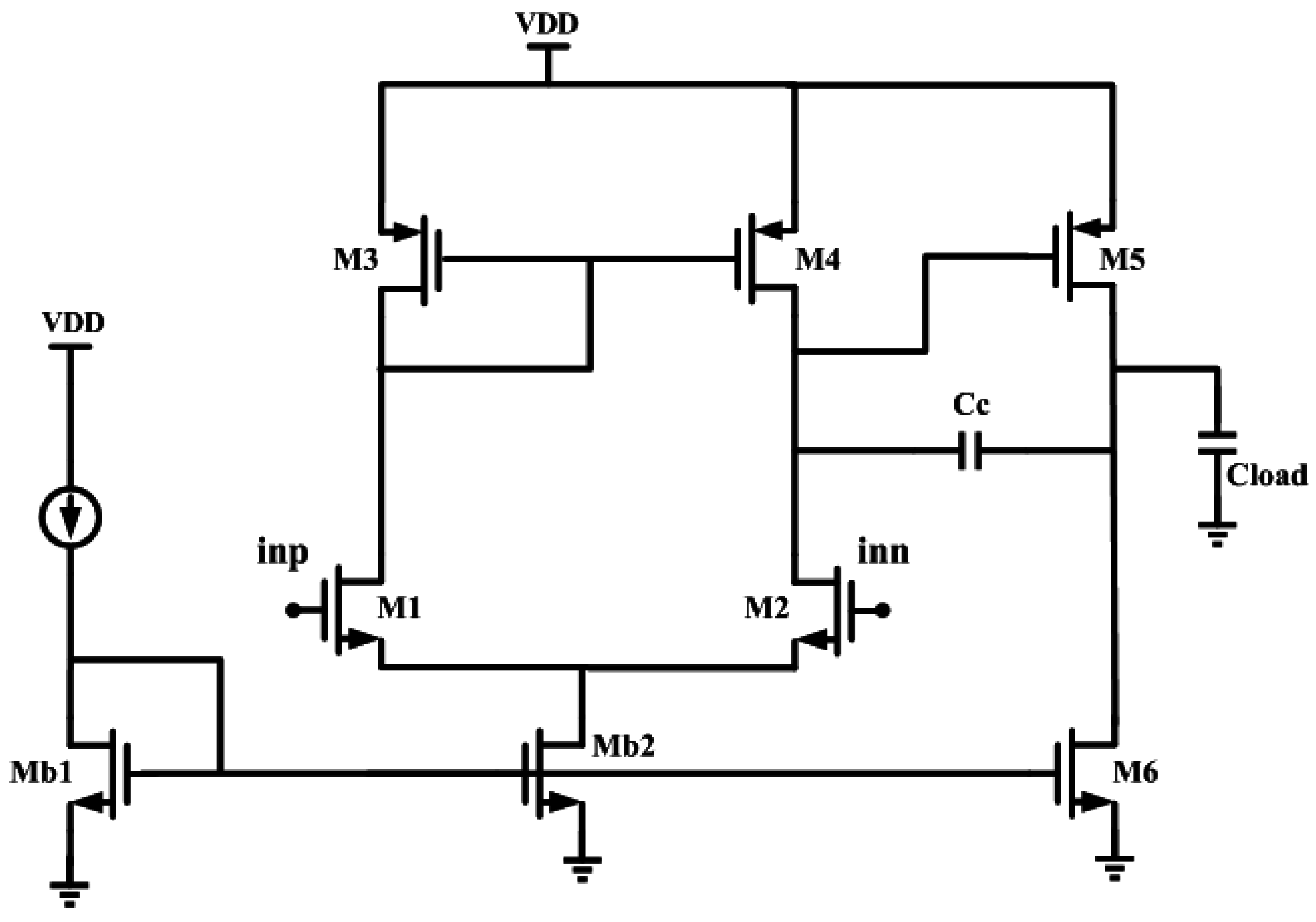

3.1. Low Voltage Design Techniques

3.2. Analog Cells in FinFET Technology

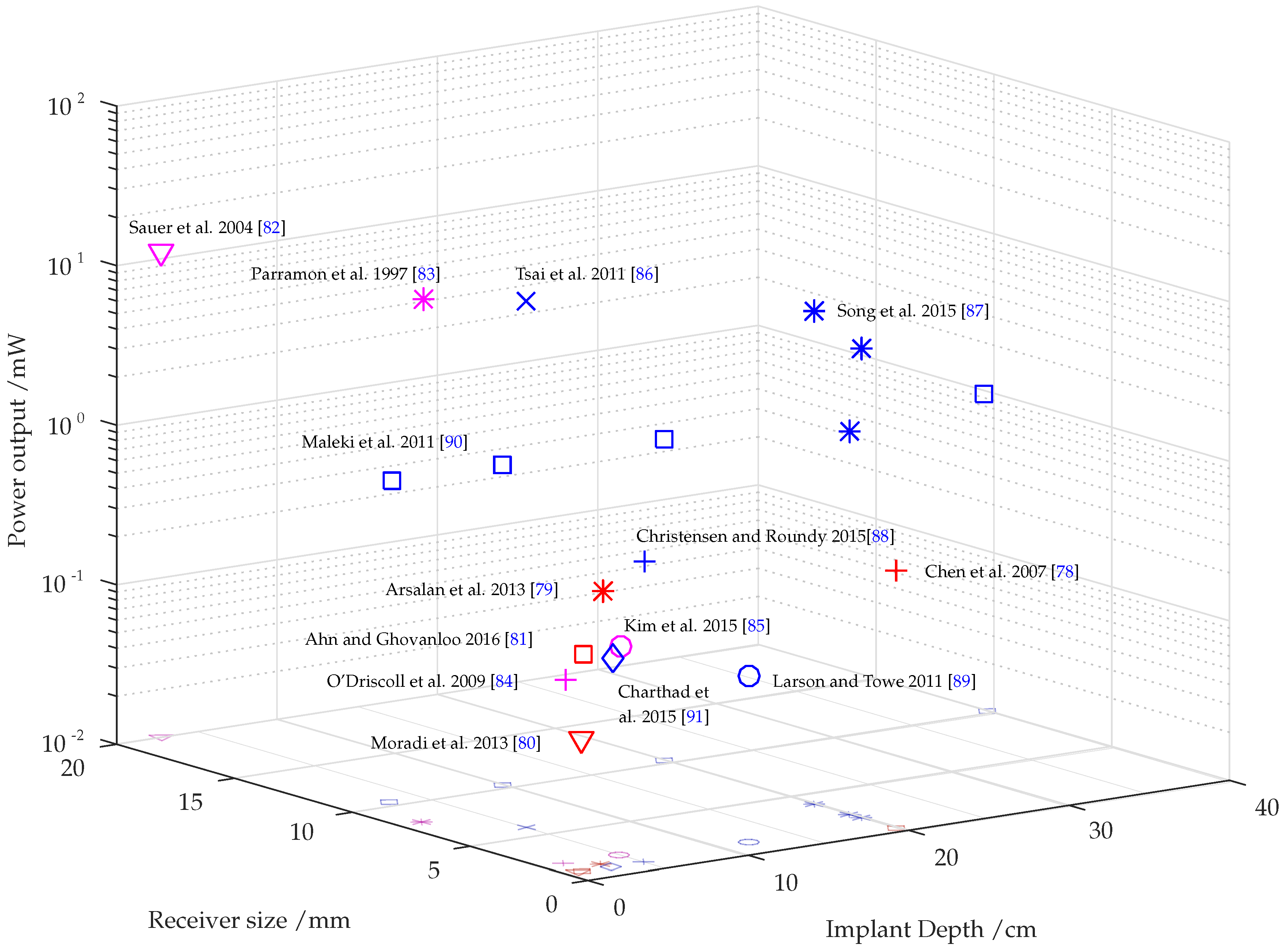

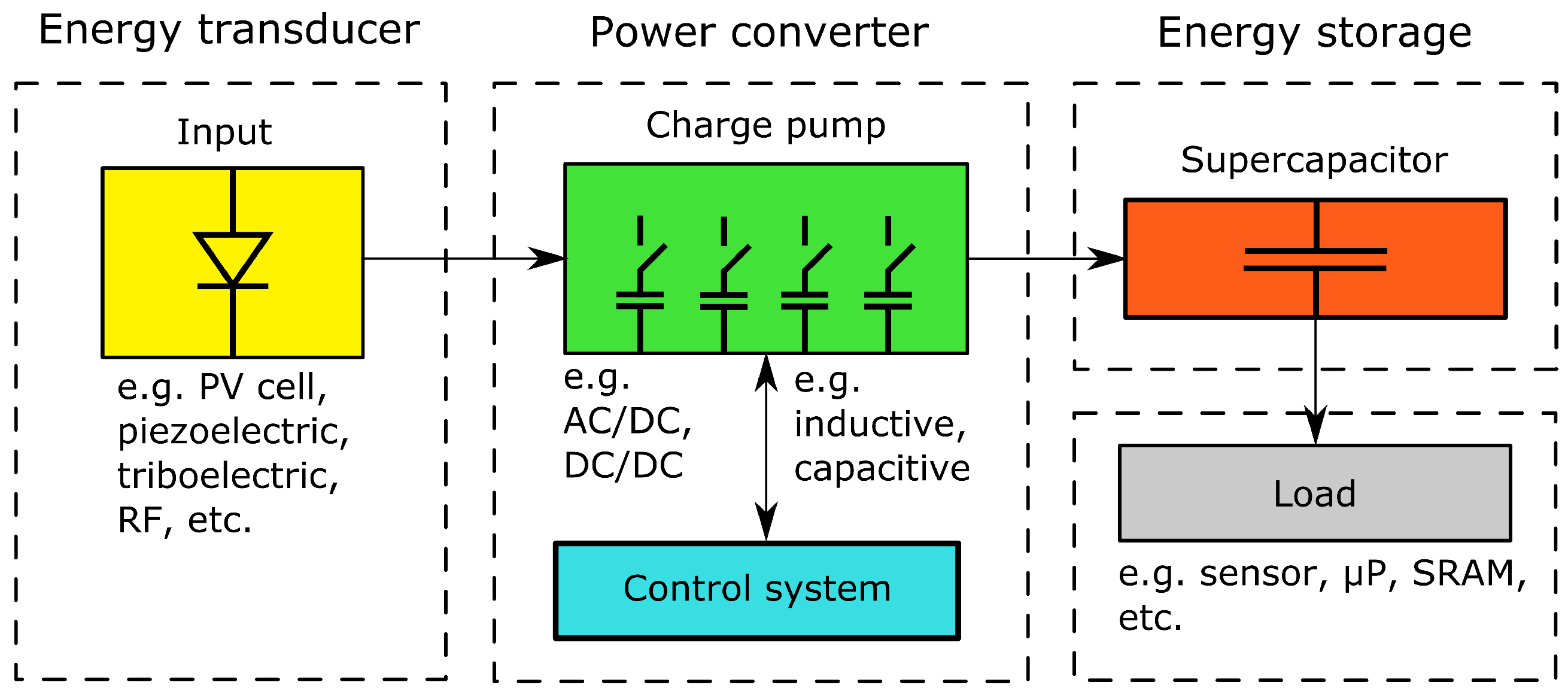

4. Energy Harvesting

4.1. Techniques and Sources

4.1.1. Solar Energy

4.1.2. Mechanical Energy

4.1.3. Combinations of Energy Harvesters

4.2. Energy Harvesting Interfaces

Power Converters

4.3. Sustainable Operation Using Ambient Energy

5. Conclusions

Author Contributions

Conflicts of Interest

Abbreviations

| WID | Wearable/Implantable Device |

| TEG | Thermoelectric Generator |

| IC | Integrated Circuit |

| SoC | System-on-Chip |

| SCE | Short Channel Effect |

| RF | Radio frequency |

| IoT | Internet of Things |

| IoBNT | Internet of Bio-Nano Things |

| MuGFET | Multi-Gate Field-Effect Transistor |

| CNT-FET | Carbon Nanotube Field-Effect Transistor |

| RDF | Random Dopant Fluctuation |

| EOT | Equivalent Gate Dielectric Thickness |

| PTM | Predective Technology Model |

| DIBL | Drain Induced Barrier Lowering |

| SS | Sub-threshold Swing |

| SRAM | Static Random Access Memory |

| WL | Word-line |

| BL | Bit-line |

| SL | Source-line |

| RBL | Read Bit-line |

| RWL | Read Word-line |

| RWLC | Read Word-line Complementary |

| CS | Column Select |

| EN | Enable Signal |

| RSNM | Read Static Noise Margin |

| WM | Write Margin |

| SA | Sense Amplifier |

| STT-RAM | Spin Transfer Torque Random Access Memory |

| MTJ | Magnetic Tunnel Junction |

| SNR | Signal-to-Noise Ratio |

| DR | Dynamic Range |

| OPAMP | Operational Amplifier |

| EEG | Electroencephalogram |

| ECG | Electrocardiography |

| ADC | Analog-to-Digital Converter |

| AFE | Analog Front-End |

| CLS | Correlated Level Shifting |

| CB | Comparator Based |

| NREL | National Renewable Energy Laboratory |

| SCVR | Switched Capacitor Voltage Regulator |

| PZT | Lead Zirconate Titanate |

| US | Ultrasonic |

| PENG | Piezoelectric Nano-Generator |

| TENG | Triboelectric Nano-Generator |

| PV | Photovoltaic |

| CIGS | Copper Indium Gallium Selenide |

| AM | Air Mass |

| MEMS | Microelectromechanical System |

| FHNG | Flexible Hybrid Nanogenerator |

References

- Pal, A. Low-Power VLSI Circuits and Systems; Springer: New Delhi, India, 2014. [Google Scholar]

- Akyildiz, I.F.; Pierobon, M.; Balasubramaniam, S.; Koucheryavy, Y. The internet of Bio-Nano things. IEEE Commun. Mag. 2015, 53, 32–40. [Google Scholar] [CrossRef]

- Pedram, M. Power Minimization in IC Design: Principles and Applications. ACM Trans. Des. Autom. Electron. Syst. 1996, 1, 3–56. [Google Scholar] [CrossRef]

- Chandrakasan, A.P.; Sheng, S.; Brodersen, R.W. Low-power CMOS digital design. IEEE J. Solid-State Circuits 1992, 27, 473–484. [Google Scholar] [CrossRef]

- Athas, W.C.; Svensson, L.J.; Koller, J.G.; Tzartzanis, N.; Chou, E.Y.C. Low-power digital systems based on adiabatic-switching principles. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 1994, 2, 398–407. [Google Scholar] [CrossRef]

- Wuytack, S.; Catthoor, F.; Franssen, F.; Nachtergaele, L.; De Man, H. Global communication and memory optimizing transformations for low power systems. In Proceedings of the IEEE International Workshop on Low Power Design, Napa Valley, CA, USA, 24–27 April 1994; pp. 203–208.

- Tiwari, V.; Malik, S.; Wolfe, A. Power analysis of embedded software: A first step towards software power minimization. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 1994, 2, 437–445. [Google Scholar] [CrossRef]

- Collaert, N.; Keersgieter, A.D.; Dixit, A.; Ferain, I.; Lai, L.S.; Lenoble, D.; Mercha, A.; Nackaerts, A.; Pawlak, B.J.; Rooyackers, R.; et al. Multi-gate devices for the 32 nm technology node and beyond. In Proceedings of the 37th European Solid State Device Research Conference, Muenchen, Germany, 11–13 September 2007; pp. 143–146.

- Noda, K.; Tatsumi, T.; Uchida, T.; Nakajima, K.; Miyamoto, H.; Hu, C. A 0.1-μm delta-doped MOSFET fabricated with post-low-energy implanting selective epitaxy. IEEE Trans. Electron Devices 1998, 45, 809–814. [Google Scholar] [CrossRef]

- Yan, R.H.; Ourmazd, A.; Lee, K.F. Scaling the Si MOSFET: From bulk to SOI to bulk. IEEE Trans. Electron Devices 1992, 39, 1704–1710. [Google Scholar] [CrossRef]

- Sachid, A.B.; Hu, C. Denser and More Stable SRAM Using FinFETs With Multiple Fin Heights. IEEE Trans. Electron Devices 2012, 59, 2037–2041. [Google Scholar] [CrossRef]

- Tawfik, S.A.; Kursun, V. Multi-Threshold Voltage FinFET Sequential Circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2011, 19, 151–156. [Google Scholar] [CrossRef]

- Moradi, F.; Gupta, S.K.; Panagopoulos, G.; Wisland, D.T.; Mahmoodi, H.; Roy, K. Asymmetrically Doped FinFETs for Low-Power Robust SRAMs. IEEE Trans. Electron Devices 2011, 58, 4241–4249. [Google Scholar] [CrossRef]

- Predictive Technology Model (PTM). Available online: http://ptm.asu.edu (accessed on 17 October 2016).

- Lin, C.H.; Haensch, W.; Oldiges, P.; Wang, H.; Williams, R.; Chang, J.; Guillorn, M.; Bryant, A.; Yamashita, T.; Standaert, T.; et al. Modeling of width-quantization-induced variations in logic FinFETs for 22 nm and beyond. In Proceedings of the Symposium on VLSI Technology (VLSIT), Kyoto, Japan, 14–16 June 2011; pp. 16–17.

- Gu, J.; Keane, J.; Sapatnekar, S.; Kim, C. Width Quantization Aware FinFET Circuit Design. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 10–13 September 2006; pp. 337–340.

- Hsieh, C.Y.; Fan, M.L.; Hu, V.P.H.; Su, P.; Chuang, C.T. Independently-Controlled-Gate FinFET Schmitt Trigger Sub-Threshold SRAMs. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2012, 20, 1201–1210. [Google Scholar] [CrossRef]

- Liu, Z.; Tawfik, S.A.; Kursun, V. An independent-gate FinFET SRAM cell for high data stability and enhanced integration density. In Proceedings of the IEEE International SOC Conference, Hsin Chu, Taiwan, 26–29 September 2007; pp. 63–66.

- Kim, Y.B.; Kim, Y.B.; Lombardi, F. Low power 8T SRAM using 32 nm independent gate FinFET technology. In Proceedings of the IEEE International SOC Conference, Newport Beach, CA, USA, 17–20 September 2008; pp. 247–250.

- Chen, Y.H.; Chan, W.M.; Wu, W.C.; Liao, H.J.; Pan, K.H.; Liaw, J.J.; Chung, T.H.; Li, Q.; Lin, C.Y.; Chiang, M.C.; et al. A 16 nm 128 Mb SRAM in High-κ Metal-Gate FinFET Technology with Write-Assist Circuitry for Low-VMIN Applications. IEEE J. Solid-State Circuits 2015, 50, 170–177. [Google Scholar] [CrossRef]

- Karl, E.; Wang, Y.; Ng, Y.G.; Guo, Z.; Hamzaoglu, F.; Meterelliyoz, M.; Keane, J.; Bhattacharya, U.; Zhang, K.; Mistry, K.; et al. A 4.6 GHz 162 Mb SRAM Design in 22 nm Tri-Gate CMOS Technology with Integrated Read and Write Assist Circuitry. IEEE J. Solid-State Circuits 2013, 48, 150–158. [Google Scholar] [CrossRef]

- Lien, N.C.; Chu, L.W.; Chen, C.H.; Yang, H.I.; Tu, M.H.; Kan, P.S.; Hu, Y.J.; Chuang, C.T.; Jou, S.J.; Hwang, W. A 40 nm 512 kb Cross-Point 8 T Pipeline SRAM with Binary Word-Line Boosting Control, Ripple Bit-Line and Adaptive Data-Aware Write-Assist. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 3416–3425. [Google Scholar] [CrossRef]

- Raychowdhury, A.; Geuskens, B.; Kulkarni, J.; Tschanz, J.; Bowman, K.; Karnik, T.; Lu, S.L.; De, V.; Khellah, M.M. PVT-and-aging adaptive wordline boosting for 8T SRAM power reduction. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), Francisco, CA, USA, 7–11 February 2010; pp. 352–353.

- Verma, N.; Chandrakasan, A.P. A 256 kb 65 nm 8T Subthreshold SRAM Employing Sense-Amplifier Redundancy. IEEE J. Solid-State Circuits 2008, 43, 141–149. [Google Scholar] [CrossRef]

- Zeinali, B.; Madsen, J.K.; Raghavan, P.; Moradi, F. Sub-Threshold SRAM Design in 14 Nm FinFET Technology with Improved Access Time and Leakage Power. In Proceedings of the IEEE Computer Society Annual Symposium on VLSI, Montpellier, France, 8–10 July 2015; pp. 74–79.

- Rajput, S.S.; Jamuar, S.S. Low voltage analog circuit design techniques. IEEE Circuits Syst. Mag. 2002, 2, 24–42. [Google Scholar] [CrossRef]

- Huai, Y. Spin-transfer torque MRAM (STT-MRAM): Challenges and prospects. AAPPS Bull. 2008, 18, 33–40. [Google Scholar]

- Farkhani, H.; Peiravi, A.; Moradi, F. Low-Energy Write Operation for 1T-1MTJ STT-RAM Bitcells with Negative Bitline Technique. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 1593–1597. [Google Scholar] [CrossRef]

- Fong, X.; Kim, Y.; Choday, S.H.; Roy, K. Failure Mitigation Techniques for 1T-1MTJ Spin-Transfer Torque MRAM Bit-cells. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 384–395. [Google Scholar] [CrossRef]

- Zheng, T.; Park, J.; Orshansky, M.; Erez, M. Variable-energy write STT-RAM architecture with bit-wise write-completion monitoring. In Proceedings of the IEEE International Symposium on Low Power Electronics and Design (ISLPED), Beijing, China, 4–6 September 2013; pp. 229–234.

- Bi, X.; Sun, Z.; Li, H.; Wu, W. Probabilistic design methodology to improve run-time stability and performance of STT-RAM caches. In Proceedings of the IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 5–8 November 2012; pp. 88–94.

- Zhou, P.; Zhao, B.; Yang, J.; Zhang, Y. Energy reduction for STT-RAM using early write termination. In Proceedings of the IEEE/ACM International Conference on Computer-Aided Design—Digest of Technical Papers, Prague, Czech Republic, 11–14 October 2009; pp. 264–268.

- Bishnoi, R.; Ebrahimi, M.; Oboril, F.; Tahoori, M.B. Asynchronous Asymmetrical Write Termination (AAWT) for a low power STT-MRAM. In Proceedings of the Design, Automation Test in Europe Conference Exhibition (DATE), Dresden, Germany, 24–28 March 2014.

- Jeong, G.; Cho, W.; Ahn, S.; Jeong, H.; Koh, G.; Hwang, Y.; Kim, K. A 0.24-μm 2.0-V 1T1MTJ 16-kb nonvolatile magnetoresistance RAM with self-reference sensing scheme. IEEE J. Solid-State Circuits 2003, 38, 1906–1910. [Google Scholar] [CrossRef]

- Chen, Y.; Li, H.; Wang, X.; Zhu, W.; Xu, W.; Zhang, T. A 130 nm 1.2 V/3.3 V 16 Kb Spin-Transfer Torque Random Access Memory With Nondestructive Self-Reference Sensing Scheme. IEEE J. Solid-State Circuits 2012, 47, 560–573. [Google Scholar] [CrossRef]

- Motaman, S.; Ghosh, S.; Kulkarni, J.P. A novel slope detection technique for robust STTRAM sensing. In Proceedings of the IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), Rome, Italy, 22–24 July 2015; pp. 7–12.

- Chen, W.M.; Chiueh, H.; Chen, T.J.; Ho, C.L.; Jeng, C.; Ker, M.D.; Lin, C.Y.; Huang, Y.C.; Chou, C.W.; Fan, T.Y.; et al. A Fully Integrated 8-Channel Closed-Loop Neural-Prosthetic CMOS SoC for Real-Time Epileptic Seizure Control. IEEE J. Solid-State Circuits 2014, 49, 232–247. [Google Scholar] [CrossRef]

- Yoo, J.; Yan, L.; El-Damak, D.; Altaf, M.A.B.; Shoeb, A.H.; Chandrakasan, A.P. An 8-Channel Scalable EEG Acquisition SoC With Patient-Specific Seizure Classification and Recording Processor. IEEE J. Solid-State Circuits 2013, 48, 214–228. [Google Scholar] [CrossRef]

- Altaf, M.A.B.; Tillak, J.; Kifle, Y.; Yoo, J. A 1.83 μJ/classification nonlinear support-vector-machine-based patient-specific seizure classification SoC. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 100–101.

- Cao, T.V.; Maier, C.; Wisland, D.; Lande, T.S.; Cauwenberghs, G. BFSK MICS direct-DCO transmitter with adaptive background frequency regulation. In Proceedings of the 38th European Solid State Circuits Conference (ESSCIRC), Bordeaux, France, 17–21 September 2012; pp. 305–308.

- Verma, N.; Shoeb, A.; Bohorquez, J.; Dawson, J.; Guttag, J.; Chandrakasan, A.P. A Micro-Power EEG Acquisition SoC With Integrated Feature Extraction Processor for a Chronic Seizure Detection System. IEEE J. Solid-State Circuits 2010, 45, 804–816. [Google Scholar] [CrossRef]

- Low-Cost Low-Power 2.4 GHz RF Transmitter. Available online: http://focus.ti.com/docs/prod/folders/print/cc2550.html (accessed on 17 October 2016).

- Ismail, M.; Fiez, T. Analog VLSI: Signal and Information Processing; Electronics and VLSI Circuits; McGraw-Hill: New York, NY, USA, 1994. [Google Scholar]

- Rajput, S.S.; Jamuar, S.S. Low voltage analog circuit design techniques. IEEE Circuits and Systems Magazine 2002, 2, 24–42. [Google Scholar] [CrossRef]

- Gregoire, B.R.; Moon, U.K. An Over-60 dB True Rail-to-Rail Performance Using Correlated Level Shifting and an Opamp With Only 30 dB Loop Gain. IEEE J. Solid-State Circuits 2008, 43, 2620–2630. [Google Scholar] [CrossRef]

- Fiorenza, J.K.; Sepka, T.; Holloway, P.; Sodini, C.G.; Lee, H.S. Comparator-Based Switched-Capacitor Circuits for Scaled CMOS Technologies. IEEE J. Solid-State Circuits 2006, 41, 2658–2668. [Google Scholar] [CrossRef]

- Blalock, B.J.; Allen, P.E.; Rincon-Mora, G.A. Designing 1-V op amps using standard digital CMOS technology. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 1998, 45, 769–780. [Google Scholar] [CrossRef]

- Rajput, S.S.; Jamuar, S.S. Design Techniques for Low Voltage Analog Circuit Structures. In Proceedings of the 2001 IEEE National Symposium On Microelectronics, Genting Highlands, Malaysia, 12–13 November 2001.

- Yan, S.; Sanchez-Siencio, E. Low Voltage Analog Circuit Design Techniques: A Tutorial. IEICE Trans. Analog Integr. Circuits Syst. 2000, 82, 179–195. [Google Scholar]

- Hanson, S.; Zhai, B.; Seok, M.; Cline, B.; Zhou, K.; Singhal, M.; Minuth, M.; Olson, J.; Nazhandali, L.; Austin, T.; et al. Exploring Variability and Performance in a Sub-200-mV Processor. IEEE J. Solid-State Circuits 2008, 43, 881–891. [Google Scholar] [CrossRef]

- Kim, T.H.; Liu, J.; Keane, J.; Kim, C.H. A 0.2 V, 480 kb Subthreshold SRAM with 1 k Cells per Bitline for Ultra-Low-Voltage Computing. IEEE J. Solid-State Circuits 2008, 43, 518–529. [Google Scholar] [CrossRef]

- Ueno, K.; Hirose, T.; Asai, T.; Amemiya, Y. A 300 nW, 15 ppm/°C, 20 ppm/V CMOS Voltage Reference Circuit Consisting of Subthreshold MOSFETs. IEEE J. Solid-State Circuits 2009, 44, 2047–2054. [Google Scholar] [CrossRef]

- Lee, J.; Cho, S. A 210 nW 29.3 ppm/°C 0.7 V voltage reference with a temperature range of -50 to 130 °C in 0.13 μm CMOS. In Proceedings of the Symposium on VLSI Circuits (VLSIC), Kyoto, Japan, 15–17 June 2011; pp. 278–279.

- Giustolisi, G.; Palumbo, G.; Criscione, M.; Cutri, F. A low-voltage low-power voltage reference based on subthreshold MOSFETs. IEEE J. Solid-State Circuits 2003, 38, 151–154. [Google Scholar] [CrossRef]

- Vita, G.D.; Iannaccone, G. An ultra-low-power, temperature compensated voltage reference generator. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 18–21 September 2005; pp. 751–754.

- Magnelli, L.; Crupi, F.; Corsonello, P.; Pace, C.; Iannaccone, G. A 2.6 nW, 0.45 V Temperature-Compensated Subthreshold CMOS Voltage Reference. IEEE J. Solid-State Circuits 2011, 46, 465–474. [Google Scholar] [CrossRef]

- Seok, M.; Kim, G.; Blaauw, D.; Sylvester, D. A Portable 2-Transistor Picowatt Temperature-Compensated Voltage Reference Operating at 0.5 V. IEEE J. Solid-State Circuits 2012, 47, 2534–2545. [Google Scholar] [CrossRef]

- Zhang, H.; Huang, M.; Zhang, Y.; Li, X.; Yoshihara, T. A nano-power switched-capacitor voltage reference using body effect in MOSFETs for application in subthreshold LSI. In Proceedings of the IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), Hong Kong, China, 3–5 June 2013.

- Wambacq, P.; Verbruggen, B.; Scheir, K.; Borremans, J.; Heyn, V.D.; Plas, G.V.D.; Mercha, A.; Parvais, B.; Subramanian, V.; Jurczak, M.; et al. Analog and RF circuits in 45 nm CMOS and below: Planar bulk versus FinFET. In Proceedings of the 32nd European Solid-State Circuits Conference, Montreux, Switzerland, 19–21 September 2006; pp. 54–57.

- Borremans, J.; Parvais, B.; Dehan, M.; Thijs, S.; Wambacq, P.; Mercha, A.; Kuijk, M.; Carchon, G.; Decoutere, S. Perspective of RF design in future planar and FinFET CMOS. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium, Atlanta, GA, USA, 15–17 June 2008; pp. 75–78.

- Raskin, J.P.; Pailloncy, G.; Lederer, D.; Danneville, F.; Dambrine, G.; Decoutere, S.; Mercha, A.; Parvais, B. High-Frequency Noise Performance of 60-nm Gate-Length FinFETs. IEEE Trans. Electron Devices 2008, 55, 2718–2727. [Google Scholar] [CrossRef]

- Olivo, J.; Carrara, S.; Micheli, G.D. Energy Harvesting and Remote Powering for Implantable Biosensors. IEEE Sens. J. 2011, 11, 1573–1586. [Google Scholar] [CrossRef]

- Best Research-Cell Efficiencies, NREL. Available online: http://www.nrel.gov/ncpv/images/efficiency_chart.jpg (accessed on 2 July 2016).

- Pandey, A.; Tyagi, V.; Selvaraj, J.A.; Rahim, N.; Tyagi, S. Recent advances in solar photovoltaic systems for emerging trends and advanced applications. Renew. Sustain. Energy Rev. 2016, 53, 859–884. [Google Scholar] [CrossRef]

- Tibbits, T.N.D.; Beutel, P.; Grave, M.; Karcher, C.; Oliva, E.; Siefer, G.; Wekkeli, A.; Schachtner, M.; Dimroth, F.; Bett, A.W.; et al. New Efficiency Frontiers with Wafer-Bonded Multi-Junction Solar Cells. In Proceedings of the 29th European PV Solar Energy Conference and Exhibition, Amsterdam, The Netherlands, 22–26 September 2014.

- Wang, Z.L.; Wu, W. Nanotechnology-Enabled Energy Harvesting for Self-Powered Micro-/Nanosystems. Angew. Chem. Int. Ed. 2012, 51, 11700–11721. [Google Scholar] [CrossRef] [PubMed]

- Mishra, A.; Bäuerle, P. Small Molecule Organic Semiconductors on the Move: Promises for Future Solar Energy Technology. Angew. Chem. Int. Ed. 2012, 51, 2020–2067. [Google Scholar] [CrossRef] [PubMed]

- Li, G.; Zhu, R.; Yang, Y. Polymer solar cells. Nat. Photonics 2012, 6, 153–161. [Google Scholar] [CrossRef]

- Virtuani, A.; Lotter, E.; Powalla, M. Performance of Cu(In,Ga)Se2 solar cells under low irradiance. Thin Solid Films 2003, 431–432, 443–447. [Google Scholar] [CrossRef]

- Chen, G.; Ghaed, H.; Haque, R.; Wieckowski, M.; Kim, Y.; Kim, G.; Fick, D.; Kim, D.; Seok, M.; Wise, K.; et al. A cubic-millimeter energy-autonomous wireless intraocular pressure monitor. In Proceedings of the IEEE International Solid-State Circuits Conference, Francisco, CA, USA, 20–24 February 2011; pp. 310–312.

- Kim, D.; Chen, G.; Fojtik, M.; Seok, M.; Blaauw, D.; Sylvester, D. A 1.85fW/bit ultra low leakage 10T SRAM with speed compensation scheme. In Proceedings of the IEEE International Symposium of Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, 15–18 May 2011; pp. 69–72.

- Fan, F.R.; Tang, W.; Wang, Z.L. Flexible Nanogenerators for Energy Harvesting and Self-Powered Electronics. Adv. Mater. 2016, 28, 4283–4305. [Google Scholar] [CrossRef] [PubMed]

- Wang, Z.L.; Song, J. Piezoelectric Nanogenerators Based on Zinc Oxide Nanowire Arrays. Science 2006, 312, 242–246. [Google Scholar] [CrossRef] [PubMed]

- Zhu, G.; Zhou, Y.S.; Bai, P.; Meng, X.S.; Jing, Q.; Chen, J.; Wang, Z.L. A Shape-Adaptive Thin-Film-Based Approach for 50% High-Efficiency Energy Generation Through Micro-Grating Sliding Electrification. Adv. Mater. 2014, 26, 3788–3796. [Google Scholar] [CrossRef] [PubMed]

- Tang, W.; Jiang, T.; Fan, F.R.; Yu, A.F.; Zhang, C.; Cao, X.; Wang, Z.L. Liquid-Metal Electrode for High-Performance Triboelectric Nanogenerator at an Instantaneous Energy Conversion Efficiency of 70.6%. Adv. Funct. Mater. 2015, 25, 3718–3725. [Google Scholar] [CrossRef]

- Persano, L.; Dagdeviren, C.; Su, Y.; Zhang, Y.; Girardo, S.; Pisignano, D.; Huang, Y.; Rogers, J.A. High performance piezoelectric devices based on aligned arrays of nanofibers of poly(vinylidenefluoride-co-trifluoroethylene). Nat. Commun. 2013, 4, 1633. [Google Scholar] [CrossRef] [PubMed]

- Lee, M.; Chen, C.Y.; Wang, S.; Cha, S.N.; Park, Y.J.; Kim, J.M.; Chou, L.J.; Wang, Z.L. A Hybrid Piezoelectric Structure for Wearable Nanogenerators. Adv. Mater. 2012, 24, 1759–1764. [Google Scholar] [CrossRef] [PubMed]

- Chen, H.; Liu, M.; Jia, C.; Zhang, C.; Wang, Z. Low Power IC Design of the Wireless Monitoring System of the Orthopedic Implants. In Proceedings of the 29th Annual International Conference of the IEEE Engineering in Medicine and Biology Society, Milano, Italy, 25–29 August 2007; pp. 5766–5769.

- Arsalan, M.; Ouda, M.H.; Marnat, L.; Ahmad, T.J.; Shamim, A.; Salama, K.N. A 5.2 GHz, 0.5mWRF powered wireless sensor with dual on-chip antennas for implantable intraocular pressure monitoring. In Proceedings of the IEEE MTT-S International Microwave Symposium Digest (IMS), Seattle, WA, USA, 2–7 June 2013.

- Moradi, E.; Björninen, T.; Sydänheimo, L.; Ukkonen, L.; Rabaey, J.M. Analysis of wireless powering of mm-size neural recording tags in RFID-inspired wireless brain-machine interface systems. In Proceedings of the IEEE International Conference on RFID, Orlando, FL, USA, 30 April–2 May 2013; pp. 8–15.

- Ahn, D.; Ghovanloo, M. Optimal Design of Wireless Power Transmission Links for Millimeter-Sized Biomedical Implants. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 125–137. [Google Scholar] [CrossRef] [PubMed]

- Sauer, C.; Stanacevic, M.; Cauwenberghs, G.; Thakor, N. Power harvesting and telemetry in CMOS for implanted devices. In Proceedings of the IEEE International Workshop on Biomedical Circuits and Systems, Rotterdam, The Netherlands, 31 October–2 November 2004.

- Parramon, J.; Doguet, P.; Marin, D.; Verleyssen, M.; Munoz, R.; Leija, L.; Valderrama, E. ASIC-based batteryless implantable telemetry microsystem for recording purposes. In Proceedings of the 19th Annual International Conference of the IEEE Engineering in Medicine and Biology Society, Chicago, IL, USA, 30 October–2 November 1997; Volume 5, pp. 2225–2228.

- O’Driscoll, S.; Poon, A.S.Y.; Meng, T.H. A mm-sized implantable power receiver with adaptive link compensation. In Proceedings of the IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 294–295.

- Kim, A.; Ochoa, M.; Rahimi, R.; Ziaie, B. New and Emerging Energy Sources for Implantable Wireless Microdevices. IEEE Access 2015, 3, 89–98. [Google Scholar] [CrossRef]

- Tsai, J.Y.; Huang, K.H.; Wang, J.R.; Liu, S.I.; Li, P.C. Ultrasonic wireless power and data communication for neural stimulation. In Proceedings of the IEEE International Ultrasonics Symposium, Orlando, FL, USA, 18–21 October 2011; pp. 1052–1055.

- Song, S.H.; Kim, A.; Ziaie, B. Omnidirectional Ultrasonic Powering for Millimeter-Scale Implantable Devices. IEEE Trans. Biomed. Eng. 2015, 62, 2717–2723. [Google Scholar] [CrossRef] [PubMed]

- Christensen, D.B.; Roundy, S. Ultrasonically powered piezoelectric generators for bio-implantable sensors: Plate versus diaphragm. J. Intell. Mater. Syst. Struct. 2016, 27, 1092–1105. [Google Scholar] [CrossRef]

- Larson, P.J.; Towe, B.C. Miniature ultrasonically powered wireless nerve cuff stimulator. In Proceedings of the 5th International IEEE/EMBS Conference on Neural Engineering (NER), Cancun, Mexico, 27 April–1 May 2011; pp. 265–268.

- Maleki, T.; Cao, N.; Song, S.H.; Kao, C.; Ko, S.C.; Ziaie, B. An Ultrasonically Powered Implantable Micro-Oxygen Generator (IMOG). IEEE Trans. Biomed. Eng. 2011, 58, 3104–3111. [Google Scholar] [CrossRef] [PubMed]

- Charthad, J.; Weber, M.J.; Chang, T.C.; Arbabian, A. A mm-Sized Implantable Medical Device (IMD) With Ultrasonic Power Transfer and a Hybrid Bi-Directional Data Link. IEEE J. Solid-State Circuits 2015, 50, 1741–1753. [Google Scholar] [CrossRef]

- Jung, W.S.; Kang, M.G.; Moon, H.G.; Baek, S.H.; Yoon, S.J.; Wang, Z.L.; Kim, S.W.; Kang, C.Y. High Output Piezo/Triboelectric Hybrid Generator. Sci. Rep. 2015, 5. [Google Scholar] [CrossRef] [PubMed]

- Choi, D.; Lee, K.Y.; Jin, M.J.; Ihn, S.G.; Yun, S.; Bulliard, X.; Choi, W.; Lee, S.Y.; Kim, S.W.; Choi, J.Y.; et al. Control of naturally coupled piezoelectric and photovoltaic properties for multi-type energy scavengers. Energy Environ. Sci. 2011, 4, 4607–4613. [Google Scholar] [CrossRef]

- Yang, Y.; Zhang, H.; Zhu, G.; Lee, S.; Lin, Z.H.; Wang, Z.L. Flexible Hybrid Energy Cell for Simultaneously Harvesting Thermal, Mechanical, and Solar Energies. ACS Nano 2013, 7, 785–790. [Google Scholar] [CrossRef] [PubMed]

- Bandyopadhyay, S.; Chandrakasan, A.P. Platform Architecture for Solar, Thermal, and Vibration Energy Combining with MPPT and Single Inductor. IEEE J. Solid-State Circuits 2012, 47, 2199–2215. [Google Scholar] [CrossRef]

- Lu, C.; Raghunathan, V.; Roy, K. Efficient Design of Micro-Scale Energy Harvesting Systems. IEEE J. Emerg. Sel. Top. Circuits Syst. 2011, 1, 254–266. [Google Scholar] [CrossRef]

- Yi, J.; Ki, W.H.; Tsui, C.Y. Analysis and Design Strategy of UHF Micro-Power CMOS Rectifiers for Micro-Sensor and RFID Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 153–166. [Google Scholar] [CrossRef]

- Haddad, P.A.; Gosset, G.; Raskin, J.P.; Flandre, D. Automated Design of a 13.56 MHz 19 μW Passive Rectifier With 72% Efficiency Under 10 μA load. IEEE J. Solid-State Circuits 2016, 51, 1290–1301. [Google Scholar] [CrossRef]

- Lu, Y.; Ki, W.H. A 13.56 MHz CMOS Active Rectifier With Switched-Offset and Compensated Biasing for Biomedical Wireless Power Transfer Systems. IEEE Trans. Biomed. Circuits Syst. 2014, 8, 334–344. [Google Scholar]

- Huang, C.; Kawajiri, T.; Ishikuro, H. A Near-Optimum 13.56 MHz CMOS Active Rectifier With Circuit-Delay Real-Time Calibrations for High-Current Biomedical Implants. IEEE J. Solid-State Circuits 2016, 51, 1797–1809. [Google Scholar] [CrossRef]

- Steyaert, M.; van Roermund, A.; Baschirotto, A. Analog Circuit Design: Low Voltage Low Power; Short Range Wireless Front-Ends; Power Management and DC-DC; Springer: Dordrecht, The Netherlands, 2014. [Google Scholar]

- Lu, C.; Park, S.P.; Raghunathan, V.; Roy, K. Efficient power conversion for ultra low voltage micro scale energy transducers. In Proceedings of the Design, Automation Test in Europe Conference Exhibition (DATE), Dresden, Germany, 8–12 March 2010; pp. 1602–1607.

- Kim, J.; Mok, P.K.T.; Kim, C. A 0.15 V Input Energy Harvesting Charge Pump With Dynamic Body Biasing and Adaptive Dead-Time for Efficiency Improvement. IEEE J. Solid-State Circuits 2015, 50, 414–425. [Google Scholar] [CrossRef]

- Ki, W.H.; Lu, Y.; Su, F.; Tsui, C.Y. Design and analysis of on-chip charge pumps for micro-power energy harvesting applications. In Proceedings of the IEEE/IFIP 19th International Conference on VLSI and System-on-Chip, Hong Kong, China, 3–5 October 2011; pp. 374–379.

| (mV) | (μA/μm) | (pA/μm) | SS (mV/decade) | DIBL (mV/V) | |

|---|---|---|---|---|---|

| n-FinFET | 471.3 | 415.57 | 43.34 | 72.57 | 27.04 |

| p-FinFET | 460.6 | 458.83 | 43.91 | 71.00 | 18.74 |

| (mV) | (μA/μm) | (pA/μm) | SS (mV/decade) | DIBL (mV/V) | |

|---|---|---|---|---|---|

| NMOS | 411 | 354 | 1180 | 92.9 | 51.85 |

| PMOS | 390 | 122 | 163 | 89.9 | 57.23 |

| RSNM (mV) | WM (mV) | Access | Leakage | Write Time (ns) | Area (μm2) | |||||

|---|---|---|---|---|---|---|---|---|---|---|

| Time (μs) | Power (pW) | |||||||||

| 6T-SRAM | 32.21 | 31.49 | 107.9 | 24.7 | 1.36 | 0.92 | 1.82 | 1 | 19 | 0.07 |

| 8T-SRAM | 91.46 | 7.35 | 114.8 | 24 | 1.14 | 0.62 | 1.92 | 0.99 | 21 | 0.1108 |

| 9T-SRAM | 90.93 | 7.39 | 115.7 | 24.4 | 0.87 | 0.56 | 2 | 1.1 | 15 | 0.1274 |

| Parameter | 14 nm | 65 nm |

|---|---|---|

| DC Gain | 51.9 dB | 41.7 dB |

| Phase Margin | ||

| Unity gain bandwidth | 338 MHz | 125 MHz |

| Power Consumption | 180.93 μW | 416 μW |

| 200 fF | 200 fF | |

| 500 fF | 500 fF |

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lundager, K.; Zeinali, B.; Tohidi, M.; Madsen, J.K.; Moradi, F. Low Power Design for Future Wearable and Implantable Devices. J. Low Power Electron. Appl. 2016, 6, 20. https://0-doi-org.brum.beds.ac.uk/10.3390/jlpea6040020

Lundager K, Zeinali B, Tohidi M, Madsen JK, Moradi F. Low Power Design for Future Wearable and Implantable Devices. Journal of Low Power Electronics and Applications. 2016; 6(4):20. https://0-doi-org.brum.beds.ac.uk/10.3390/jlpea6040020

Chicago/Turabian StyleLundager, Katrine, Behzad Zeinali, Mohammad Tohidi, Jens K. Madsen, and Farshad Moradi. 2016. "Low Power Design for Future Wearable and Implantable Devices" Journal of Low Power Electronics and Applications 6, no. 4: 20. https://0-doi-org.brum.beds.ac.uk/10.3390/jlpea6040020