MDPI

Article

# A 0.18-ns Response Time Digital LDO Regulator with Adaptive PI Controller in 180-nm CMOS

Shengping Lv † D, Peiyuan Wan †, Hongda Zhang †, Jiarong Geng †, Jiabao Wen †, Yiming Yao † and Zhijie Chen \*,†

Faculty of Information Technology, College of Microelectronics, Beijing University of Technology, Beijing 100124, China; lspbjut@emails.bjut.edu.cn (S.L.); wanpy@bjut.edu.cn (P.W.); feall3@emails.bjut.edu.cn (H.Z.); fresh\_grapes@126.com (J.G.); wenjiabao0919@163.com (J.W.); yiming423@hotmail.com (Y.Y.)

- \* Correspondence: chenzj@bjut.edu.cn; Tel.: +86-(010)-6739-1269

- † These authors contributed equally to this work.

**Abstract:** Digital low drop-out regulator (D-LDO) with fast settling time and superior transient response is gaining increasing attention to make up for the deficiency of analog LDO. However, as the traditional digital LDOs regulate the output voltage code at a rate of 1 bit per clock cycle, the transient response speed is limited. In this paper, a multi-bit conversion technique is proposed to improve the transient response speed. The multi-bit conversion technique is achieved by an error detector with adaptive regulation of proportion and integration parameters in the digital controller before pass devices. Besides, a voltage sensor and a time-to-digital converter are employed to convert the output voltage to digital codes. Implemented in a 180-nm CMOS process, the proposed D-LDO features under 36/33 mV of undershoot/overshoot at  $V_{\rm OUT} = 0.95$  V as the load current steps up with 40 mA/1 ns on a 0.5 nF load capacitor. The simulated response time is 0.18-ns, the figure-of-merit of speed FOM1 is 0.65 ps and FOM2 achieves 0.068 pF.

Keywords: low drop-out regulator; adaptive control; fast response; embedded power management

Citation: Lv, S.; Wan, P.; Zhang, H.; Geng, J.; Wen, J.; Yao, Y.; Chen, Z. A 0.18-ns Response Time Digital LDO Regulator with Adaptive PI Controller in 180-nm CMOS. Electronics 2021, 10, 1668. https://dx.doi.org/10.3390/ electronics10141668

Academic Editor: Costas Psychalinos

Received: 24 May 2021 Accepted: 7 July 2021 Published: 13 July 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

## 1. Introduction

Digital low drop-out regulator (D-LDO), enjoying a wide range of applications in the Internet of Things (IoT) technology, has recently become one of the main topics of much research in the field of wireless communications. LDOs normally use power from the battery or the energy harvest. In such conditions, LDOs are desired to improve battery life and improve user experiences with immediate transition. In particular, the application of the IoT makes that the battery or the energy harvest provide supply voltage lower than ever. Hence, the stability is harder to control because the decrease of dynamic range and bandwidth of integrated circuits.

Conventional LDOs have been designed with analog circuits and employed an error amplifier and a driver amplifier to provide voltage regulation with negative feedback. They exhibit high efficiency, fast response time and high power supply rejection (PSR) [1–3]. However, it is difficult for analog LDOs to operating at low supply voltage, which has prompted the digital implementations of LDOs [4].

Comparing with analog LDOs, the digital low-dropout regulator (D-LDO) is more suitable for low-supply-voltage operation, and the input-voltage range of D-LDOs is unlimited without error amplifiers. In addition, D-LDO has better scalability and portability exploiting the benefit of digital-logic characteristics. Employing a large number of shift-register, conventional D-LDO has a slower transient response than the analog LDO [5]. Fast load regulation is important in digital circuits with rapidly changing supply current. In [6–8], D-LDOs with an improved triggered comparator have been proposed to improve the transient response, but the performances of the D-LDOs are limited by the analog-to-digital interface, i.e., the comparator. Ref. [9] has categorized all the existing LDO

designs by their control methods. Itpresents the hybrid LDO is a good low-voltage solution with fast transient response and also certain power supply rejection. In [10], D-LDO with transient enhanced PI controller which forms control deviation according to the given value and the actual output value achieves fast transient settling by adjusting the gain of PI controller, and the load current variation can be improved as well. D-LDO in [11] boosts loop-gain dynamically during load transients by a load transient detector without compromising the stability of the D-LDO at steady-state operation, but there may be a deviation in the regulation because of the analog-to-digital converter (ADC).

In this paper, a D-LDO with fast settling time and low undershoot/overshoot is proposed. To improve the load transient response, a time-to-digital converter (TDC) based converter and a PI controller are adopted to achieve a multi-bit regulation. By combining the benefits of both analog and digital control loops with PI controller can be a good low-voltage solution with fast response. The settling time is reduced by five times to 26 ns. In addition, an error detector is proposed to adjust the coefficient of the PI controller adaptively and reduce undershoot/overshoot voltage to 36/33 mV with 40 mA/ns.

The remainder of this paper is organized as follows: In Section 2, the architecture of the D-LDO is proposed. Section 3 presents the details of the circuit implementation of the proposed structure. The simulation results, discussions, and comparisons are illustrated in Section 4. Finally, the conclusion of this paper is given in Section 5.

#### 2. Architecture of the Proposed D-LDO

### 2.1. Topology

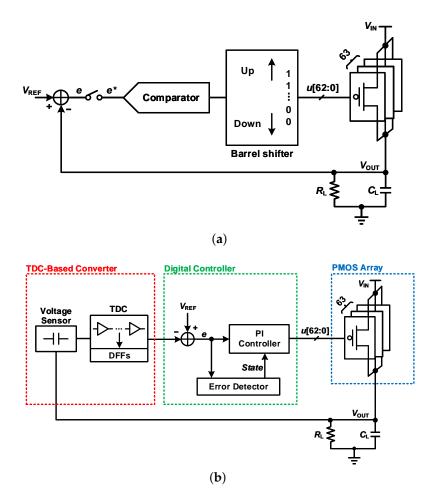

Figure 1 shows the circuit diagram for the baseline D-LDO and the proposed D-LDO. The baseline D-LDO employs a comparator and a barrel shifter, whose output code switches 1 bit in a clock cycle. In order to speed up the response, a TDC-Based Converter and an adaptive PI controller are used. The first component is the TDC-based Converter, which provides a digital code of the output voltage  $V_{\rm OUT}$ . In the TDC-based converter, a voltage sensor firstly converts the output voltage ( $V_{OUT}$ ) to a time signal by capturing the charging time of a capacitor. The TDC includes the buffers and D-Flip-Flops, converting the time signal to a 63-bit width thermometer code furtherly. Then, the second component is the Digital Controller which consists of a subtractor, an error detector and a PI controller. The subtractor in the digital controller outputs the error between the thermometer code  $V_{\rm OUT}$ and the reference voltage  $V_{REF}$ . The error is transmitted to the PI controller and the error detector. Together with a State code calculated by the error detector, the PI controller determined the number of turned-on transistors in the following PMOS array which contains 63 identical PMOS devices controlled by the digital code supplied currents. The proportion and integral coefficients of the PI controller are selected adaptively according to fuzzy rules based on the error and the integral of the error. In this way, the PI controller produces 63-bit width thermometer codes to control the gate of the power transistors in the PMOS array, so that the right amount of current is supplied to the load. The major building blocks of the proposed architecture above will be illustrated in Section 3.

Figure 1. The circuit architecture of (a) the baseline D-LDO and (b) the proposed D-LDO.

#### 2.2. Transfer Function of the Control Loop

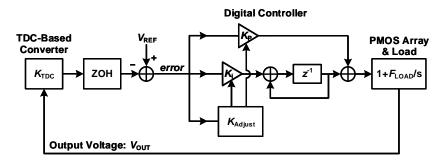

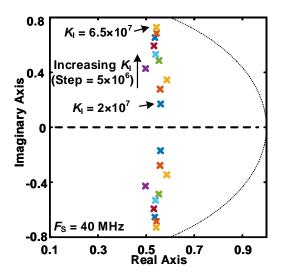

Figure 2 shows the hybrid model for the proposed D-LDO. The relationship between input and output of the TDC-based converter is modeled as a gain  $K_{\rm TDC}$  and a zero order holder (ZOH) as interface between continue signal and discrete signal. The z-domain transfer function of the digital controller is derived by taking the traditional z-transfer of the PI controller and is given as

$$G_{PI}(z) = (K_p + K_{Adjust}) + (K_i + K_{Adjust}) \frac{z^{-1}}{1 - z^{-1}}$$

(1)

where  $K_{\text{Adjust}}$  is the adaptive coefficient. The output stage and load can be approximated as an RC circuit, and the *z*-domain model of load and PMOS array is

$$G_{LP}(z) = \frac{F_{LOAD}z}{z - e^{-F_{LOAD}/F_S}}$$

(2)

where  $F_{\text{LOAD}} = 1/(2\pi \cdot R_{\text{LOAD}} \cdot C_{\text{LOAD}})$ ,  $F_{\text{S}}$  is sampling frequency. The  $K_{\text{P}}$  and  $K_{\text{i}}$  with  $K_{\text{Adjust}}$  can be represented as  $K_{\text{P}}'$  and  $K_{\text{i}}'$ .  $V_{\text{REF}}$  is considered as AC ground so the closed-loop transfer function of the D-LDO in z-domain is derived as

$$G(z) = \frac{\left[K_{p}'z - \left(K_{p}' - K_{i}'\right)\right]\left[(1 + F_{LOAD})z - 1\right]}{\left[1 + K_{TDC}K_{p}'(1 + F_{LOAD})\right]z^{2} - \left[2 + K_{TDC}K_{p}' + K_{TDC}\left(K_{p}' - K_{i}'\right)(1 + F_{LOAD})\right]z - \left(K_{p}' - K_{i}'\right)K_{TDC} + 1}$$

(3)

Electronics **2021**, 10, 1668 4 of 12

Consider that  $K_p$  and  $K_i$  are adjusted with *error*, the stability of the proposed D-LDO is changed in each period. If there is a large *error*, the stability is traded off to obtain a faster transient response. In contrast,  $K'_p$  and  $K'_i$  are changed to achieve a more stable regulation when the *error* is small.

Figure 2. The system hybrid model for the proposed D-LDO.

Figure 3 shows the poles of the proposed system under variable integration gain. As illustrated in Figure 3, a higher integration gain of the PI controller leads loss of stability. According to the traditional PI theory, large  $K_p$  leads to quick adjustment and large  $K_i$  leads to high accuracy. In adaptive process, a large  $K_p'$  is selected when *error* in wide region to approach  $V_{\text{REF}}$  quickly. In addition, if *error* in narrow region, a large  $K_i'$  is chosen for eliminating errors.

**Figure 3.** The pole plot of the proposed system under variable integration gain (x shown in Figure 3).

## 3. Circuit Implementation

### 3.1. Time-to-Digital Based Converter

The transformation of the  $V_{\text{OUT}}$  from analog to digital is based on a voltage sensor and a TDC.

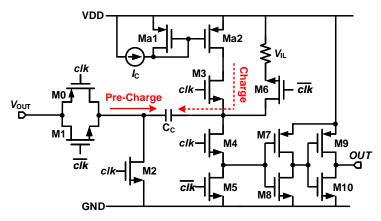

Figure 4 shows the schematics of the voltage sensor which converts the analog signals to time signals. The operation process of voltage sensor consists of two parts. Firstly, when clk is low level, the switches M0, M1, M5, and M6 are turned on. The capacitor  $C_{\rm C}$  is pre-charged with  $V_{\rm OUT}$  and  $V_{\rm IL}$  which is the trigger voltage of the DFFs which is an information storage device with memory function and two stable states behind. During the charge stage, the quantity of electric charge in  $C_{\rm C}$  can be expressed as  $Q_{\rm pre} = C_{\rm C} \cdot (V_{\rm OUT} - V_{\rm IL})$ . Secondly when clk is high level, M3, M4, and M6 are turned on, the two

Electronics **2021**, 10, 1668 5 of 12

plates of  $C_C$  are connected with GND and current source  $I_C$ . Because the current loss of  $C_C$  does not occur suddenly, the charge variation in  $C_C$  is given as follow

$$\Delta Q = C_{\rm C} \cdot [V_{\rm IL} - (V_{\rm IL} - V_{\rm OUT})] = I_{\rm C} \cdot \Delta t \tag{4}$$

where  $\Delta t$  is the time from the beginning of charging to the DFFs are triggered. Hence, the voltage sensor converts  $V_{\text{OUT}}$  to a time signal  $\Delta t$ .

Figure 4. Schematics of the Voltage Sensor.

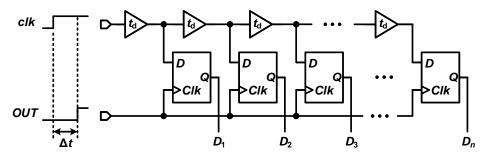

Figure 5 shows the schematics of the TDC. During the time of  $\Delta t$ , the input signal "1" is transmitted in the delay line. When the pin OUT generates a positive edge, in other words, the time  $\Delta t$  is consumed, the DFFs are triggered. The number of DFFs output signal "1" is expressed as  $N = [\Delta t/t_{\rm d}]$ , where  $t_{\rm d}$  is the delay time of a buffer. The buffers and DFFs showed in Figure 5 are suitable for standard cell-based logic synthesis.

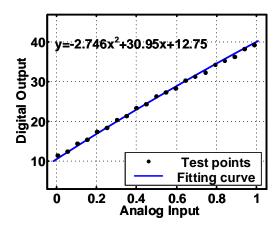

From the discuss above, an analog signal of  $V_{\rm OUT}$  is converted to a signal about time through the operation of voltage sensor when clk in low level. After clk is switched to high level, the time signal is transmitted to the TDC for generating digital codes. At the end of a cycle, 63-bit digital thermometer code is obtained. Figure 6 shows the linearity of the proposed TDC-based converter. The test points are fitted into a quadratic function. The different value of  $V_{OUT}$  is converted to digital code and the a quantization interval of the TDC-based converter is about 25 mV.

Figure 5. Schematics of the Time-to-Digital Converter.

Electronics **2021**, 10, 1668 6 of 12

Figure 6. The linearity of proposed TDC-Based converter.

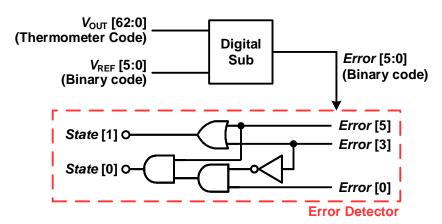

#### 3.2. Error Detector

The adaptive operation in the proposed D-LDO adjusts the coefficients of P and I which is ducted by the error detector as shown in Figure 7. In this mode, the *error* between  $V_{\rm OUT}$  and  $V_{\rm REF}$  is divided into four ranges. The four ranges correspond to four groups of coefficients for the PI controller. Therefore, using the PI digital controller with an error detector, the proposed D-LDO achieves a faster response time and lower overshoot/undershoot voltage.

Figure 7. Schematics of the Error Detector

A digital sub is introduced to generate the error between the  $V_{\rm OUT}$  and  $V_{\rm REF}$ . Because the output of the TDC-based converter is thermometer code and the reference voltage is binary, the digital sub contains a encoder to convert the output of the TDC-based converter to binary codes. The entire digital sub is implemented by Verilog and logical synthesis.

Four levels for error are shown in Table 1:  $Error \ge 32$ ,  $Error \ge 8$ ,  $Error \ge 1$ , Error = 0, where the digital code is equivalent to the thermometer code from the TDC-based converter output N. And  $\Delta N = 1$  is equivalent to the 25 mV of voltage values. Therefore, the State[1:0] becomes "11" when  $Error \ge 0.9$  V, and becomes "10" when  $Error \ge 0.4$  V, and becomes "01" when Error < 0.4 V and becomes "00" when achieve stabilizedt. Depending on Error[5], Error[3], Error[0], the PI controller operates in three groups of coefficient as shown in Table 2.

| Error Levels    | Input    |          |          | Output   |          |

|-----------------|----------|----------|----------|----------|----------|

|                 | Error[5] | Error[3] | Error[0] | State[1] | State[0] |

| Error $\geq$ 32 | 1        | Χ        | X        | 1        | 1        |

| Error $\geq 8$  | 0        | 1        | X        | 1        | 0        |

| Error > 1       | 0        | 0        | 1        | 0        | 1        |

0

0

0

**Table 1.** State table. 1 means high voltage, 0 means low voltage, X means any voltage.

Table 2. Cofficient.

Error = 0

| Inj      | put      | Out     | tput    |

|----------|----------|---------|---------|

| State[1] | State[0] | P       | I       |

| 0        | 0        | Hold on | Hold on |

| 0        | 1        | 0.8     | 4       |

| 1        | 0        | 1       | 0.7     |

| 1        | 1        | 1.2     | 0.1     |

The determination of coefficients is based on the fuzzy algorithm [12,13]. For example, if the *error* is "large" then  $K_P = a_1x + b_1$ , here the  $a_1$  and  $b_1$  are the premise parameter in membership functions of the fuzzy sets "large" in the premises. Therefore, we define the relative range of error as [-3, -2, -1, 0, 1, 2, 3] corresponding to [Negative large, Negative mid, Negative small, Zero, Positive small, Positive mid, Positive large]. To confirm the parameter, we divide the spaces into some fuzzy subspaces where the performance index is minimized.

As mentioned in Section 2, the large  $K_i$  leads instability. In order to speed up the rate of regulation, a large  $K_p$  is chosen. Hence, we expect  $K_i$  will not generate overshoot when the system is regulated quickly. Hence, we select the value of  $K_i$  is less than 1 when the error is large. On the contrary, when the  $V_{\text{OUT}}$  close to reference, a large  $K_i$  and a small  $K_p$  are needed to eliminate the error and avoid the underdamping. That's the fuzzy principle to design the value of  $K_p$  and  $K_i$ . Through the simulation and the experience of the control system, the final parameters are obtained to calculate the coefficients in Table 2.

## 4. Simulation Results and Discussion

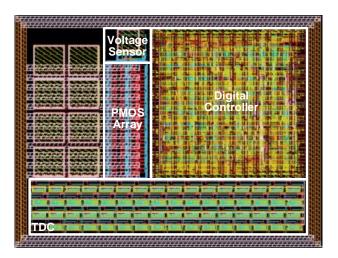

The proposed adaptive D-LDO is realized in 180-nm SMIC technology as shown in Figure 8 and the area is 235  $\mu m \times 312~\mu m$ . In the circuit, the charing capacitor  $C_C$  is 450 fF and the charging current  $I_C$  is 100  $\mu A$ . The delay of each buffers  $t_d$  is 0.145 ns. The D-LDO operates within an input voltage range of 1–1.2 V and an output voltage of 0.95 V. The D-LDO supplies a maximum current of 100 mA with a load capacitance of 500 pF, while operating at a 40 MHz clock rate with a quiescent current of 34.68  $\mu A$ . Simulated current efficiency is 99.64% at 10  $\Omega$  load resistor.

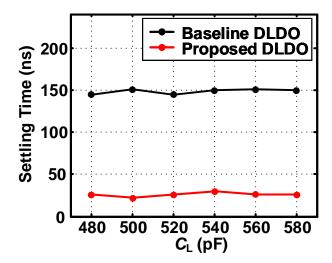

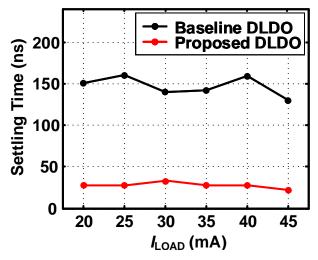

In order to describe the transient response speed of the proposed circuit, the settling time  $T_S$  with variable load was simulated. The settling time is defined as the time that the output voltage recovers to 90% of the droop voltage. As shown in Figures 9 and 10, the proposed D-LDO reduces the settling time under each condition. The settling time is decreased to only 17.6% of the baseline design of D-LDO (from 147.8 ns to 26.1 ns) on average in corner tt which means typical corner . In other words, the proposed circuit improves the response speed by about 5 times.

Figure 8. The layout of the proposed D-LDO.

Figure 9. The settling time with load capacitance change.

**Figure 10.** The settling time with  $I_{\rm LOAD}$  change.

Electronics **2021**, 10, 1668 9 of 12

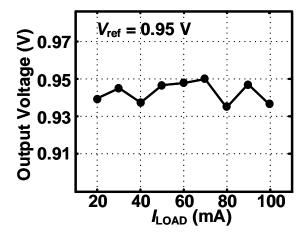

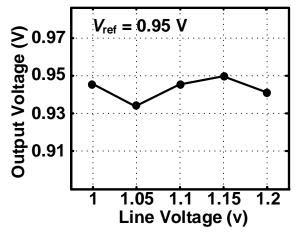

As shown in Figures 11 and 12, the output voltage with a load current range from 20 to 100 mA and a line voltage range from 1 to 1.2 V are simulated. The effect of the load current and the line voltage on the output voltage is not slight, a load regulation of 0.3 mV/mA and a line regulation of 0.1 mV/mV are achieved. Due to the quantization interval of the TDC-based converter is about 25 mV, the output voltage error in variations of simulation environment is acceptable.

**Figure 11.** The output voltage under the variations of load current.

Figure 12. The output voltage under the variations of line voltage.

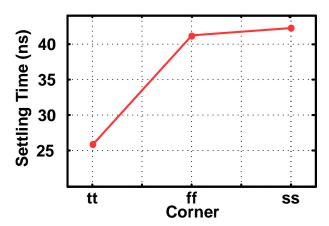

Figure 13 shows the simulated settling time in various corners. With  $V_{\rm IN}$  = 1 V and  $V_{\rm OUT}$  = 0.95 V, corner tt achieves 26.1 ns, corner ff and ss which means fast or slow corner achieve 42 ns and 44 ns, respectively. It shows the proposed D-LDO has consistency in different conditions.

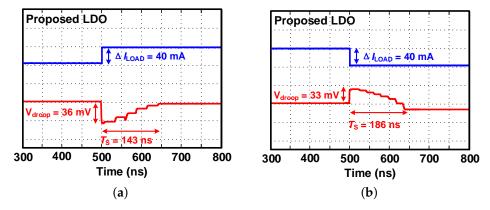

The simulated output transient response for the load current change with 40 mA in 1 ns in Figure 14. With  $V_{\rm in}$  = 1 V,  $V_{\rm OUT}$  = 0.95 V (both step up and down),  $f_{\rm S}$ = 40 MHz,  $C_{\rm L}$  = 0.5 nF,  $R_{\rm L}$  = 10  $\Omega$ , the simulated output undershoot is 36 mV and the overshoot is 33 mV. Recovery time achieves 143/186 ns within undershoot/overshoot. Compared with the published LDO designs with PI controller, the proposed D-LDO exhibits a significantly faster settling time.

Electronics 2021, 10, 1668 10 of 12

Figure 13. The settling time with corner change.

**Figure 14.** The transient responses of  $V_{\text{OUT}}$  when  $I_{\text{LOAD}}$  change of (a) step up and (b) step down.

The response time  $T_R$  of the D-LDO is proposed in [14] is given as

$$T_{\rm R} = \frac{C_{\rm L} \Delta V_{\rm OUT}}{I_{\rm MAX}} \tag{5}$$

where  $C_L$  is the load capacitance,  $\Delta V_{OUT}$  is the undershoot/overshoot voltage,  $I_{MAX}$  is the maximum load current. Commonly used figure-of-merits FOM1 and FOM2 [14] for LDO performance is

$$FOM1 = \frac{C_L \Delta V_{OUT}}{I_{MAX}} \cdot \frac{I_Q}{I_{MAX}}$$

(6)

$$FOM1 = \frac{C_{L}\Delta V_{OUT}}{I_{MAX}} \cdot \frac{I_{Q}}{I_{MAX}}$$

$$FOM2 = \frac{\Delta V_{OUT}}{V_{OUT}} \cdot \frac{I_{Q}}{I_{MAX}} \cdot C_{L}$$

(6)

where  $I_{O}$  is the quiescent current. The smaller FOM indicates the better LDO performance. The comparison with published D-LDOs are listed in Table 3. In comparison to those prior designs, the proposed D-LDO achieves FOM1 of 0.65 ps, FOM2 of 0.068 pF, and  $T_R$ of 0.18-ns. In contrast to these prior D-LDOs, this paper achieves faster response time, lower undershoot/overshoot voltage, and more outstanding performance on the figureof-merit FOM1 and FOM2. Meanwhile, the proposed D-LDO exhibits decent competitive current efficiency.

Electronics 2021, 10, 1668 11 of 12

| Design                                   | Yuan [15],<br>EDSSC'19 | Yuan [16],<br>TCSII'20 | Chen [17],<br>TPEL'21 | This Work       |

|------------------------------------------|------------------------|------------------------|-----------------------|-----------------|

| Process                                  | 180- nm                | 180-nm                 | 110-nm                | 180-nm          |

| $V_{\mathrm{IN}}\left(\mathrm{V}\right)$ | 1                      | 0.8 - 1.1              | 0.8 - 1.2             | 1–1.2           |

| $V_{\rm OUT}$ (V)                        | 0.9                    | 0.7 - 1.0              | 0.7 - 1.1             | 0.95            |

| Load Regulation (mV/mA)                  | 0.053                  | 0.11                   | 0.422                 | 0.3             |

| Current Consumption (μA)                 | 500                    | 500                    | 188.8-197.9           | 34.68           |

| Total $C_L$                              | Not available          | 390 pF                 | 40 pF                 | 0.5 nF          |

| $\Delta V_{ m OUT} @ \Delta I_{ m LOAD}$ | 420 mV<br>@216 mA      | 267 mV<br>@160 mA      | 360 mV<br>@47.5 mA    | 36 mV<br>@40 mA |

| Load Transient Edge Time (ns)            | NA                     | 65                     | <1                    | 1               |

| Recovery Under/Over-shoot Time (ns)      | 80/80                  | 80/80                  | 67/250                | 143/186         |

| Peak Current Efficiency (%)              | 99.78                  | 99.71                  | 92.98-99.61           | 99.64           |

0.95

2.1

Not available

0.52

2.03

0.362

0.2

1.26

0.0706

0.18

0.65

0.068

Table 3. Comparison with published D-LDO designs.

#### 5. Conclusions

FOM1 (ps)

FOM2 (pF)

Response Time  $T_R$  (ns)

A fully integrated D-LDO with fast transient response is proposed. The D-LDO is designed and simulated in 180-nm technology. With an error detector, the proposed D-LDO achieves an undershoot of 36 mV, overshoot of 33 mV, and transient response time of 143/186 ns for a load change with a 40 mA/ns slew rate. The multi-bit conversion technique decreases the settling time in corner tt, ff, ss to 17.6%, 27.3%, and 28.6% of the baseline D-LDO respectively. The current consumption is 34.68 μA and the peak current efficiency is 99.64%. The proposed D-LDO achieves FOM1 of 0.65 ps and FOM2 of 0.068 pF, which are comparable with the state-of-the-art designs.

Author Contributions: Conceptualization, S.L., H.Z. and Z.C.; Data curation, S.L., H.Z. and J.G.; Investigation, P.W., J.W. and Y.Y.; Methodology, S.L., H.Z. and Z.C.; Resources, P.W. and Z.C.; Writing—original draft, S.L., H.Z. and Z.C.; and Writing—review and editing, S.L., H.Z., P.W. and Z.C; All authors have read and agreed to the published version of the manuscript.

Funding: This work was supported by Beijing Natural Science Foundation Project No. 4202010, and National Natural Science Foundation of China, Key Project No. 61731019.

Data Availability Statement: The data presented in this study are available on request from the corresponding author.

Conflicts of Interest: The authors declare no conflict of interest.

## References

- Lam, Y.H.; Ki, W.H. A 0.9 V 0.35 µm Adaptively Biased CMOS LDO Regulator with Fast Transient Response. In Proceedings of the 2008 IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008; pp. 442-626.

- Milliken, R.J.; Silva-Martinez, J.; Sanchez-Sinencio, E. Full On-Chip CMOS Low-Dropout Voltage Regulator. IEEE Trans. Circuits 2. Syst. I Regular Pap. 2007, 54, 1879-1890.

- Nasir, S.B.; Gangopadhyay, S.; Raychowdhury, A. All-Digital Low-Dropout Regulator With Adaptive Control and Reduced 3. Dynamic Stability for Digital Load Circuits. IEEE Trans. Power Electron. 2016, 31, 8293–8302.

- Ojima, N.; Nakura, T.; Iizuka, T.; Asada, K. A Synthesizable Digital Low-Dropout Regulator Based on Voltage-to-Time Conversion. In Proceedings of the 2018 IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), Verona, Italy, 8–10 October 2018; pp. 55–58.

- Woo, K.; Kim, T.; Hwang, S.; Kim, M.; Yang, B. A fast-transient digital LDO using a double edge-triggered comparator with a 5. completion signal. In Proceedings of the 2018 International Conference on Electronics, Information, and Communication (ICEIC), Honolulu, HI, USA, 24-27 January 2018; pp. 1-4

- Salem, L.G.; Warchall, J.; Mercier, P.P. A 100 nA-to-2 mA successive-approximation digital LDO with PD compensation and sub-LSB duty control achieving a 15.1 ns response time at 0.5 V. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 340–341.

7. Amayreh, M.; Leicht, J.; Manoli, Y. A 200ns settling time fully integrated low power LDO regulator with comparators as transient enhancement. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, USA, 22–25 May 2016; pp. 494–497.

- Ding, Z.; Rhee, W.; Wang, Z. A VCO-dedicated digital LDO with multi-comparator coarse loop and 1-bit Δ∑ fine loop for robust frequency generation. In Proceedings of the 2018 IEEE MTT-S International Wireless Symposium (IWS), Chengdu, China, 6–10 May 2018; pp. 1–4.

- 9. Lu, Y; Huang, M.; Martins, R.P. PID Control Considerations for Analog-Digital Hybrid Low-Dropout Regulators (Invited Paper). In Proceedings of the 2019 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Xi'an, China, 12–14 June 2019; pp. 1–3.

- 10. Kim, D.; Seok, M. A fully integrated digital low-dropout regulator based on event-driven explicit time-coding architecture. *IEEE J. Solid State Circuits* **2017**, *52*, 3071–3080.

- Lim, C.; Mandal, D.; Bakkaloglu, B.; Kiaei, S. A 50-mA 99.2% Peak Current Efficiency, 250-ns Settling Time Digital Low-Dropout Regulator With Transient Enhanced PI Controller. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2017, 25, 2360-2370.

- 12. Santos, M.; Dormido, S.; de la Cruz, J.M. Fuzzy-PID controllers vs. fuzzy-PI controllers. In Proceedings of the IEEE 5th International Fuzzy Systems, New Orleans, LA, USA, 11 September 1996; Volume 3, pp. 1598–1604.

- 13. Takagi, T.; Sugeno, M. Fuzzy identification of systems and its applications to modeling and control. *IEEE Trans. Syst. Man Cybern.* **1985**, 116–132, doi:10.1109/TSMC.1985.6313399.

- 14. Hazucha, P.; Karnik, T.; Bloechel, B.A.; Parsons, C.; Finan, D.; Borkar, S. Area-efficient linear regulator withultra-fast load regulation. *IEEE J. Solid State Circuits* **2005**, *40*, 933–940.

- 15. Yuan, Z.; Fan, S.; Geng, L. A 225-mA Binary Searching Digital LDO with Transient Enhancement. In Proceedings of the 2019 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Xi'an, China, 12–14 June 2019; pp. 1–2.

- 16. Yuan, Z.; Fan, S.; Yuan, C.; Geng, L. A 100 MHz, 0.8-to-1.1 V, 170 mA Digital LDO With 8-Cycles Mean Settling Time and 9-Bit Regulating Resolution in 180-nm CMOS. *IEEE Trans. Circuits Syst. II Express Briefs* **2020**, *67*, 1664–1668.

- 17. Chen, W.-J.; Huang, C.-H. Fast-Turnaround Design and Modeling Techniques for a Fast-Transient Digital Low-Dropout Regulator With 3 mV Ripples. *IEEE Trans. Power Electron.* **2021**, *36*, 6824–6837.