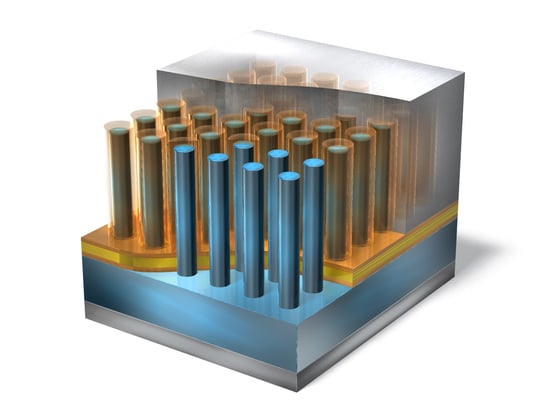

Fabrication of Silicon Nanowire Metal-Oxide-Semiconductor Capacitors with Al2O3/TiO2/Al2O3 Stacked Dielectric Films for the Application to Energy Storage Devices

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Zhang, L.; Liu, M.; Ren, W.; Zhou, Z.; Dong, G.; Zhang, Y.; Peng, B.; Hao, X.; Wang, C.; Jiang, Z.-D.; et al. ALD preparation of high-k HfO2 thin films with enhanced energy density and efficient electrostatic energy storage. RSC Adv. 2017, 7, 8388–8393. [Google Scholar] [CrossRef] [Green Version]

- Chen, C.; Duan, S.; Cai, T.; Liu, B.; Hu, G. Smart energy management system for optimal microgrid economic operation. In IET Renewable Power Generation; Institution of Engineering and Technology: Stevenage, UK, 2011; Volume 5, pp. 258–267. [Google Scholar]

- Lam, L.T.; Louey, R. Development of ultra-battery for hybrid-electric vehicle applications. J. Power Sources 2006, 158, 1140–1148. [Google Scholar] [CrossRef]

- Wagner, F.T.; Lakshmanan, B.; Mathias, M.F. Electrochemistry and the Future of the Automobile. J. Phys. Chem. Lett. 2010, 1, 2204–2219. [Google Scholar] [CrossRef]

- Leontis, I.; Botzakaki, M.A.; Georga, S.N.; Nassiopoulou, A.G. High capacitance density MIS capacitor using Si nanowires by MACE and ALD alumina dielectric. J. Appl. Phys. 2016, 119, 244508. [Google Scholar] [CrossRef]

- Banerjee, P.; Perez, I.; Henn-Lecordier, L.; Lee, S.B.; Rubloff, G.W. Nanotubular metal–insulator–metal capacitor arrays for energy storage. Nat. Nanotechnol. 2009, 4, 292–296. [Google Scholar] [CrossRef] [PubMed]

- Morel, P.H.; Haberfehlner, G.; Lafond, D.; Audoit, G.; Jousseaume, V.; Leroux, C.; Fayolle-Lecocq, M.; Baron, T.; Ernst, T. Ultra high density three dimensional capacitors based on Si nanowires array grown on a metal layer. Appl. Phys. Lett. 2012, 101, 083110. [Google Scholar] [CrossRef]

- Zhang, M.L.; Peng, K.Q.; Fan, X.; Jie, J.S.; Zhang, R.Q.; Lee, S.T.; Wong, N.B. Preparation of large-area uniform silicon nanowires arrays through metal-assisted chemical etching. J. Phys. Chem. C 2008, 112, 4444–4450. [Google Scholar] [CrossRef]

- Chartier, C.; Bastide, S.; Lévy-Clément, C. Metal-assisted chemical etching of silicon in HF–H2O2. Electrochim. Acta 2008, 53, 5509–5516. [Google Scholar] [CrossRef]

- Nassiopoulou, A.G.; Gianneta, V.; Katsogridakis, C. Si nanowires by a single-step metal-assisted chemical etching process on lithographically defined areas: Formation kinetics. Nanoscale Res. Lett. 2011, 6, 597. [Google Scholar] [CrossRef] [Green Version]

- Kato, S.; Watanabe, Y.; Kurokawa, Y.; Yamada, A.; Ohta, Y.; Niwa, Y.; Hirota, M. Metal-Assisted Chemical Etching Using Silica Nanoparticle for the Fabrication of a Silicon Nanowire Array. Jpn. J. Appl. Phys. 2012, 51, 02BP09. [Google Scholar] [CrossRef]

- Xie, Q.; Jiang, Y.-L.; Detavernier, C.; Deduytsche, D.; Meirhaeghe, R.L.V.; Ru, G.-P.; Li, B.-Z.; Qu, X.-P. Atomic layer deposition of TiO2 from tetrakis-dimethyl-amido titanium or Ti isopropoxide precursors and H2O. J. Appl. Phys. 2007, 102, 083521. [Google Scholar] [CrossRef]

- Dang, V.-S.; Parala, H.; Kim, J.H.; Xu, K.; Srinivasan, N.B.; Edengeiser, E.; Havenith, M.; Wieck, A.D.; de los Arcos, T.; Fischer, R.A.; et al. Electrical and optical properties of TiO2 thin films prepared by plasma-enhanced atomic layer deposition. Phys. Status Solidi (a) 2014, 211, 416–424. [Google Scholar] [CrossRef]

- Dueñas, S.; Castán, H.; García, H.; Andrés, E.S.; Toledano-Luque, M.; Mártil, I.; González-Díaz, G.; Kukli, K.; Uustare, T.; Aarik, J. A comparative study of the electrical properties of TiO2films grown by high-pressure reactive sputtering and atomic layer deposition. Semicond. Sci. Technol. 2005, 20, 1044–1051. [Google Scholar] [CrossRef]

- Alexandrov, P.; Koprinarova, J.; Todorov, D. Dielectric properties of TiO2-films reactively sputtered from Ti in an RF magnetron. Vacuum 1996, 47, 1333–1336. [Google Scholar] [CrossRef]

- Aarik, J.; Aidla, A.; Kiisler, A.-A.; Uustare, T.; Sammelselg, V. Effect of crystal structure on optical properties of TiO2 films grown by atomic layer deposition. Thin Solid Films 1997, 305, 270–273. [Google Scholar] [CrossRef]

- Avasthi, S.; McClain, W.E.; Man, G.; Kahn, A.; Schwartz, J.; Sturm, J.C. Hole-blocking titanium-oxide/silicon heterojunction and its application to photovoltaics. Appl. Phys. Lett. 2013, 102, 203901. [Google Scholar] [CrossRef] [Green Version]

- Mochizuki, T.; Gotoh, K.; Ohta, A.; Ogura, S.; Kurokawa, Y.; Miyazaki, S.; Fukutani, K.; Usami, N. Activation mechanism of TiOx passivating layer on crystalline Si. Appl. Phys. Express 2018, 11, 102301. [Google Scholar] [CrossRef]

- Woo, J.-C.; Chun, Y.-S.; Joo, Y.-H.; Kim, C.-I. Low leakage current in metal-insulator-metal capacitors of structural Al2O3/TiO2/Al2O3 dielectrics. Appl. Phys. Lett. 2012, 100, 081101. [Google Scholar] [CrossRef]

- Lehnert, W.; Ruhl, G.; Gschwandtner, A. Plasma enhanced atomic layer batch processing of aluminum doped titanium dioxide. J. Vac. Sci. Technol. A 2012, 30, 01A152. [Google Scholar] [CrossRef]

- Padhi, P.S.; Ajimsha, R.S.; Chetia, S.K.; Das, A.K.; Sahu, V.K.; Misra, P. Reduced leakage current in Al2O3/TiO2/Al2O3 dielectric stacks grown by pulsed laser deposition. AIP Conf. Proc. 2020, 2265, 030190. [Google Scholar]

- Kim, S.K.; Choi, G.-J.; Lee, S.Y.; Seo, M.; Lee, S.W.; Han, J.H.; Ahn, H.-S.; Han, S.; Hwang, C.S. Al-Doped TiO2 Films with Ultralow Leakage Currents for Next Generation DRAM Capacitors. Adv. Mater. 2008, 20, 1429–1435. [Google Scholar] [CrossRef]

- Shi, L.; Yin, J.; Yin, K.; Gao, F.; Xia, Y.; Liu, Z. An investigation into ultra-thin pseudobinary oxide (TiO2)x(Al2O3)1-x films as high-k gate dielectrics. Appl. Phys. A 2008, 90, 379–384. [Google Scholar] [CrossRef]

- Kim, Y.S.; Yun, S.J. Nanolaminated Al2O3–TiO2 thin films grown by atomic layer deposition. J. Cryst. Growth 2005, 274, 585–593. [Google Scholar] [CrossRef]

- Jeon, W.; Chung, H.-S.; Joo, D.; Kang, S.-W. TiO2/Al2O3/TiO2 Nanolaminated Thin Films for DRAM Capacitor Deposited by Plasma-Enhanced Atomic Layer Deposition. Electrochem. Solid-State Lett. 2008, 11, H19. [Google Scholar] [CrossRef]

- Lei, J.; Fang, C.; Liu, C.; Wu, D.; Li, A.-D. Flexible Al-Ti-Zn-O MIM capacitors fabricated by room temperature atomic layer deposition and their electrical performances. J. Alloys Compd. 2021, 870, 159391. [Google Scholar] [CrossRef]

- Lin, B.-C.; Ku, C.-S.; Lee, H.-Y.; Chakroborty, S.; Wu, A.T. Analysis of arrayed nanocapacitor formed on nanorods by flow-rate interruption atomic layer deposition. Appl. Surf. Sci. 2017, 426, 224–228. [Google Scholar] [CrossRef]

- Kemell, M.; Ritala, M.; Leskelä, M.; Ossei-Wusu, E.; Carstensen, J.; Föll, H. Si/Al2O3/ZnO:Al capacitor arrays formed in electrochemically etched porous Si by atomic layer deposition. Microelectron. Eng. 2007, 84, 313–318. [Google Scholar] [CrossRef]

- Burke, M.; Blake, A.; Djara, V.; O’Connell, D.; Povey, I.M.; Cherkaoui, K.; Monaghan, S.; Scully, J.; Murphy, R.; Hurley, P.K.; et al. High aspect ratio iridescent three-dimensional metal–insulator–metal capacitors using atomic layer deposition. J. Vac. Sci. Technol. A 2015, 33, 01A103. [Google Scholar] [CrossRef]

- Zhang, G.; Wu, H.; Chen, C.; Wang, T.; Wu, W.; Yue, J.; Liu, C. Transparent Nanotubular Capacitors Based On Transplanted Anodic Aluminum Oxide Templates. ACS Appl. Mater. Interfaces 2015, 7, 5522–5527. [Google Scholar] [CrossRef]

- Haspert, L.C.; Lee, S.B.; Rubloff, G.W. Nanoengineering Strategies for Metal–Insulator–Metal Electrostatic Nanocapacitors. ACS Nano 2012, 6, 3528–3536. [Google Scholar] [CrossRef]

- Ferguson, J.D.; Weimer, A.W.; George, S.M. Atomic Layer Deposition of Al2O3 Films on Polyethylene Particles. Chem. Mater. 2004, 16, 5602–5609. [Google Scholar] [CrossRef]

- Trasferetti, B.C.; Davanzo, C.U.; Zoppi, R.A.; da Cruz, N.C.; de Moraes, M.A.B. Berreman effect applied to phase characterization of thin films supported on metallic substrates: The case of TiO2. Phys. Rev. B 2001, 64, 125404. [Google Scholar] [CrossRef] [Green Version]

- Jõgi, I.; Pärs, M.; Aarik, J.; Aidla, A.; Laan, M.; Sundqvist, J.; Oberbeck, L.; Heitmann, J.; Kukli, K. Conformity and structure of titanium oxide films grown by atomic layer deposition on silicon substrates. Thin Solid Films 2008, 516, 4855–4862. [Google Scholar] [CrossRef]

- Hausmann, D.M.; Kim, E.; Becker, J.; Gordon, R.G. Atomic Layer Deposition of Hafnium and Zirconium Oxides Using Metal Amide Precursors. Chem. Mater. 2002, 14, 4350–4358. [Google Scholar] [CrossRef]

- Gordon, R.G.; Hausmann, D.; Kim, E.; Shepard, J. A Kinetic Model for Step Coverage by Atomic Layer Deposition in Narrow Holes or Trenches. Chem. Vap. Depos. 2003, 9, 73–78. [Google Scholar] [CrossRef]

- Ren, Y.; Nursam, N.M.; Wang, D.; Weber, K.J. Charge stability in LPCVD silicon nitride for surface passivation of silicon solar cells. In Proceedings of the 2010 35th IEEE Photovoltaic Specialists Conference, Honolulu, HI, USA, 20–25 June 2010; pp. 000897–000901. [Google Scholar]

- Zhang, L.; Janotti, A.; Meng, A.C.; Tang, K.; Van de Walle, C.G.; McIntyre, P.C. Interfacial Cation-Defect Charge Dipoles in Stacked TiO2/Al2O3 Gate Dielectrics. ACS Appl. Mater. Interfaces 2018, 10, 5140–5146. [Google Scholar] [CrossRef] [PubMed]

- Lenzlinger, M.; Snow, E.H. Fowler—Nordheim Tunneling into Thermally Grown SiO2. J. Appl. Phys. 1969, 40, 278–283. [Google Scholar] [CrossRef]

- Padovani, A.; Larcher, L.; Marca, V.D.; Pavan, P.; Park, H.; Bersuker, G. Charge trapping in alumina and its impact on the operation of metal-alumina-nitride-oxide-silicon memories: Experiments and simulations. J. Appl. Phys. 2011, 110, 014505. [Google Scholar] [CrossRef]

- Schmitz, J.; Cubaynes, F.N.; Havens, R.J.; De Kort, R.; Scholten, A.J.; Tiemeijer, L.F. RF capacitance-voltage characterization of MOSFETs with high leakage dielectrics. IEEE Electron Device Lett. 2003, 24, 37–39. [Google Scholar] [CrossRef] [Green Version]

- Choi, C.-H.; Goo, J.-S.; Oh, T.-Y.; Yu, Z.; Dutton, R.W.; Bayoumi, A.; Min, C.; Voorde, P.V.; Vook, D.; Diaz, C.H. MOS C-V characterization of ultrathin gate oxide thickness (1.3–1.8 nm). IEEE Electron Device Lett. 1999, 20, 292–294. [Google Scholar] [CrossRef]

- Alimardani, N.; King, S.W.; French, B.L.; Tan, C.; Lampert, B.P.; Conley, J.F., Jr. Investigation of the impact of insulator material on the performance of dissimilar electrode metal-insulator-metal diodes. J. Appl. Phys. 2014, 116, 024508. [Google Scholar] [CrossRef] [Green Version]

- Yang, X.; Zheng, P.; Bi, Q.; Weber, K. Silicon heterojunction solar cells with electron selective TiOx contact. Sol. Energy Mater. Sol. Cells 2016, 150, 32–38. [Google Scholar] [CrossRef]

- Sankapal, B.R.; Lux-Steiner, M.C.; Ennaoui, A. Synthesis and characterization of anatase-TiO2 thin films. Appl. Surf. Sci. 2005, 239, 165–170. [Google Scholar] [CrossRef]

| Type | Template | Insulator | Capacitance Density (μF/cm2) | Leakage Current Density (A/cm2) | Electrode Area (cm2) | Ref. |

|---|---|---|---|---|---|---|

| MIM | ZnO-NR | Al2O3 (10 nm) | 6.3 × 10−3 (10 kHz) | 7.16 × 10−3 (1 V) | 0.25 | [27] |

| MOS | P-Si | Al2O3 (50 nm) | 2.5 (10 kHz) | 5.27 × 10−5 (1 V) | 1.13 × 10−2 ~ 1.33 × 10−2 | [28] |

| MIM | Si-TR | Al2O3 (9~10 nm) | 3.62 (200 Hz) | 3 × 10−9 (1 V) | 3.3 × 10−3 | [29] |

| MIM | AAO | Al2O3 (10 nm) | 3.7 (200 kHz) | 1.7 × 10−7 (1 V) | 1.0 × 10−4 | [30] |

| MOS | SiNW | Al2O3 (10 nm) | 4.1 (1 kHz) | 1.49 × 10−9 (−1 V) | 2.5 × 10−5 | [5] |

| MOS | SiNW | Al2O3 (10 nm) | 18 (1 kHz) | 4.0 × 10−6 (1 V) | 1 × 10−4 | [7] |

| MIM | AAO | Al2O3 (7 nm) | 26.2 ± 1.5 (20 Hz) | 4.3 × 10−10 (0.7 V) | - | [31] |

| MIM | AAO | Al2O3 (6.6 nm) | 100 (20 Hz and DC) | 6.63 × 10−10 (1 V) | 1.27 × 10−4 | [6] |

| MIM | Flat | Al2O3 (6 nm)/ TiO2 (20 nm)/ Al2O3 (6 nm) | 2.13 (1 V, 1 MHz) | 4.71 × 10−13 (1 V) | 6 × 10−6 | [19] |

| MIM | Flat | Anatase TiO2 (4 nm)/ Al2O3 (1.25 nm)/ Rutile TiO2 (4 nm) | 4.26 (−1 V, 1 MHz) | 9.41 × 10−5 (−1 V) | 3.53 × 10−4 | [25] |

| MOS | Flat | (TiO2)x (2.5 nm)/ (Al2O3)y (2.5 nm) | 6.96 (1 V, 1 MHz) | 5.31 × 10−6 (1 V) | 7.85 × 10−5 | [23] |

| MOS | SiNW | Al2O3 (3.6 nm)/ TiO2 (15.2 nm)/Al2O3 (3.7 nm) | 0.99 (−1 V, 1 MHz) 5.9 (−4 V, 1 MHz) 84 (−10 V, 1 MHz) | 3.81 × 10−4 (−1 V) 7.45 × 10−1 (−4 V) | 1.96 × 10−3 | This study |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nezasa, R.; Gotoh, K.; Kato, S.; Miyamoto, S.; Usami, N.; Kurokawa, Y. Fabrication of Silicon Nanowire Metal-Oxide-Semiconductor Capacitors with Al2O3/TiO2/Al2O3 Stacked Dielectric Films for the Application to Energy Storage Devices. Energies 2021, 14, 4538. https://0-doi-org.brum.beds.ac.uk/10.3390/en14154538

Nezasa R, Gotoh K, Kato S, Miyamoto S, Usami N, Kurokawa Y. Fabrication of Silicon Nanowire Metal-Oxide-Semiconductor Capacitors with Al2O3/TiO2/Al2O3 Stacked Dielectric Films for the Application to Energy Storage Devices. Energies. 2021; 14(15):4538. https://0-doi-org.brum.beds.ac.uk/10.3390/en14154538

Chicago/Turabian StyleNezasa, Ryota, Kazuhiro Gotoh, Shinya Kato, Satoru Miyamoto, Noritaka Usami, and Yasuyoshi Kurokawa. 2021. "Fabrication of Silicon Nanowire Metal-Oxide-Semiconductor Capacitors with Al2O3/TiO2/Al2O3 Stacked Dielectric Films for the Application to Energy Storage Devices" Energies 14, no. 15: 4538. https://0-doi-org.brum.beds.ac.uk/10.3390/en14154538