Energy Efficiency in Slew-Rate Enhanced Single-Stage OTAs for Switched-Capacitor Applications

Abstract

:1. Introduction

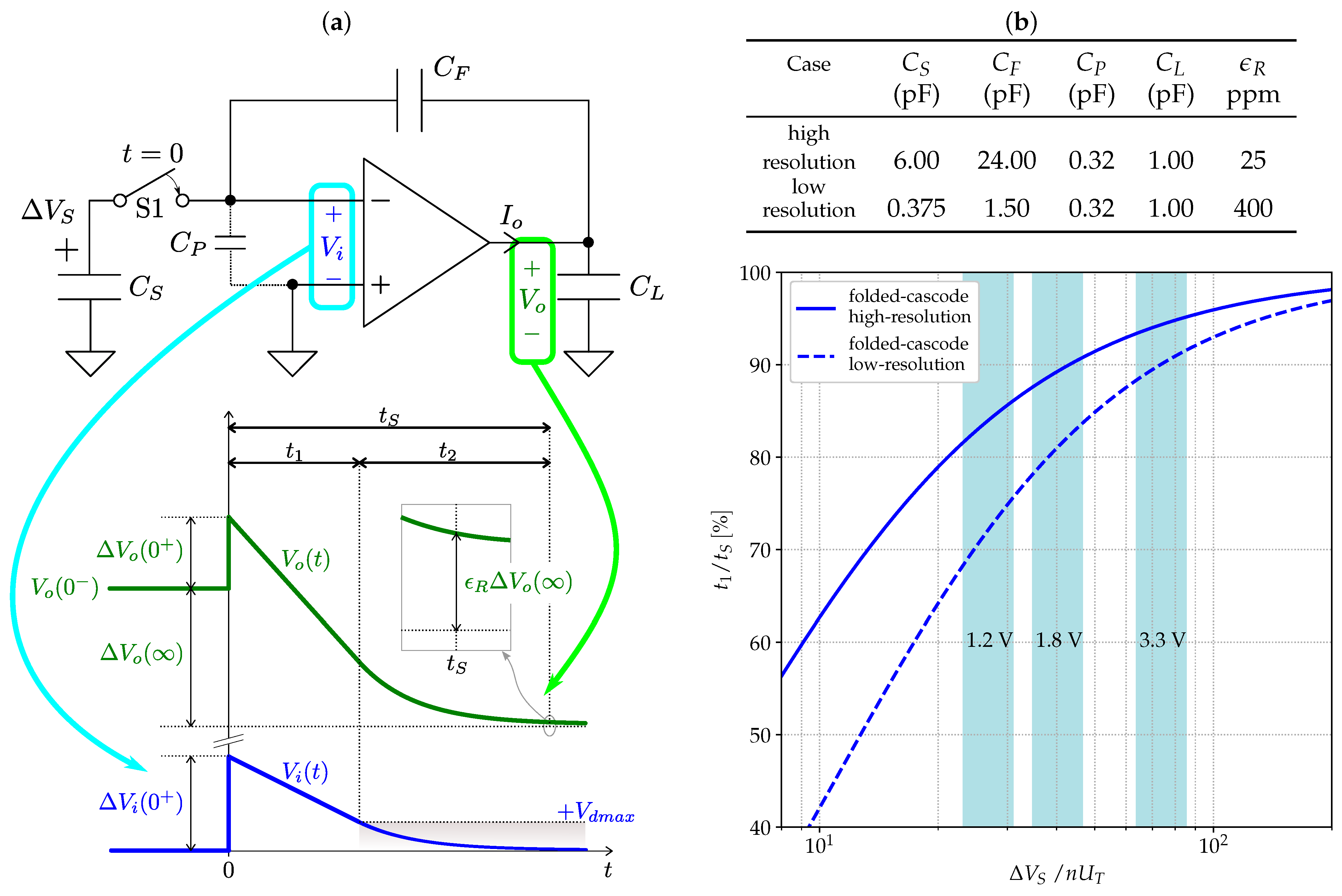

2. Extened Settling-Time Model

2.1. System-Level Settling Model

- acts as a normalizing unit for taking into account system-level specifications regarding the capacitive load , the input step amplitude , and the current consumption .

- and : both parameters mainly depend on the capacitive feedback network , , and the OTA’s input parasitic capacitance .

- expresses the efficiency by which the OTA uses the given to produce its output current when operating in slew-rate region.

- expresses the efficiency by which the OTA uses the given to produce large transconductance when operating in linear region.

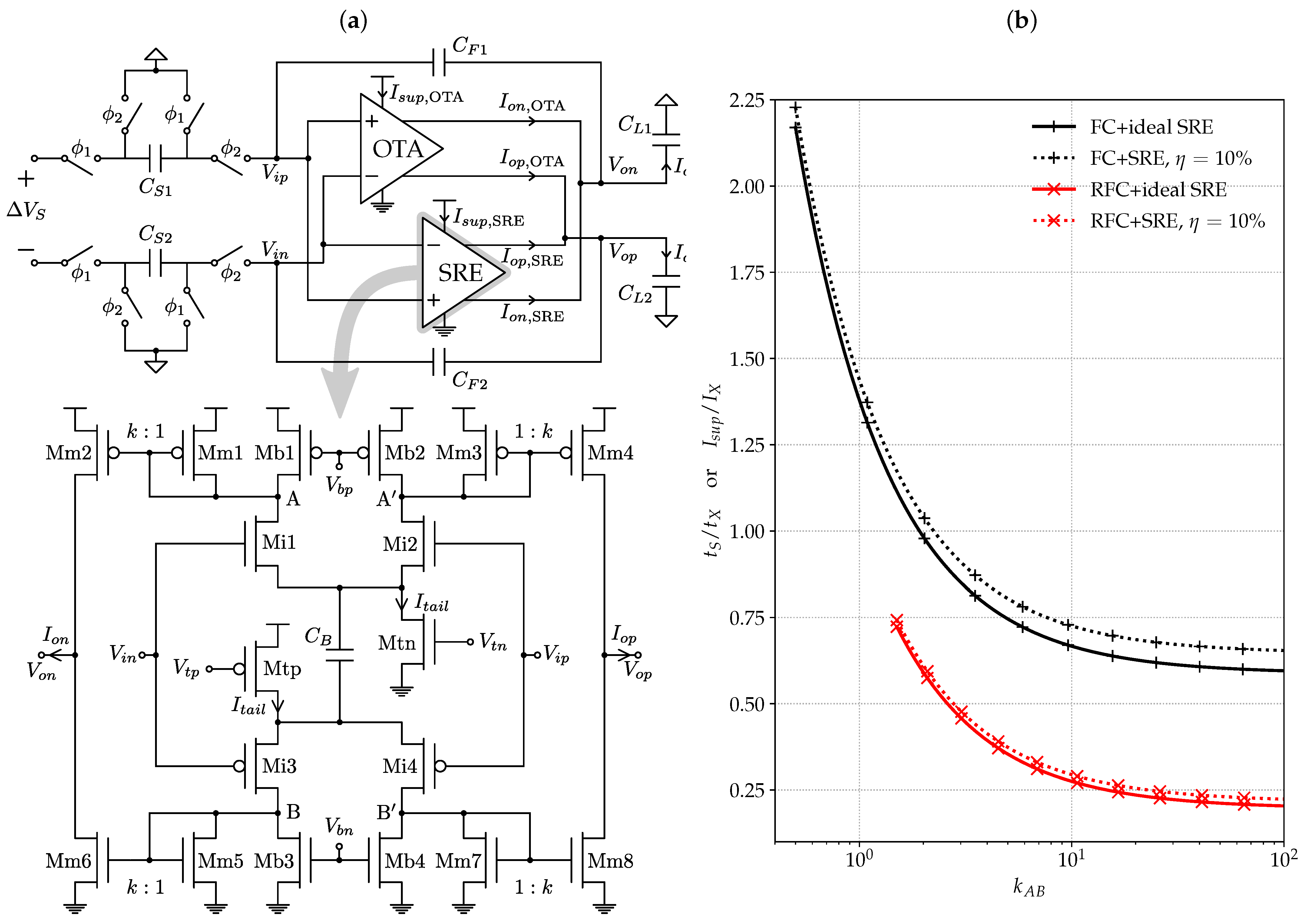

2.2. Model Extension to OTA/SRE Systems

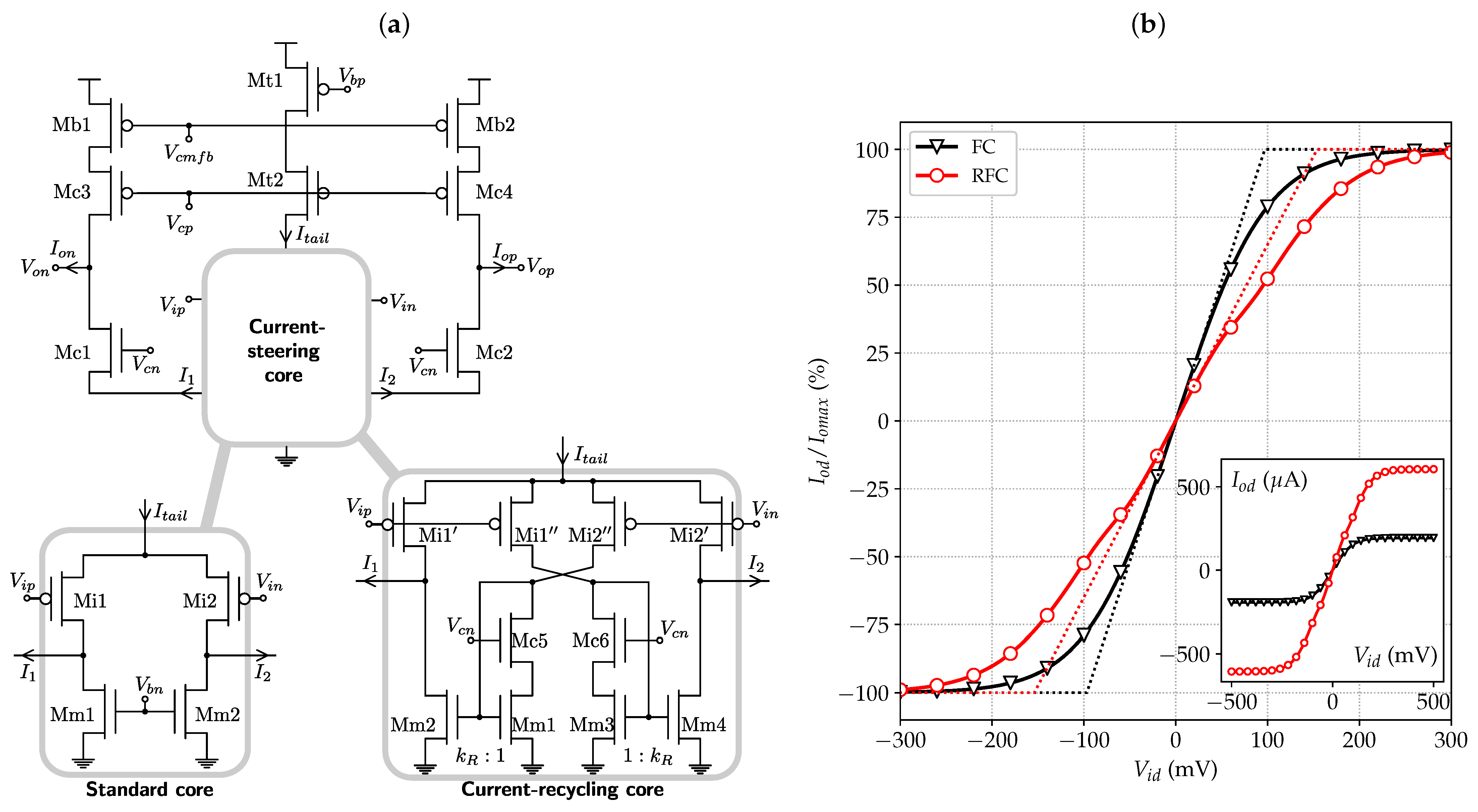

2.3. Model Extension to Advanced OTA Topologies

3. Energy Efficiency of OTA/SRE Systems

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Sansen, W.M.C.; Qiuting, H.; Halonen, K.A.I. Transient analysis of charge-transfer in SC filters-gain error and distortion. IEEE J. Solid-State Circuits 1987, 22, 268–276. [Google Scholar] [CrossRef]

- Robertini, A.; Goette, J.; Guggenbuhl, W. Nonlinear distortions in SC-integrators due to nonideal switches and amplifiers. IEEE Int. Sympos. Circuits Syst. 1989, 3, 1692–1695. [Google Scholar] [CrossRef]

- Robertini, A.; Guggenbuhl, W. Errors in SC circuits derived from linearly modeled amplifiers and switches. IEEE Trans. Circuits Syst. I Fund. Theory Appl. 1992, 39, 93–101. [Google Scholar] [CrossRef]

- Wang, F.; Harjani, R. Power analysis and optimal design of op amps for oversampled converters. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 1999, 46, 359–369. [Google Scholar] [CrossRef]

- del Rio, R.; Medeiro, F.; Perez-Verdu, B.; Rodriguez-Vazquez, A. Reliable analysis of settling errors in SC integrators-application to the design of high-speed ΣΔ modulators. In Proceedings of the 2000 IEEE International Symposium on Circuits and Systems (ISCAS), Geneva, Switzerland, 28–31 May 2000; Volume 4, pp. 417–420. [Google Scholar] [CrossRef] [Green Version]

- Suarez, G.; Jimenez, M.; Fernandez, F.O. Behavioral Modeling Methods for Switched-Capacitor ΣΔ Modulators. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 1236–1244. [Google Scholar] [CrossRef]

- Karnstedt, C. Optimizing Power of Switched Capacitor Integrators in Sigma-Delta Modulators. IEEE Circuits Syst. Mag. 2010, 10, 64–71. [Google Scholar] [CrossRef]

- Boni, A.; Giuffredi, L.; Pietrini, G.; Magnanini, A.; Tonelli, M. Design-oriented model for power-driven design optimization of SC-ΔΣ modulators. Int. J. Circ. Theor. Appl. 2018, 46, 707–728. [Google Scholar] [CrossRef]

- Hollis, T.M.; Comer, D.J.; Comer, D.T. Optimization of MOS amplifier performance through channel length and inversion level selection. In Proceedings of the IEEE Transactions on Circuits and Systems II: Express Briefs, Taormina, Italy, 2–3 September 2005; Volume 52, pp. 545–549. [Google Scholar] [CrossRef]

- Catania, A.; Cicalini, M.; Dei, M.; Piotto, M.; Bruschi, P. Performance Analysis and Design Optimization of Parallel-Type Slew-Rate Enhancers for Switched-Capacitor Applications. Electronics 2020, 9, 1949. [Google Scholar] [CrossRef]

- Nagaraj, K. Slew rate enhancement method for folded-cascode amplifiers. Electr. Lett. 1989, 25, 19. [Google Scholar] [CrossRef]

- Nagaraj, K. CMOS amplifiers incorporating a novel slew rate enhancement technique. In Proceedings of the IEEE Custom Integrated Circuits Conference, Boston, MA, USA, 13–16 May 1990; pp. 11.6/1–11.6/5. [Google Scholar] [CrossRef]

- Assaad, R.S.; Silva-Martinez, J. The Recycling Folded Cascode: A General Enhancement of the Folded Cascode Amplifier. IEEE J. Solid-State Circuits 2009, 44, 2535–2542. [Google Scholar] [CrossRef]

- Fiorenza, J.K.; Sepke, T.; Holloway, P.; Sodini, C.G.; Lee, H. Comparator-Based Switched-Capacitor Circuits for Scaled CMOS Technologies. IEEE J. Solid-State Circuits 2006, 41, 2658–2668. [Google Scholar] [CrossRef]

- Lopez-Martin, A.J.; Baswa, S.; Ramirez-Angulo, J.; Carvajal, R.G. Low-Voltage Super class AB CMOS OTA cells with very high slew rate and power efficiency. IEEE J. Solid-State Circuits 2005, 40, 1068–1077. [Google Scholar] [CrossRef]

- Sutula, S.; Dei, M.; Terés, L.; Serra-Graells, F. Variable-Mirror Amplifier: A New Family of Process-Independent Class-AB Single-Stage OTAs for Low-Power SC Circuits. IEEE Trans. Circuits Syst. I Regular Pap. 2016, 63, 1101–1110. [Google Scholar] [CrossRef] [Green Version]

- Cisneros-Fernández, J.; Terés, L.; Dei, M.; Serra-Graells, F. Design methodology for power-efficient SC delta-sigma modulators based on switched-VMAs. In Proceedings of the 2017 32nd Conference on Design of Circuits and Integrated Systems (DCIS), Barcelona, Spain, 22–24 November 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Cisneros-Fernández, J.; Serra-Graells, F.; Terés, L.; Dei, M. A Compact Switched-Capacitor Multi-Bit Quantizer for Low-Power High-Resolution Delta-Sigma ADCs. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar] [CrossRef]

| Specifications | ||

|---|---|---|

| 15 | ns | |

| 1.8 | V | |

| 1.5 | pF | |

| 6.0 | pF | |

| 1.0 | pF | |

| 100 | ppm | |

| SRE, A, fF. | ||

| L (nm) | W (m) | |

| Mi1-2 | 180 | 1.50 |

| Mi3-4 | 180 | 4.50 |

| Mm1, Mm3 | 180 | 1.62 |

| Mm2, Mm4 | 180 | 48.60 |

| Mm5, Mm7 | 180 | 0.54 |

| Mm6, Mm8 | 180 | 16.20 |

| Mtn | 1000 | 2.88 |

| Mtp | 1000 | 0.96 |

| Mb1-2 | 1000 | 2.16 |

| Mb3-4 | 1000 | 0.72 |

| L (nm) | W (m) | |

| Mi1-2 | 180 | 480 |

| Mm1-2 | 400 | 32 |

| Mc1-2 | 180 | 72 |

| Mc3-4 | 180 | 288 |

| Mb1-2 | 400 | 73 |

| Mt1 | 400 | 146 |

| Mt2 | 180 | 576 |

| L (nm) | W (m) | |

| Mi1-2 | 180 | 240 |

| Mm1-2 | 400 | 32 |

| Mc1-2 | 180 | 72 |

| Mc3-4 | 180 | 288 |

| Mb1-2 | 400 | 73 |

| Mt1 | 400 | 146 |

| Mt2 | 180 | 576 |

| L (nm) | W (m) | |

| Mi1-1″-2-2″ | 180 | 156 |

| Mm1-3 | 400 | 16 |

| Mm2-4 | 400 | 48 |

| Mc5-6 | 180 | 36 |

| Mc1-2 | 180 | 72 |

| Mc3-4 | 180 | 28 |

| Mb1-2 | 400 | 73 |

| Mt1 | 400 | 146 |

| Mt2 | 180 | 72 |

| L (nm) | W (m) | |

| Mi1-1″-2-2″ | 180 | 78 |

| Mm1-3 | 400 | 16 |

| Mm2-4 | 400 | 48 |

| Mc5-6 | 180 | 36 |

| Mc1-2 | 180 | 72 |

| Mc3-4 | 180 | 28 |

| Mb1-2 | 400 | 73 |

| Mt1 | 400 | 146 |

| Mt2 | 180 | 72 |

| FC1 | FC2 + SRE | RFC1 | RFC2 + SRE | |

|---|---|---|---|---|

| (ns) | 14.98 | 14.69 | 14.64 | 14.61 |

| (pJ) | 21.93 | 14.49 | 15.52 | 10.3 |

| (fF) | 701 | 358 | 528 | 270 |

| (pJ) | 3.13 | 3.14 | 3.13 | 3.15 |

| 7.00 | 4.61 | 4.95 | 3.27 | |

| (%) | 49.8 | 10.5 | 38.8 | 11.9 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Catania, A.; Cicalini, M.; Piotto, M.; Bruschi, P.; Dei, M. Energy Efficiency in Slew-Rate Enhanced Single-Stage OTAs for Switched-Capacitor Applications. J. Low Power Electron. Appl. 2021, 11, 1. https://0-doi-org.brum.beds.ac.uk/10.3390/jlpea11010001

Catania A, Cicalini M, Piotto M, Bruschi P, Dei M. Energy Efficiency in Slew-Rate Enhanced Single-Stage OTAs for Switched-Capacitor Applications. Journal of Low Power Electronics and Applications. 2021; 11(1):1. https://0-doi-org.brum.beds.ac.uk/10.3390/jlpea11010001

Chicago/Turabian StyleCatania, Alessandro, Mattia Cicalini, Massimo Piotto, Paolo Bruschi, and Michele Dei. 2021. "Energy Efficiency in Slew-Rate Enhanced Single-Stage OTAs for Switched-Capacitor Applications" Journal of Low Power Electronics and Applications 11, no. 1: 1. https://0-doi-org.brum.beds.ac.uk/10.3390/jlpea11010001