SET Pulse Characterization and SER Estimation in Combinational Logic with Placement and Multiple Transient Faults Considerations †

Abstract

:1. Introduction

2. Related Work

3. SET Modeling and Characterization

3.1. Current Pulse Model

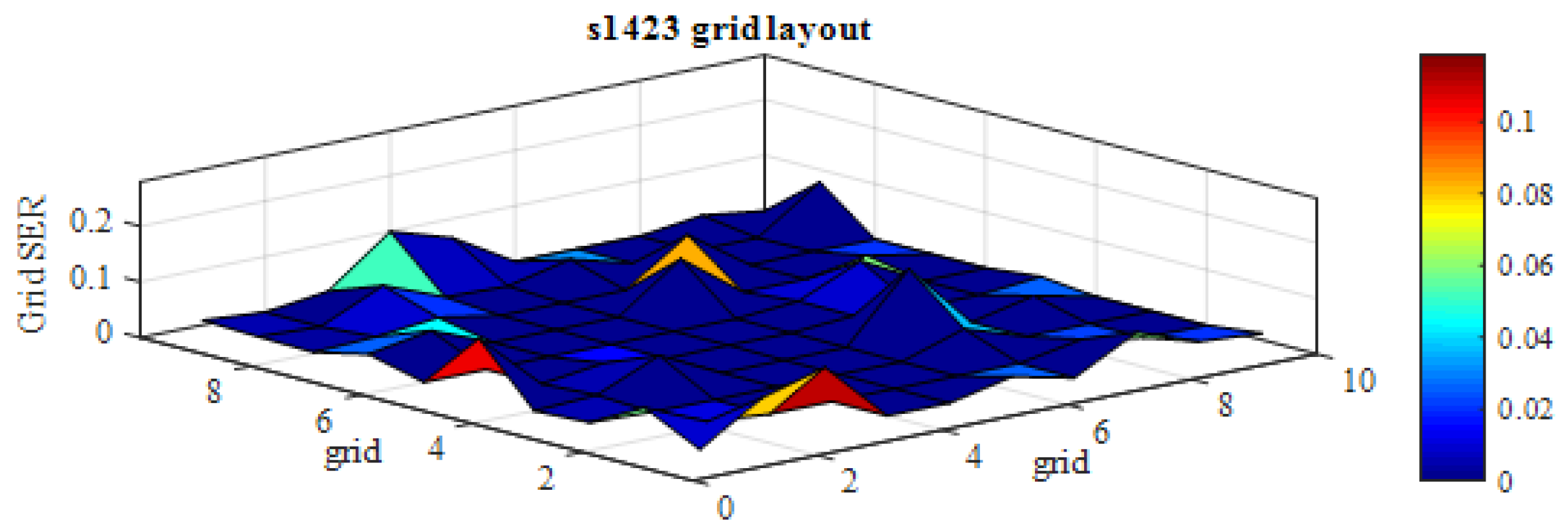

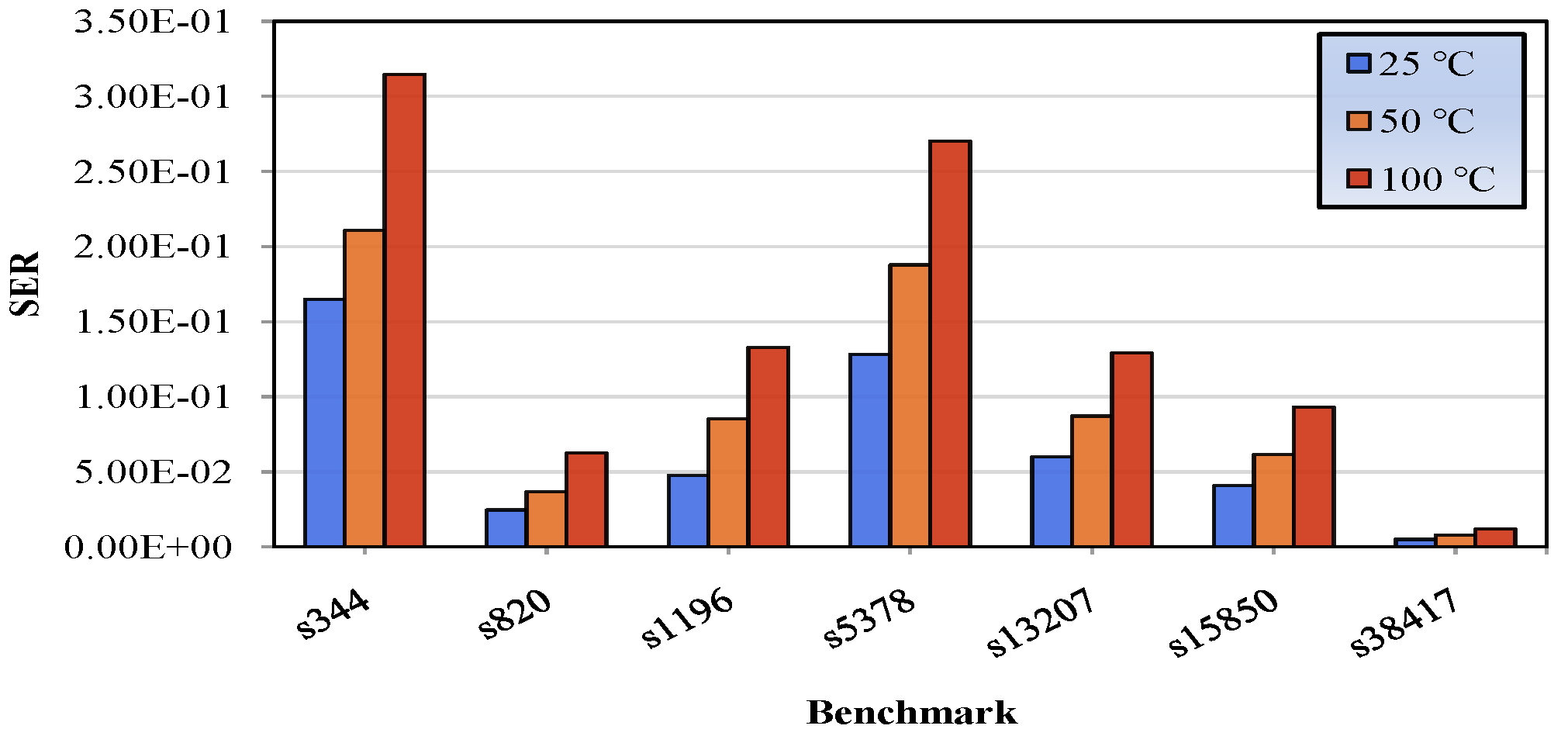

3.2. Transistor Pulse Injection

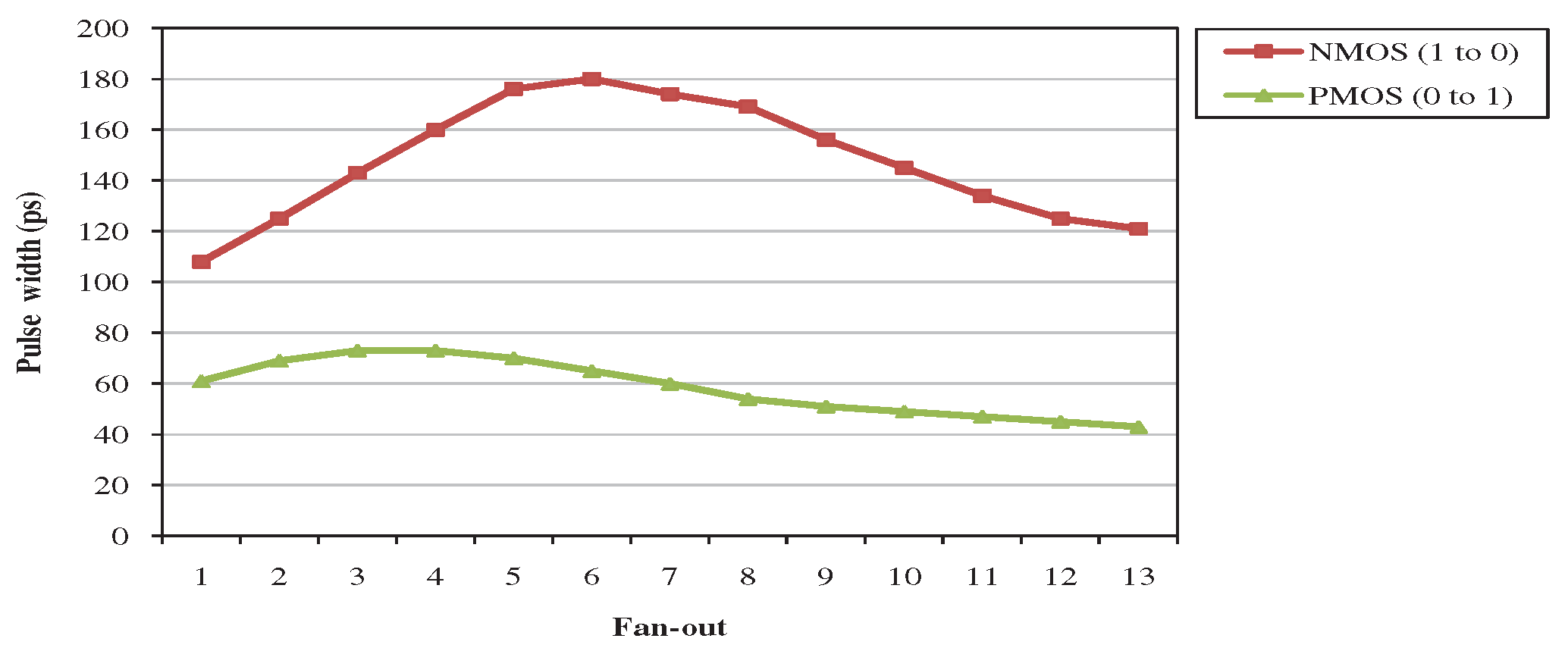

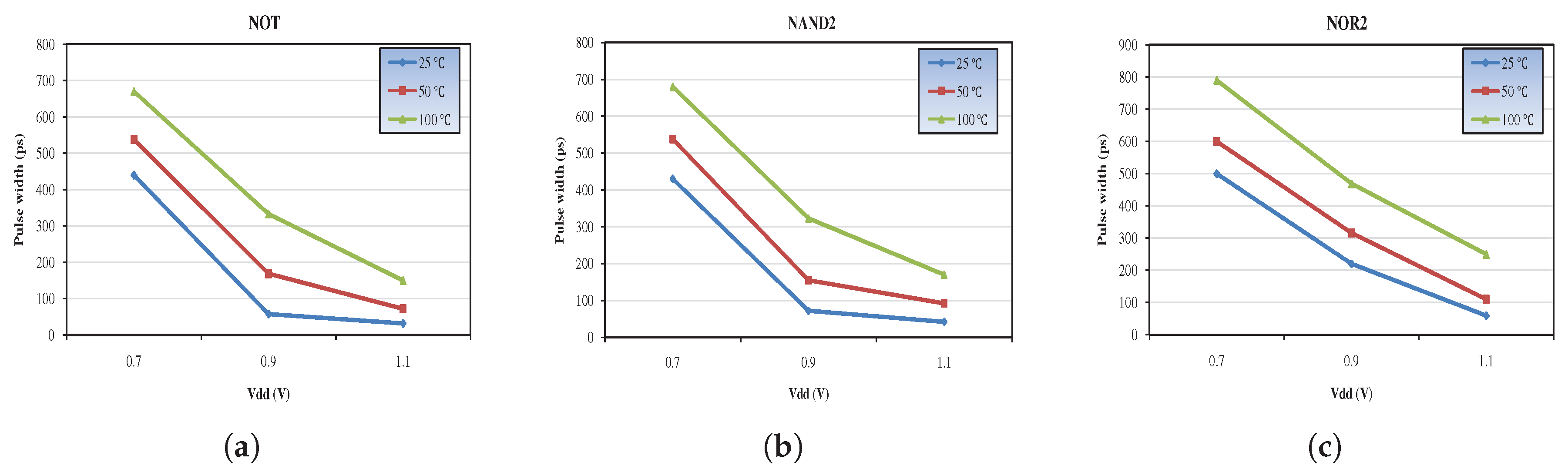

3.3. SET Pulse Characterization

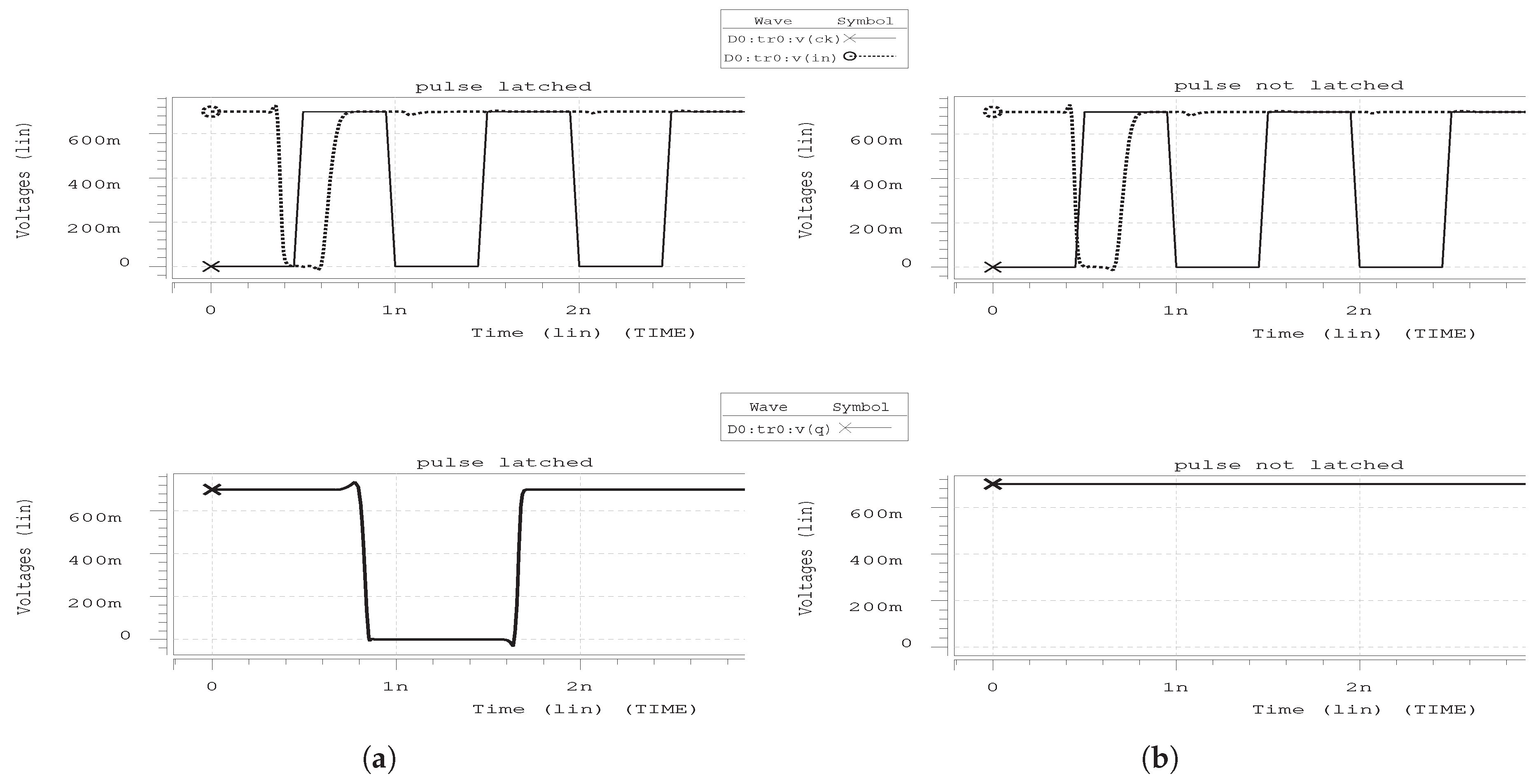

3.4. Propagation and Verification Framework

4. Proposed Methodology for SER Estimation

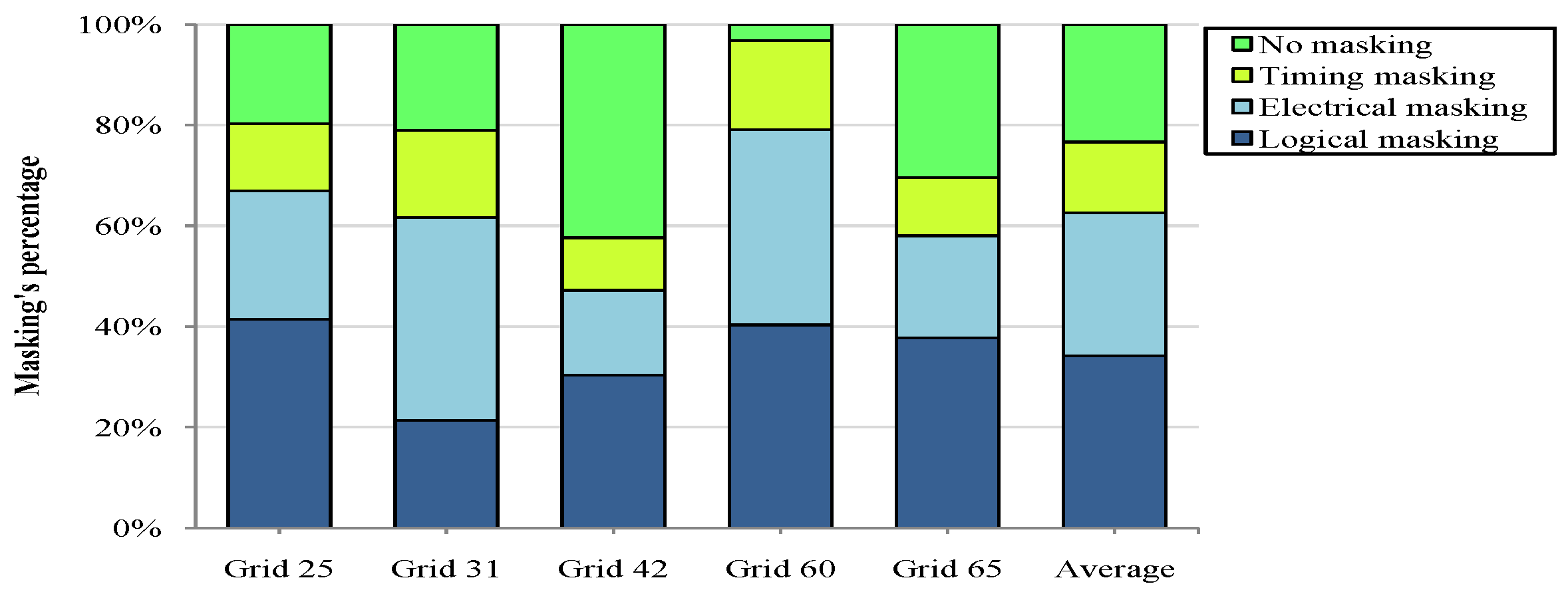

4.1. Masking Mechanisms

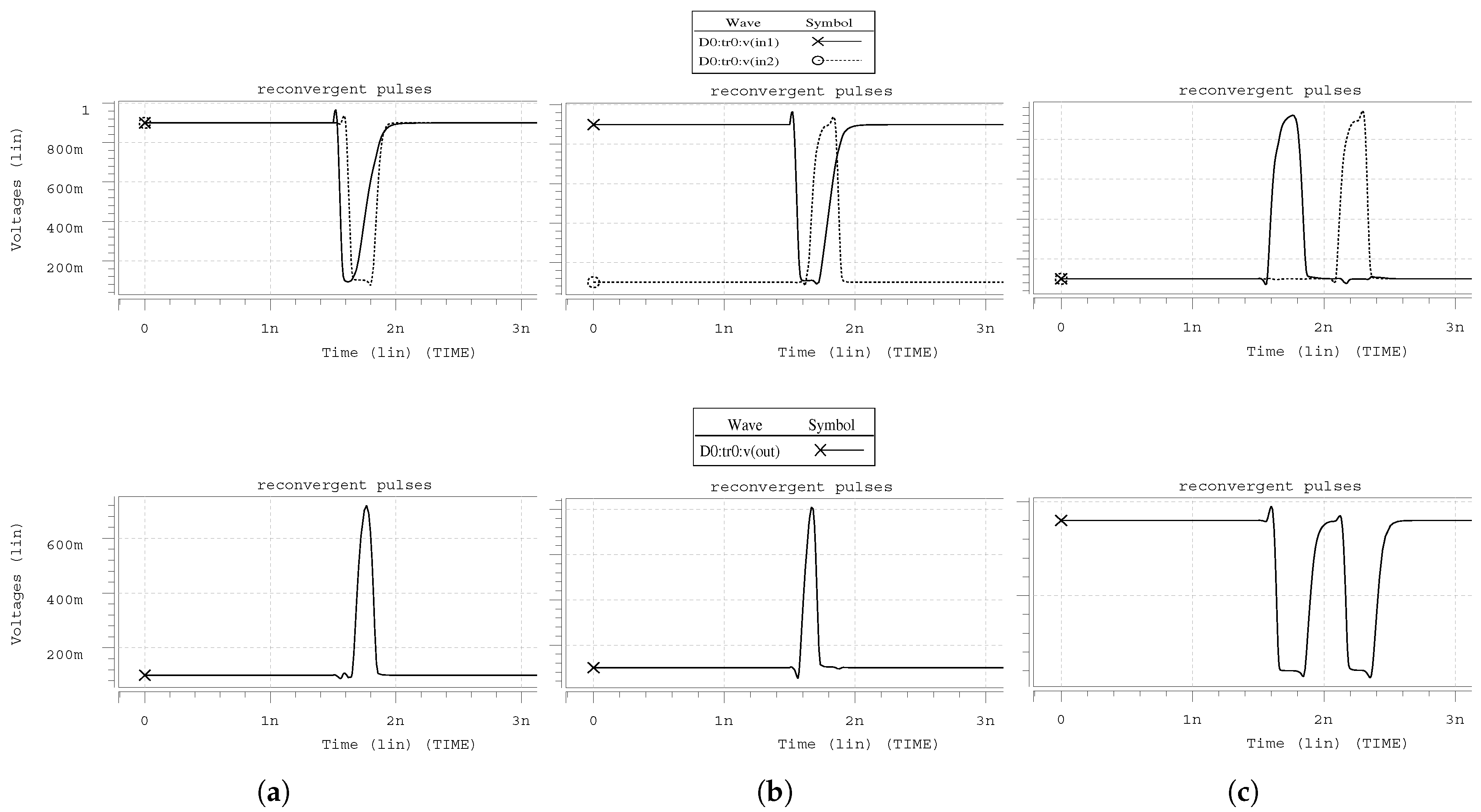

4.2. Reconvergent Transient Faults

4.3. Multiple Transient Faults Behavior

4.4. Algorithm for SER Εstimation

| Algorithm 1: SER Estimation |

|

5. Gate Sensitivity

6. Experimental Results

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| CMOS | Complementary Metal–Oxide–Semiconductor |

| SER | Soft Error Rate |

| VLSI | Very Large-Scale Integration |

| IC | Integrated Circuit |

| SET | Single Event Transient |

| SEMT | Single Event Multiple Transient |

| TF | Transient Fault |

| MTF | Multiple Transient Fault |

| FF | Flip-Flop |

| DEF | Design Exchange Format |

| GDSII | Graphic Database System |

| GLP | Glitch Latching Probability |

References

- Campos, A.; Espinosa, G.; Torres Jacome, A.; Tlelo-Cuautle, E. On the Prediction of the Threshold Voltage Degradation in CMOS Technology Due to Bias-Temperature Instability. Electronics 2019, 7, 427. [Google Scholar] [CrossRef] [Green Version]

- May, T.C.; Woods, M.H. Alpha-particle-induced soft errors in dynamic memories. IEEE Trans. Electron Devices 1979, 26, 2–9. [Google Scholar] [CrossRef]

- Ziegler, J.F. Terrestrial cosmic rays. IBM J. Res. Dev. 1996, 40, 19–39. [Google Scholar] [CrossRef]

- Hazucha, P.; Svensson, C. Impact of CMOS technology scaling on the atmospheric neutron soft error rate. IEEE Trans. Nucl. Sci. 2000, 47, 2586–2594. [Google Scholar] [CrossRef]

- Seifert, N.; Slankard, P.; Kirsch, M.; Narasimham, B.; Zia, V.; Brookreson, C.; Vo, A.; Mitra, S.; Gill, B.; Maiz, J. Radiation-induced soft error rates of advanced CMOS bulk devices. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), San Jose, CA, USA, 26–30 March 2006; pp. 217–225. [Google Scholar]

- Chandra, V.; Aitken, R. Impact of Technology and Voltage Scaling on the Soft Error Susceptibility in Nanoscale CMOS. In Proceedings of the IEEE International Symposium on Defect and Fault Tolerance of VLSI Systems, Boston, MA, USA, 1–3 October 2008; pp. 114–122. [Google Scholar]

- Carbajal-Gómez, V.; Tlelo-Cuautle, E.; Munoz-Pacheco, J.M.; De La Fraga, L.; Sanchez-Lopez, C.; Fernandez-Fernandez, F. Optimization and CMOS design of chaotic oscillators robust to PVT variations. Integration 2019, 65, 32–42. [Google Scholar] [CrossRef]

- HSPICE® User Guide: Simulation and Analysis, Version b-2008.09. 2008. Available online: https://cseweb.ucsd.edu/classes/wi10/cse241a/assign/hspice_sa.pdf (accessed on 6 January 2020).

- Tlelo-Coyotecatl, E.; Diaz-Sanchez, A.; Rocha-Pérez, J.; Vazquez-Gonzalez, J.L.; Sánchez-Gaspariano, L.; Tlelo-Cuautle, E. Enhancing Q-Factor in a Biquadratic Bandpass Filter Implemented with Opamps. Technologies 2019, 7, 64. [Google Scholar] [CrossRef] [Green Version]

- Paliaroutis, G.I.; Tsoumanis, P.; Evmorfopoulos, N.; Dimitriou, G.; Stamoulis, G.I. Multiple Transient Faults in Combinational Logic with Placement Considerations. In Proceedings of the 8th International Conference on Modern Circuits and Systems Technologies on Electronics and Communications (MOCAST), Thessaloniki, Greece, 13–15 May 2019; pp. 1–4. [Google Scholar]

- Gadlage, M.J.; Ahlbin, J.R.; Ramachandran, V.; Gouker, P.; Dinkins, C.A.; Bhuva, B.L.; Narasimham, B.; Schrimpf, R.D.; McCurdy, M.W.; Alles, M.L.; et al. Temperature Dependence of Digital Single-Event Transients in Bulk and Fully-Depleted SOI Technologies. IEEE Trans. Nucl. Sci. 2009, 56, 3115–3121. [Google Scholar] [CrossRef]

- Glorieux, M.; Evans, A.; Ferlet-Cavrois, V.; Boatella-Polo, C.; Alexandrescu, D.; Clerc, S.; Gasiot, G.; Roche, P. Detailed SET Measurement and Characterization of a 65nm Bulk Technology. IEEE Trans. Nucl. Sci. 2016, 64, 81–88. [Google Scholar] [CrossRef]

- Dixit, A.; Wood, A. The impact of new technology on soft error rates. In Proceedings of the International Reliability Physics Symposium, Monterey, CA, USA, 10–14 April 2011; pp. 5B.4.1–5B.4.7. [Google Scholar]

- Cha, H.; Patel, J.H. A logic-level model for α-particle hits in CMOS circuits. In Proceedings of the IEEE International Conference on Computer Design ICCD’93, Cambridge, MA, USA, 3–6 October 1993; pp. 538–542. [Google Scholar]

- Xu, J.; Guo, Y.; Song, R.; Liang, B.; Chi, Y. Supply Voltage and Temperature Dependence of Single-Event Transient in 28-nm FDSOI MOSFETs. Symmetry 2019, 11, 793. [Google Scholar] [CrossRef] [Green Version]

- Wang, F.; Xie, Y. Soft Error Rate Analysis for Combinational Logic Using an Accurate Electrical Masking Model. IEEE Trans. Depend. Sec. Comp. 2011, 8, 137–146. [Google Scholar] [CrossRef]

- Rao, R.R.; Chopra, K.; Blaauw, D.T.; Sylvester, D.M. Computing the Soft Error Rate of a Combinational Logic Circuit Using Parameterized Descriptors. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2007, 26, 468–479. [Google Scholar] [CrossRef]

- Zhang, M.; ShanbhagHazucha, N.R. Soft-Error-Rate-Analysis (SERA) methodology. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2006, 25, 2140–2155. [Google Scholar] [CrossRef]

- Anglada, M.; Canal, R.; Aragón, J.L.; González, A. MASkIt: Soft error rate estimation for combinational circuits. In Proceedings of the IEEE 34th International Conference on Computer Design (ICCD), Scottsdale, AZ, USA, 2–5 October 2016; pp. 614–621. [Google Scholar]

- Wang, F.; Agrawal, V.D. Soft error rate determination for nanoscale sequential logic. In Proceedings of the 11th International Symposium on Quality Electronic Design (ISQED), San Jose, CA, USA, 22–24 March 2010; pp. 225–230. [Google Scholar]

- Chang, A.C.-C.; Huang, R.H.; Wen, C.H. CASSER: A closed-form analysis framework for statistical soft error rate. IEEE Trans. Very Large Scale Integr. Syst. 2013, 21, 1837–1848. [Google Scholar] [CrossRef]

- Kiddie, B.T.; Robinson, W.H.; Limbrick, D.B. Single-Event Multiple-Transients (SEMT): Circuit characterization and analysis. In Proceedings of the IEEE Workshop Silicon Errors in Logic-System Effects (SELSE), Palo Alto, CA, USA, 26–27 March 2013. [Google Scholar]

- Evans, A.; Glorieux, M.; Alexandrescu, D.; Polo, C.B.; Ferlet-Cavrois, V. Single event multiple transient (SEMT) measurements in 65 nm bulk technology. In Proceedings of the 16th European Conference on Radiation and Its Effects on Components and Systems, Bremen, Germany, 19–23 September 2016; pp. 1–6. [Google Scholar]

- Rossi, D.; Omana, M.; Toma, F.; Metra, C. Multiple transient faults in logic: An issue for next generation ICs? In Proceedings of the IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, Monterey, CA, USA, 3–5 October 2005; pp. 352–360. [Google Scholar]

- Nanditha, P.R.; Sarik, S.; Desai, M.P. On the likelihood of multiple bit upsets in logic circuits. arXiv 2014, arXiv:1401.1003. [Google Scholar]

- Huang, H.; Wen, C.H.-P. Layout-Based soft error rate estimation framework considering multiple transient faults—From device to circuit level. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2016, 35, 586–597. [Google Scholar] [CrossRef]

- Ebrahimi, M.; Asadi, H.; Tahoori, M.B. A layout-based approach for multiple event transient analysis. In Proceedings of the 50th ACM/EDAC/IEEE Design Automation Conference (DAC), Austin, TX, USA, 29 May–7 June 2013; pp. 1–6. [Google Scholar]

- Miskov-Zivanov, N.; Marculescu, D. Multiple transient faults in combinational and sequential circuits: A systematic approach. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2010, 29, 1614–1627. [Google Scholar] [CrossRef]

- Fazeli, M.; Ahmadian, S.N.; Miremadi, S.G.; Asadi, H.; Tahoori, M.B. Soft error rate estimation of digital circuits in the presence of Multiple Event Transients (METs). In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 14–18 March 2011; pp. 1–6. [Google Scholar]

- Paliaroutis, G.I.; Tsoumanis, P.; Evmorfopoulos, N.; Dimitriou, G.; Stamoulis, G.I. A placement-aware soft error rate estimation of combinational circuits for multiple transient faults in CMOS technology. In Proceedings of the IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems, Chicago, IL, USA, 8–10 October 2018; pp. 1–6. [Google Scholar]

- Du, Y.; Chen, S. A novel layout-based single event transient injection approach to evaluate the soft error rate of large combinational circuits in Complimentary Metal-Oxide-Semiconductor bulk technology. IEEE Trans. Reliab. 2016, 65, 248–255. [Google Scholar] [CrossRef]

- Li, J.; Draper, J. Accelerated Soft-Error-Rate (SER) estimation for combinational and sequential circuits. ACM Trans. Des. Autom. Electr. Syst. 2017, 22, 57. [Google Scholar] [CrossRef]

- Cao, X.; Xiao, L.; Li, J.; Zhang, R.; Liu, S.; Wang, J. A layout-based soft error vulnerability estimation approach for combinational circuits considering Single Event Multiple Transients (SEMTs). IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2018, 38, 1109–1122. [Google Scholar] [CrossRef]

- Messenger, G.C. Collection of Charge on Junction Nodes from Ion Tracks. IEEE Trans. Nucl. Sci. 1982, 29, 2024–2031. [Google Scholar] [CrossRef]

- Srinivasan, G.R.; Murley, P.C.; Tang, H.K. Accurate, predictive modeling of soft error rate due to cosmic rays and chip alpha radiation. In Proceedings of the IEEE International Reliability Physics Symposium, San Jose, CA, USA, 11–14 April 1994; pp. 12–16. [Google Scholar]

- Naseer, R.; Draper, J.; Boulghassoul, Y.; DasGupta, S.; Witulski, A. Critical charge and set pulse widths for combinational logic in commercial 90nm cmos technology. In Proceedings of the 17th ACM Great Lakes Symposium on VLSI, Stresa, Lago Maggiore, Italy, 11–13 March 2007. [Google Scholar]

- Nangate 45nm Open Cell Library, Nangate Inc. 2009. Available online: http://www.nangate.com/ (accessed on 6 January 2020).

| Benchmark | Nodes | Inputs | Gates | FFs | SER | Ex. Time | |||

|---|---|---|---|---|---|---|---|---|---|

| SETs | SEMTs | ||||||||

| Fail. Rate | FIT | Fail. Rate | FIT | ||||||

| s27 | 17 | 4 | 13 | 3 | 0.221830 | 4.95 × 10−6 | 0.278987 | 6.22 × 10−6 | s |

| s298 | 169 | 3 | 166 | 14 | 0.105548 | 4.28 × 10−6 | 0.119706 | 4.86 × 10−6 | s |

| s344 | 240 | 9 | 231 | 15 | 0.151876 | 7.65 × 10−6 | 0.165033 | 8.32 × 10−6 | s |

| s349 | 224 | 9 | 215 | 15 | 0.147416 | 7.43 × 10−6 | 0.151563 | 7.63 × 10−6 | s |

| s382 | 196 | 3 | 193 | 21 | 0.147883 | 8.84 × 10−6 | 0.219213 | 1.31 × 10−5 | s |

| s400 | 203 | 3 | 200 | 21 | 0.152426 | 9.21 × 10−6 | 0.197017 | 1.19 × 10−5 | s |

| s420 | 252 | 19 | 233 | 16 | 0.118641 | 7.41 × 10−6 | 0.155258 | 9.70 × 10−6 | s |

| s526 | 280 | 3 | 277 | 21 | 0.158764 | 1.15 × 10−5 | 0.221793 | 1.61 × 10−5 | 1 s |

| s641 | 517 | 35 | 482 | 19 | 0.052395 | 4.85 × 10−6 | 0.068785 | 6.36 × 10−6 | 2 s |

| s713 | 539 | 35 | 504 | 19 | 0.046882 | 4.45 × 10−6 | 0.060003 | 5.70 × 10−6 | 2 s |

| s820 | 443 | 18 | 425 | 5 | 0.017064 | 1.52 × 10−6 | 0.024629 | 2.19 × 10−6 | 2 s |

| s953 | 496 | 16 | 480 | 29 | 0.200970 | 2.23 × 10−5 | 0.154886 | 1.71 × 10−5 | 7 s |

| s1196 | 762 | 14 | 748 | 18 | 0.036776 | 5.02 × 10−6 | 0.047549 | 6.48 × 10−6 | 4 s |

| s1238 | 768 | 14 | 754 | 18 | 0.036994 | 5.12 × 10−6 | 0.051779 | 7.17 × 10−6 | 4 s |

| s1423 | 1008 | 17 | 991 | 74 | 0.025936 | 6.60 × 10−5 | 0.034567 | 8.08 × 10−5 | 10 s |

| s1488 | 1211 | 8 | 1203 | 6 | 0.009252 | 1.68 × 10−6 | 0.018931 | 3.44 × 10−6 | 4 s |

| s5378 | 3053 | 35 | 3018 | 179 | 0.104812 | 7.20 × 10−5 | 0.128300 | 8.82 × 10−5 | m |

| s9234 | 7002 | 19 | 6983 | 228 | 0.043296 | 5.45 × 10−5 | 0.052699 | 6.55 × 10−5 | m |

| s13207 | 9608 | 31 | 9577 | 669 | 0.051429 | 1.10 × 10−4 | 0.059780 | 1.26 × 10−4 | m |

| s15850 | 12,115 | 14 | 12,101 | 597 | 0.031277 | 7.32 × 10−5 | 0.040679 | 9.53 × 10−5 | m |

| s35932 | 21,278 | 35 | 21,243 | 1728 | 0.050904 | 2.70 × 10−4 | 0.066115 | 3.51 × 10−4 | 58 m |

| s38417 | 24,874 | 28 | 23,815 | 1636 | 0.038741 | 1.08 × 10−2 | 0.051637 | 1.44 × 10−2 | 10 h |

| s38584 | 21,407 | 38 | 20,679 | 1426 | 0.030439 | 8.12 × 10−3 | 0.042658 | 1.12 × 10−2 | 7 h |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Paliaroutis, G.I.; Tsoumanis, P.; Evmorfopoulos, N.; Dimitriou, G.; Stamoulis, G.I. SET Pulse Characterization and SER Estimation in Combinational Logic with Placement and Multiple Transient Faults Considerations. Technologies 2020, 8, 5. https://0-doi-org.brum.beds.ac.uk/10.3390/technologies8010005

Paliaroutis GI, Tsoumanis P, Evmorfopoulos N, Dimitriou G, Stamoulis GI. SET Pulse Characterization and SER Estimation in Combinational Logic with Placement and Multiple Transient Faults Considerations. Technologies. 2020; 8(1):5. https://0-doi-org.brum.beds.ac.uk/10.3390/technologies8010005

Chicago/Turabian StylePaliaroutis, Georgios Ioannis, Pelopidas Tsoumanis, Nestor Evmorfopoulos, George Dimitriou, and Georgios I. Stamoulis. 2020. "SET Pulse Characterization and SER Estimation in Combinational Logic with Placement and Multiple Transient Faults Considerations" Technologies 8, no. 1: 5. https://0-doi-org.brum.beds.ac.uk/10.3390/technologies8010005