Neutral-Point Voltage Balancing Method for Three-Phase Three-Level Dual-Active-Bridge Converters

Abstract

:1. Introduction

2. Topology and Operating Principle of the 3L-DAB3

2.1. Topology of the 3L-DAB3

2.2. Operating Principle of the 3L-DAB3

- (1)

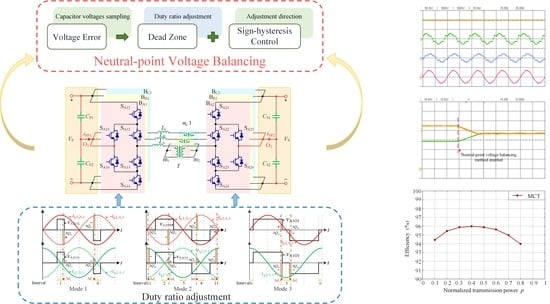

- Mode 1: The inner duty ratio dj satisfies the constraint 0 ≤ dj ≤ 1/3. The durations of the P and N states in vmjOj are the same, and they are controlled as djThs; the voltage levels and steps of vLAj are illustrated in Figure 4a.

- (2)

- Mode 2: The inner duty ratio dj satisfies the constraint 1/3 < dj ≤ 2/3. The durations of the P and N states in vmjOj are the same, and they are controlled as (2/3 − dj)Ths; the voltage levels and steps of vLAj are illustrated in Figure 4b.

- (3)

- Mode 3: The inner duty ratio dj satisfies the constraint 2/3 < dj ≤ 1. The durations of the P and N states in vmjOj are the same, and they are controlled as (dj − 2/3)Ths; the voltage levels and steps of vLAj are illustrated in Figure 4c.

3. Neutral-Point Voltage Balancing Principle

3.1. Neutral-Point Voltage Self-Balancing of the 3LHB-DAB1

3.2. Neutral-Point Balancing Principle of the 3L-DAB3

- (1)

- Mode 1: When one bridge outputs the P or N state, iLi charges the neutral point O1 in the six yellow operating intervals, as shown in the shaded areas in Figure 6a. In these six intervals, iNP1 = −iLi. In the other six intervals, three 3L ANPC bridges output the O states and iNP1 = iLA + iLB + iLC = 0, which does not charge the neutral point O1. As an example, the current paths in Interval 1 of phase A are shown in Figure 7a.

- (2)

- Mode 2: The iNP1 in 12 operating intervals charges the neutral point O1, as shown in the shaded areas in Figure 6b. Generally, there are two different cases: in Intervals 2, 4, 6, 8, 10, and 12, iNP1 = −iLi; in Intervals 1, 3, 5, 7, 9, and 11, iNP1 = iLi. As an example, the current paths in Interval 8 of phase A are shown in Figure 7b.

- (3)

- Mode 3: When one bridge outputs the O state, iNP1 charges the neutral point O1 in the six yellow operating intervals, as shown in the shaded areas in Figure 6c. In these six intervals, iNP1 = iLi. In the other six intervals, three 3L ANPC bridges output the P or N states, iNP1 = 0, which does not charge the neutral point O1. As an example, the current paths in Interval 3 of phase A are shown are Figure 7c.

4. Neutral-Point Voltage Balancing Method

4.1. Control Principle of the Neutral-Point Voltage Balancing Method

4.2. Realization of the Proposed Balancing Method

5. Simulation Results and Experimental Verification

5.1. Simulation Results

5.2. Experimental Verification

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Nomenclature

| DAB | Dual active bridge |

| DAB1 | Single-phase dual-active-bridge |

| DAB3 | Three-phase dual-active-bridge |

| 3L | Three-level |

| 3LHB-DAB1 | 3L half-bridge DAB1 |

| 3LFB-DAB1 | 3L full-bridge DAB1 |

| 3L-DAB3 | Three-phase three-level DAB |

| ANPC | Active neutral-point-clamped |

| Bi1 (i = A, B, C) | Active bridge of the primary side |

| Bi2 | Active bridge of the secondary side |

| Sij1–Sij6 (j = 1, 2) | Six switches of a bridge |

| Aj, Bj, Cj | Output terminals of the bridges |

| VP | DC voltage of the input side |

| VS | DC voltage of the output side |

| CP1, CP2, CS1, CS2 | Filter capacitors in the DC sides |

| Ts | Switching period |

| Ths | Half of switching period |

| fs | Switching frequency |

| ω | Angular frequency |

| PA | Active transmission power of phase A |

| QA | Reactive transmission power of phase A |

| P | Active transmission power of 3L-DAB3 |

| Q | Reactive transmission power of 3L-DAB3 |

| iNPj | Neutral-point instantaneous current |

| INPj | Average value of iNPj |

| dm (m= P, N) | Duration ratio of output state P and N |

| ∆dj | Duty ratio adjustment of dj |

| ∆QNPj | Introduced charge with ∆dj |

| tc | Efficient charging time with ∆dj |

| vCP1, vCP2 | Capacitor Voltages of CP1, CP2 |

| vCS1, vCS2 | Capacitor Voltages of CS1, CS2 |

| Li | Equivalent inductor |

| iLi | Phase current |

| vLij | Terminal voltages of Li |

| nk | Turns-ratio of transformer T |

| k | Voltage conversion ratio |

| vLi | Voltage drop of Li |

| O1, O2 | Neutral-points of two bridges |

| m1, m2 | Neutral-points of Y-Y winding |

| d1 | Inner duty ratio of Bi1 |

| d2 | Inner duty ratio of Bi2 |

| d | Outer duty ratio |

| vi1O1, vi2O2 | AC-side voltages |

| vmjOj | Voltages of m1, m2 refer to O1, O2 |

| iLA,1 | Fundamental component of iLA |

| vA1O1,1 | Fundamental component of vA1O1 |

| ip,LA,1 | In phase component of iLA,1 |

| iq,LA,1 | In quadrature of iLA,1 |

| ∆Qz (z = 1, 2, 3) | Introduced charge of three modes |

| ∆Qzn | Different parts of ∆Qz |

| Vref | Reference voltage of capacitor |

| hd | Dead zone parameter |

| H | Sign-hysteresis parameter |

| evc | Voltage error |

| Sdz | Enabling signal |

| Pbase | Maximum transmission power |

| p | Normalized power |

| Gij1–Gij6 | Drive waveforms of Sij1–Sij6 |

References

- Hou, N.; Li, Y.W. Overview and Comparison of Modulation and Control Strategies for a Nonresonant Single-Phase Dual-Active-Bridge DC–DC Converter. IEEE Trans. Power Electron. 2020, 35, 3148–3172. [Google Scholar] [CrossRef]

- Zhao, B.; Song, Q.; Liu, W.; Sun, Y. Overview of Dual-Active-Bridge Isolated Bidirectional DC–DC Converter for High-Frequency-Link Power-Conversion System. IEEE Trans. Power Electron. 2014, 29, 4091–4106. [Google Scholar] [CrossRef]

- Zhao, B.; Song, Q.; Liu, W. Experimental Comparison of Isolated Bidirectional DC–DC Converters Based on All-Si and All-SiC Power Devices for Next-Generation Power Conversion Application. IEEE Trans. Ind. Electron. 2014, 61, 1389–1393. [Google Scholar] [CrossRef]

- Zhao, B.; Song, Q.; Li, J.; Liu, W. A Modular Multilevel DC-Link Front-to-Front DC Solid-State Transformer Based on High-Frequency Dual Active Phase Shift for HVDC Grid Integration. IEEE Trans. Ind. Electron. 2017, 64, 8919–8927. [Google Scholar] [CrossRef]

- Steigerwald, R.L.; De Doncker, R.W.; Kheraluwala, H. A Comparison of High-Power DC-DC Soft-Switched Converter Topologies. IEEE Trans. Ind. Appl. 1996, 32, 1139–1145. [Google Scholar] [CrossRef]

- Engel, S.P.; Stieneker, M.; Soltau, N.; Rabiee, S.; Stagge, H.; De Doncker, R.W. Comparison of the Modular Multilevel DC Converter and the Dual-Active Bridge Converter for Power Conversion in HVDC and MVDC Grids. IEEE Trans. Power Electron. 2015, 30, 124–137. [Google Scholar] [CrossRef]

- Krismer, F.; Kolar, J.W. Efficiency-Optimized High-Current Dual Active Bridge Converter for Automotive Applications. IEEE Trans. Ind. Electron. 2012, 59, 2745–2760. [Google Scholar] [CrossRef]

- He, P.; Khaligh, A. Comprehensive Analyses and Comparison of 1 KW Isolated DC–DC Converters for Bidirectional EV Charging Systems. IEEE Trans. Transp. Electrif. 2017, 3, 147–156. [Google Scholar] [CrossRef]

- De Doncker, R.W.A.A.; Divan, D.M.; Kheraluwala, M.H. A Three-Phase Soft-Switched High-Power-Density DC/DC Converter for High-Power Applications. IEEE Trans. Ind. Appl. 1991, 27, 63–73. [Google Scholar] [CrossRef]

- Segaran, D.; Holmes, D.G.; McGrath, B.P. Comparative Analysis of Single-and Three-Phase Dual Active Bridge Bidirectional DC-DC Converters. Aust. J. Electr. Electron. Eng. 2009, 6, 329–337. [Google Scholar] [CrossRef]

- van Hoek, H.; Neubert, M.; Kroeber, A.; De Doncker, R.W. Comparison of a Single-Phase and a Three-Phase Dual Active Bridge with Low-Voltage, High-Current Output. In Proceedings of the 2012 International Conference on Renewable Energy Research and Applications (ICRERA), Nagasaki, Japan, 11–14 November 2012; pp. 1–6. [Google Scholar]

- Shu, L.; Chen, W.; Li, R.; Zhang, K.; Deng, F.; Yuan, Y.; Wang, T. A Three-Phase Triple-Voltage Dual-Active-Bridge Converter for Medium Voltage DC Transformer to Reduce the Number of Submodules. IEEE Trans. Power Electron. 2020, 35, 11574–11588. [Google Scholar] [CrossRef]

- Garcia-Bediaga, A.; Villar, I.; Rujas, A.; Etxeberria-Otadui, I.; Rufer, A. Analytical Models of Multiphase Isolated Medium-Frequency DC–DC Converters. IEEE Trans. Power Electron. 2017, 32, 2508–2520. [Google Scholar] [CrossRef]

- Anurag, A.; Acharya, S.; Bhattacharya, S.; Weatherford, T.R.; Parker, A.A. A Gen-3 10-KV SiC MOSFET-Based Medium-Voltage Three-Phase Dual Active Bridge Converter Enabling a Mobile Utility Support Equipment Solid State Transformer. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 1519–1536. [Google Scholar] [CrossRef]

- Agarwal, A.; Rastogi, S.K.; Bhattacharya, S. Performance Evaluation of Two-Level to Three-Level Three-Phase Dual Active Bridge (2L-3L DAB3). In Proceedings of the 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 20–24 March 2022; pp. 361–368. [Google Scholar]

- Cunico, L.M.; Kirsten, A.L. Improved ZVS Range for Three-Phase Dual-Active-Bridge Converter With Wye-Extended-Delta Transformer. IEEE Trans. Ind. Electron. 2022, 69, 7984–7993. [Google Scholar] [CrossRef]

- Hu, J.; Yang, Z.; Cui, S.; De Doncker, R.W. Closed-Form Asymmetrical Duty-Cycle Control to Extend the Soft-Switching Range of Three-Phase Dual-Active-Bridge Converters. IEEE Trans. Power Electron. 2021, 36, 9609–9622. [Google Scholar] [CrossRef]

- Hu, J.; Soltau, N.; De Doncker, R.W. Asymmetrical Duty-Cycle Control of Three-Phase Dual-Active Bridge Converter for Soft-Switching Range Extension. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–8. [Google Scholar]

- van Hoek, H.; Neubert, M.; De Doncker, R.W. Enhanced Modulation Strategy for a Three-Phase Dual Active Bridge—Boosting Efficiency of an Electric Vehicle Converter. IEEE Trans. Power Electron. 2013, 28, 5499–5507. [Google Scholar] [CrossRef]

- Sun, J.; Qiu, L.; Liu, X.; Zhang, J.; Ma, J.; Fang, Y. Optimal Simultaneous PWM Control for Three- Phase Dual-Active-Bridge Converters to Minimize Current Stress in the Whole Load Range. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 5822–5837. [Google Scholar] [CrossRef]

- Baars, N.H.; Wijnands, C.G.E.; Everts, J. A Three-Level Three-Phase Dual Active Bridge DC-DC Converter with a Star-Delta Connected Transformer. In Proceedings of the 2016 IEEE Vehicle Power and Propulsion Conference (VPPC), Hangzhou, China, 17–20 October 2016; pp. 1–6. [Google Scholar]

- Baars, N.H.; Wijnands, C.G.E.; Everts, J. ZVS Modulation Strategy for a Three-Phase Dual Active Bridge DC-DC Converter with Three-Level Phase-Legs. In Proceedings of the 2016 18th European Conference on Power Electronics and Applications (EPE’16 ECCE Europe), Karlsruhe, Germany, 5–9 September 2016; pp. 1–10. [Google Scholar]

- Baars, N.H.; Everts, J.; Wijnands, C.G.E.; Lomonova, E.A. Modulation Strategy for Wide-Range ZVS Operation of a Three-Level Three-Phase Dual Active Bridge Dc-Dc Converter. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 3357–3364. [Google Scholar]

- Baars, N.H.; Everts, J.; Wijnands, C.G.E.; Lomonova, E.A. Evaluation of a High-Power Three-Phase Dual Active Bridge DC-DC Converter with Three-Level Phase-Legs. In Proceedings of the 2016 18th European Conference on Power Electronics and Applications (EPE’16 ECCE Europe), Karlsruhe, Germany, 5–9 September 2016; pp. 1–10. [Google Scholar]

- Filba-Martinez, A.; Busquets-Monge, S.; Nicolas-Apruzzese, J.; Bordonau, J. Operating Principle and Performance Optimization of a Three-Level NPC Dual-Active-Bridge DC–DC Converter. IEEE Trans. Ind. Electron. 2016, 63, 678–690. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Pérez, M.A.; Leon, J.I. Recent Advances and Industrial Applications of Multilevel Converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Liu, P.; Duan, S. Analysis of the Neutral-Point Voltage Self-Balance Mechanism in the Three-Level Full-Bridge DC−DC Converter by Introduction of Flying Capacitors. IEEE Trans. Power Electron. 2019, 34, 11736–11747. [Google Scholar] [CrossRef]

- Kim, K.; Kim, J.; Nguyen, V.C.; Cha, H. A novel voltage balancing strategy using LC for dual output dual-active-bridge converter. In Proceedings of the 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019—ECCE Asia), Busan, Korea, 27–30 May 2019. [Google Scholar]

- Lee, J.; Choi, H.; Jung, J. Three Level NPC Dual Active Bridge Capacitor Voltage Balancing Switching Modulation. In Proceedings of the 2017 IEEE International Telecommunications Energy Conference (INTELEC), Broadbeach, QLD, Australia, 22–26 October 2017; pp. 438–443. [Google Scholar]

- Filba-Martinez, A.; Busquets-Monge, S.; Bordonau, J. Modulation and Capacitor Voltage Balancing Control of Multilevel NPC Dual Active Bridge DC–DC Converters. IEEE Trans. Ind. Electron. 2020, 67, 2499–2510. [Google Scholar] [CrossRef]

- Campos-Salazar, J.M.; Busquets-Monge, S.; Filba-Martinez, A.; Alepuz, S. Comparison of Modulations and Dc-Link Balance Control Strategies for a Multibattery Charger System Based on a Three-Level Dual-Active-Bridge Power Converter. In Proceedings of the 2022 IEEE 31st International Symposium on Industrial Electronics (ISIE), Anchorage, AK, USA, 1–3 June 2022; pp. 366–373. [Google Scholar]

- Joebges, P.; Gorodnichev, A.; De Doncker, R.W. Modulation and Active Midpoint Control of a Three-Level Three-Phase Dual-Active Bridge DC-DC Converter under Non-Symmetrical Load. In Proceedings of the 2018 International Power Electronics Conference (IPEC-Niigata 2018—ECCE Asia), Niigata, Japan, 20–24 May 2018; pp. 375–382. [Google Scholar]

- Baars, N.; Everts, J.; Wijnands, C.; Lomonova, E. Performance Evaluation of a Three-Phase Dual Active Bridge DC-DC Converter with Different Transformer Winding Configurations. IEEE Trans. Power Electron. 2015, 31, 6814–6823. [Google Scholar] [CrossRef]

- Guan, Q.-X.; Zhang, Y.; Zhao, H.-B.; Kang, Y. Optimized Switching Strategy for ANPC–DAB Converter Through Multiple Zero States. IEEE Trans. Power Electron. 2022, 37, 2885–2898. [Google Scholar] [CrossRef]

- Chen, H.; Ouyang, S.; Liu, J.; Li, X. An Asymmetrical Phase-Shift Scheme of Three-Phase Dual Active Bridge with Minimum Current Root-Mean-Square Value Control. IEEE Trans. Power Electron. 2022, 37, 1–20. [Google Scholar] [CrossRef]

- Liu, P.; Chen, C.; Duan, S. An Optimized Modulation Strategy for the Three-Level DAB Converter With Five Control Degrees of Freedom. IEEE Trans. Ind. Electron. 2020, 67, 254–264. [Google Scholar] [CrossRef]

- Wang, C.; Li, Y. Analysis and Calculation of Zero-Sequence Voltage Considering Neutral-Point Potential Balancing in Three-Level NPC Converters. IEEE Trans. Ind. Electron. 2010, 57, 2262–2271. [Google Scholar] [CrossRef]

- Filba-Martinez, A.; Busquets-Monge, S.; Bordonau, J. Modulation and Capacitor Voltage Balancing Control of a Three-Level NPC Dual-Active-Bridge DC-DC Converter. In Proceedings of the 39th Annual Conference of the IEEE Industrial Electronics Society (IECON 2013), Vienna, Austria, 10–13 November 2013; pp. 6251–6256. [Google Scholar]

- Hu, Y.; Zhang, T.H.; Yang, L.X.; Guan, Q.X.; Zhang, Y. Comparative Study of Reactive Power Optimization and Current Stress Optimization of DAB Converter with Dual Phase Shift Control. Proc. CSEE 2020, 40, 243–253. (In Chinese) [Google Scholar] [CrossRef]

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| Input voltage VP | 400 V | Turns ratio of T nk | 1 |

| Output voltage VS | 300 V | Switching frequency fs | 20 kHz |

| Rated power | 3.6 kW | Dead zone hd | 1 |

| Input/output capacitors | 150 μF | Sign-hysteresis parameter H | 10 |

| Series inductor Li | 125 μH | Duty ratio |∆dj| | 0.03 |

| Power devices | ON semiconductor—FGH50T65SQD (650 V/50 A) | ||

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, X.; Zhang, Y.; Yang, J. Neutral-Point Voltage Balancing Method for Three-Phase Three-Level Dual-Active-Bridge Converters. Energies 2022, 15, 6463. https://0-doi-org.brum.beds.ac.uk/10.3390/en15176463

Wu X, Zhang Y, Yang J. Neutral-Point Voltage Balancing Method for Three-Phase Three-Level Dual-Active-Bridge Converters. Energies. 2022; 15(17):6463. https://0-doi-org.brum.beds.ac.uk/10.3390/en15176463

Chicago/Turabian StyleWu, Xinmi, Yu Zhang, and Jiawen Yang. 2022. "Neutral-Point Voltage Balancing Method for Three-Phase Three-Level Dual-Active-Bridge Converters" Energies 15, no. 17: 6463. https://0-doi-org.brum.beds.ac.uk/10.3390/en15176463