Experimental and Modeling Study on the High-Performance p++-GaAs/n++-GaAs Tunnel Junctions with Silicon and Tellurium Co-Doped InGaAs Quantum Well Inserted

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

3.1. Devices Performance of the Tunnel Junctions

3.1.1. Influence of Growth Temperature

3.1.2. Influence of Thickness

3.1.3. Influence of V/III Ratio

3.2. Role of Trap-Assisted Tunneling

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Kabir, E.; Kumar, P.; Kumar, S.; Adelodun, A.A.; Kim, K.H. Solar energy: Potential and future prospects. Renew. Sustain. Energy Rev. 2018, 82, 894. [Google Scholar] [CrossRef]

- Geisz, J.F.; France, R.M.; Schulte, K.L.; Steiner, M.A.; Norman, A.G.; Guthrey, H.L.; Young, M.R.; Song, T.; Moriarty, T. Six-junction III–V solar cells with 47.1% conversion efficiency under 143 Suns concentration. Nat. Energy 2020, 5, 326. [Google Scholar] [CrossRef]

- Louarn, K.; Claveau, Y.; Fontaine, C.; Arnoult, A.; Marigo-Lombart, L.; Massiot, I.; Piquemal, F.; Bounouh, A.; Cavassilas, N.; Almuneau, G. Thickness Limitation of Band-to-Band Tunneling Process in GaAsSb/InGaAs Type-II Tunnel Junctions Designed for Multi-Junction Solar Cells. ACS Appl. Energy Mater. 2019, 2, 1149. [Google Scholar] [CrossRef] [Green Version]

- Wheeldon, J.F.; Valdivia, C.E.; Walker, A.W.; Kolhatkar, G.; Jaouad, A.; Turala, A.; Riel, B.; Masson, D.; Puetz, N.; Fafard, S.; et al. Performance comparison of AlGaAs, GaAs and InGaP tunnel junctions for concentrated multijunction solar cells. Prog. Photovolt. 2011, 19, 442. [Google Scholar] [CrossRef]

- Northrup, J.E.; Zhang, S.B. Dopant and defect energetics: Si in GaAs. Phys. Rev. B 1993, 47, 6791. [Google Scholar] [CrossRef] [PubMed]

- Hermle, M.; Létay, G.; Philipps, S.P.; Bett, A.W. Numerical simulation of tunnel diodes for multi-junction solar cells. Prog. Photovolt. 2008, 16, 409. [Google Scholar] [CrossRef]

- Bedair, S.; Carlin, C.Z.; Harmon, J.L.; Sayed, I.E.H.; Colter, P. High Performance Tunnel Junction with Resistance to Thermal Annealing. In Proceedings of the 12th International Conference on Concentrator Photovoltaic Systems (CPV-12), Freiburg, Germany, 25–27 April 2016; p. 020003. [Google Scholar]

- Lumb, M.P.; Yakes, M.K.; Gonzalez, M.; Vurgaftman, I.; Bailey, C.G.; Hoheisel, R.; Walters, R.J. Double quantum-well tunnel junctions with high peak tunnel currents and low absorption for InP multi-junction solar cells. Appl. Phys. Lett. 2012, 100, 213907. [Google Scholar] [CrossRef]

- Bedair, S.; Harmon, L.J.; Carlin, C.Z.; Hashem, I.E.; Colter, P.C. High performance as-grown and annealed high band gap tunnel junctions: Te behavior at the interface. Appl. Phys. Lett. 2016, 108, 203903. [Google Scholar] [CrossRef] [Green Version]

- Louarn, K.; Claveau, Y.; Marigo-Lombart, L.; Fontaine, C.; Arnoult, A.; Piquemal, F.; Bounouh, A.; Cavassilas, N.; Almuneau, G. Effect of low and staggered gap quantum wells inserted in GaAs tunnel junctions. J. Phys. D Appl. Phys. 2018, 51, 145107. [Google Scholar] [CrossRef]

- Law, J.J.M.; Carter, A.D.; Lee, S.; Huang, C.Y.; Lu, H.; Rodwell, M.J.W.; Gossard, A.C. Co-doping of InxGa1-xAs with silicon and tellurium for improved ultra-low contact resistance. J. Cryst. Growth 2013, 378, 92. [Google Scholar] [CrossRef]

- Nguyen, X.S.; Yadav, S.; Lee, K.H.; Kohen, D.; Kumar, A.; Made, R.I.; Lee, K.E.K.; Chua, S.J.; Gong, X.; Fitzgerald, E.A. MOCVD growth of high quality InGaAs HEMT layers on large scale Si wafers for heterogeneous integration with Si CMOS. IEEE Trans. Semicond. Manuf. 2017, 30, 456. [Google Scholar] [CrossRef]

- Hamon, G.; Paillet, N.; Alvarez, J.; Larrue, A.; Decobert, J. Te doping of GaAs and GaInP using diisopropyl telluride (DIPTe) for tunnel junction applications. J. Cryst. Growth 2018, 498, 301. [Google Scholar] [CrossRef]

- Louarn, K. Development of Tunnel Junctions Based on III-V Semiconductors Heterostructures for High Efficiency Multi-Junction Solar Cells. Ph.D. Thesis, Paul Sabatier University, Toulouse, France, 2018. [Google Scholar]

- Jandieri, K.; Baranovskii, S.D.; Rubel, O.; Stolz, W.; Gebhard, F.; Guter, W.; Hermle, M.; Bett, A.W. Resonant electron tunneling through defects in GaAs tunnel diodes. J. Appl. Phys. 2008, 104, 094506. [Google Scholar] [CrossRef]

- Park, Y.; Qian, W.; Skowronski, M. Precipitation of Tellurium-Rich Phase in Heavily Diethyltellurium-Doped GaAs during Organometallic Vapor Phase Epitaxy. J. Electrochem. Soc. 1995, 142, 4294. [Google Scholar] [CrossRef]

- García, I.; Rey-Stolle, I.; Algora, C. Performance analysis of AlGaAs/GaAs tunnel junctions for ultra-high concentration photovoltaics. J. Phys. D Appl. Phys. 2012, 45, 045101. [Google Scholar]

- Crosslight Software Inc., Canada. Available online: http://www.crosslight.com/ (accessed on 20 October 2019).

- Li, Z.Q.; Xiao, Y.G.; Li, Z.M.S. Modeling of multi-junction solar cells by Crosslight APSYS. In High and Low Concentration for Solar Electric Applications; International Society for Optics and Photonics: San Diego, CA, USA, 2006; p. 633909. [Google Scholar]

- Colter, P.; Hagar, B.; Bedair, S. Tunnel junctions for III-V multijunction solar cells review. Crystals 2018, 8, 445. [Google Scholar] [CrossRef] [Green Version]

- Slotboom, J.W.; Degraaff, H.C. Measurements of bandgap narrowing in Si bipolar transistors. Solid-State Electron. 1976, 19, 857. [Google Scholar] [CrossRef]

- Gehring, A. Simulation of Tunneling in Semiconductor Devices. Ph.D. Thesis, Technical University, Vienna, Austria, 2003. [Google Scholar]

- Wheeldon, J.F.; Valdivia, C.E.; Walker, A.; Kolhatkar, G.; Hall, T.J.; Hinzer, K.; Masson, D.; Fafard, S.; Jaouad, A.; Turala, A. AlGaAs tunnel junction for high efficiency multi-junction solar cells: Simulation and measurement of temperature-dependent operation. In Proceedings of the 34th IEEE Photovoltaic Specialists Conference (PVSC), Philadelphia, PA, USA, 7–12 June 2009; pp. 106–111. [Google Scholar]

- Narasimhan, V.K.; Yastrebova, N.; Valdivia, C.E.; Hall, T.J.; Hinzer, K.; Masson, D.; Fafard, S.; Jaouad, A.; Arès, R.; Aimez, V. Effect of parameter variations on the current-voltage behavior of AlGaAs tunnel junction models. In Proceedings of the 1st Microsystems and Nanoelectronics Research Conference, Ottawa, ON, Canada, 15 October 2008; p. 165. [Google Scholar]

| Sample No. | Thickness (nm) | V/III | Temperature (°C) |

|---|---|---|---|

| a-1 | 16 | 74 | 600 |

| a-2 | 16 | 74 | 580 |

| a-3 | 16 | 74 | 550 |

| b-1 | 11 | 74 | 550 |

| c-1 | 16 | 15 | 550 |

| c-2 | 16 | 5 | 550 |

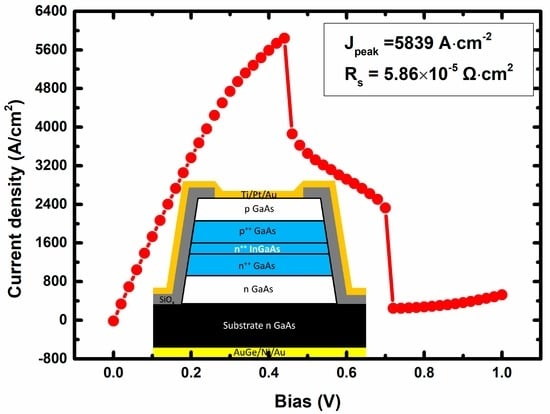

| Sample No. | Doping Level (cm−3) | Peak Current Density (A cm−2) | Resistance (Ω cm2) |

|---|---|---|---|

| a-1 | 1.13 × 1019 | 16 | 1.25 × 10−2 |

| a-2 | 2.00 × 1019 | 472 | 3.17 × 10−4 |

| a-3 | 4.03 × 1019 | 2130 | 1.17 × 10−4 |

| b-1 | 3.55 × 1019 | 1222 | 1.94 × 10−4 |

| c-1 | 4.22 × 1019 | 3320 | 9.00 × 10−5 |

| c-2 | 5.09 × 1019 | 5839 | 5.86 × 10−5 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gou, Y.; Wang, J.; Cheng, Y.; Guo, Y.; Xiao, X.; Liu, H.; Tan, S.; Zhou, L.; Yang, H.; Deng, G.; et al. Experimental and Modeling Study on the High-Performance p++-GaAs/n++-GaAs Tunnel Junctions with Silicon and Tellurium Co-Doped InGaAs Quantum Well Inserted. Crystals 2020, 10, 1092. https://0-doi-org.brum.beds.ac.uk/10.3390/cryst10121092

Gou Y, Wang J, Cheng Y, Guo Y, Xiao X, Liu H, Tan S, Zhou L, Yang H, Deng G, et al. Experimental and Modeling Study on the High-Performance p++-GaAs/n++-GaAs Tunnel Junctions with Silicon and Tellurium Co-Doped InGaAs Quantum Well Inserted. Crystals. 2020; 10(12):1092. https://0-doi-org.brum.beds.ac.uk/10.3390/cryst10121092

Chicago/Turabian StyleGou, Yudan, Jun Wang, Yang Cheng, Yintao Guo, Xiao Xiao, Heng Liu, Shaoyang Tan, Li Zhou, Huomu Yang, Guoliang Deng, and et al. 2020. "Experimental and Modeling Study on the High-Performance p++-GaAs/n++-GaAs Tunnel Junctions with Silicon and Tellurium Co-Doped InGaAs Quantum Well Inserted" Crystals 10, no. 12: 1092. https://0-doi-org.brum.beds.ac.uk/10.3390/cryst10121092