Secure Boot for Reconfigurable Architectures

Abstract

:1. Introduction

2. Background Studies

2.1. Secure Boot in FPGAs

2.2. Trusted Platform Modules

3. Threat Model for Secure Boot of FPGA Bitstreams

3.1. Bitstream Spoofing

3.2. Runtime Malicious Modification

3.3. Nonsecure Communication with Content Provider

4. The Root of Trust Architecture

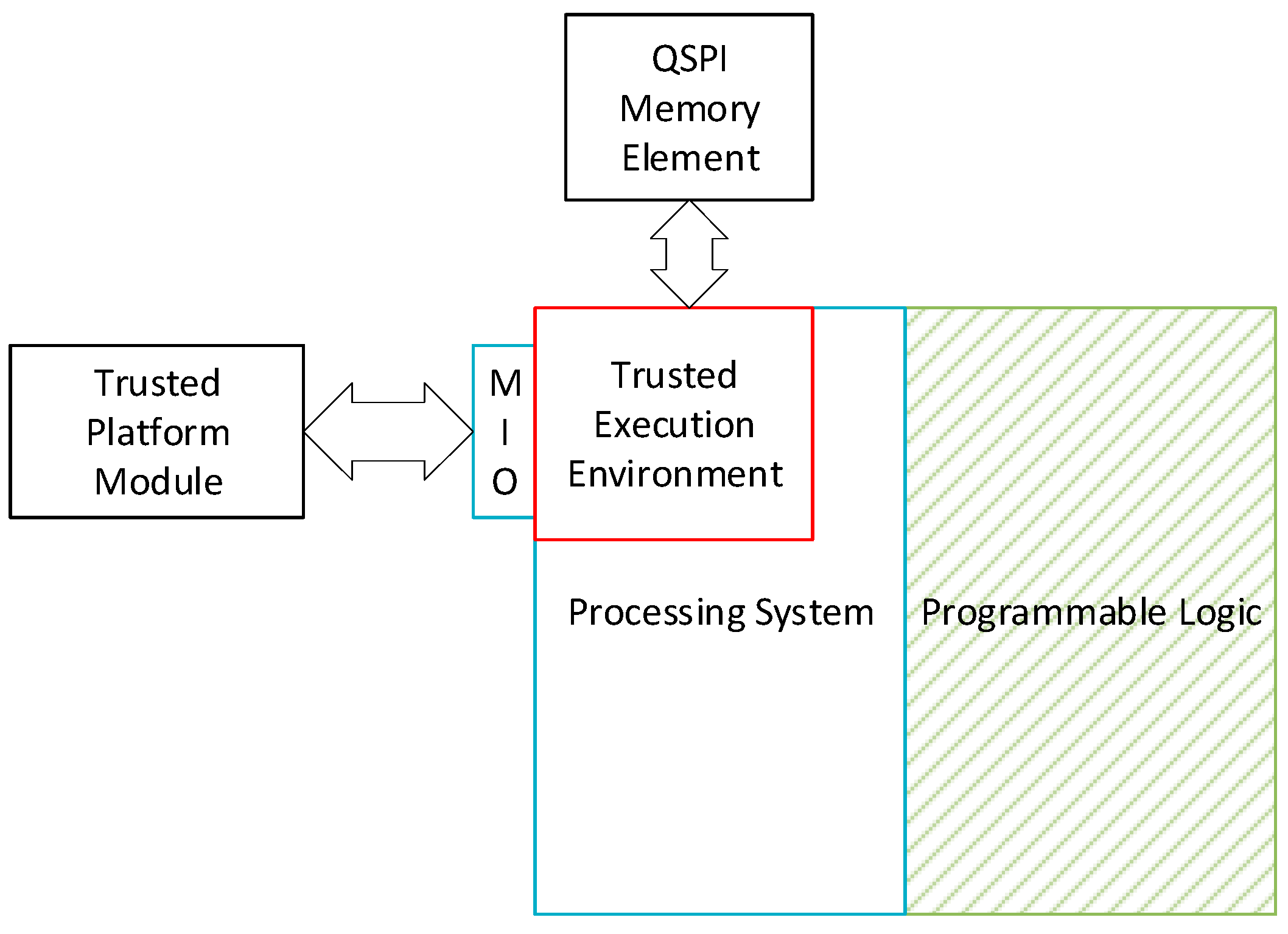

4.1. Hardware Overview

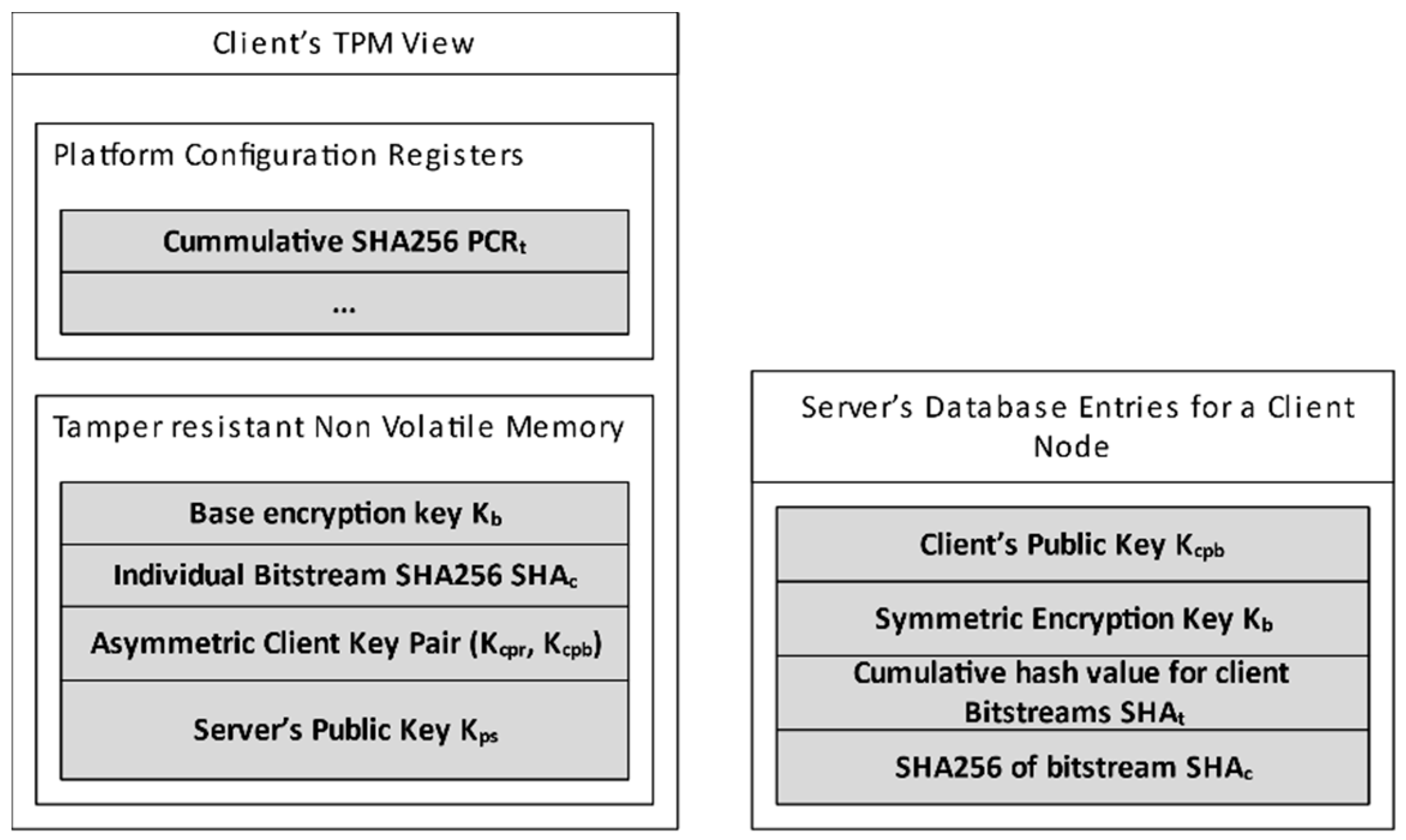

4.2. Establishing Source of Trust

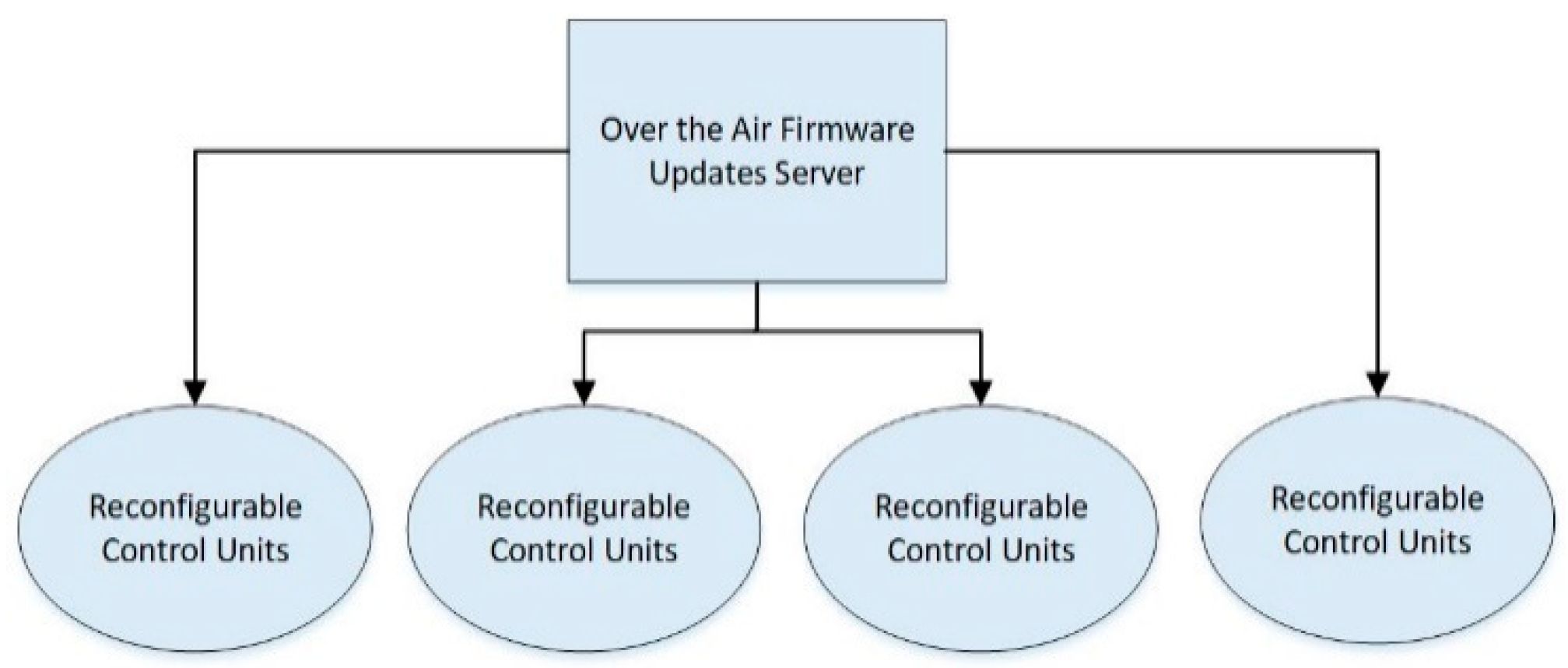

4.3. Secure Over the Air (OTA) Update Mechanism

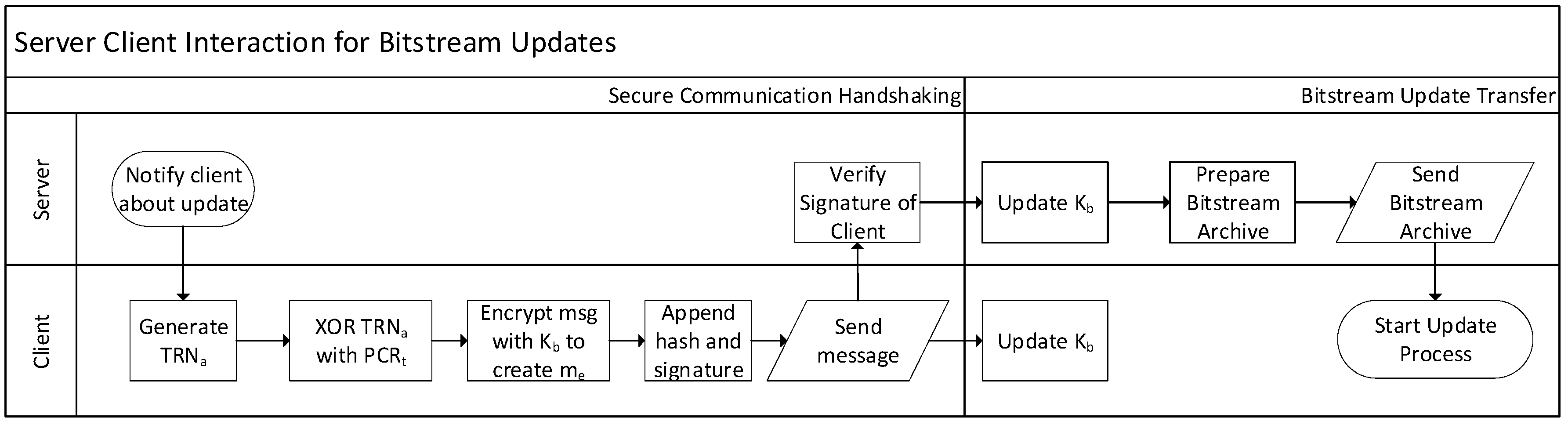

4.3.1. Secure Communication Handshaking

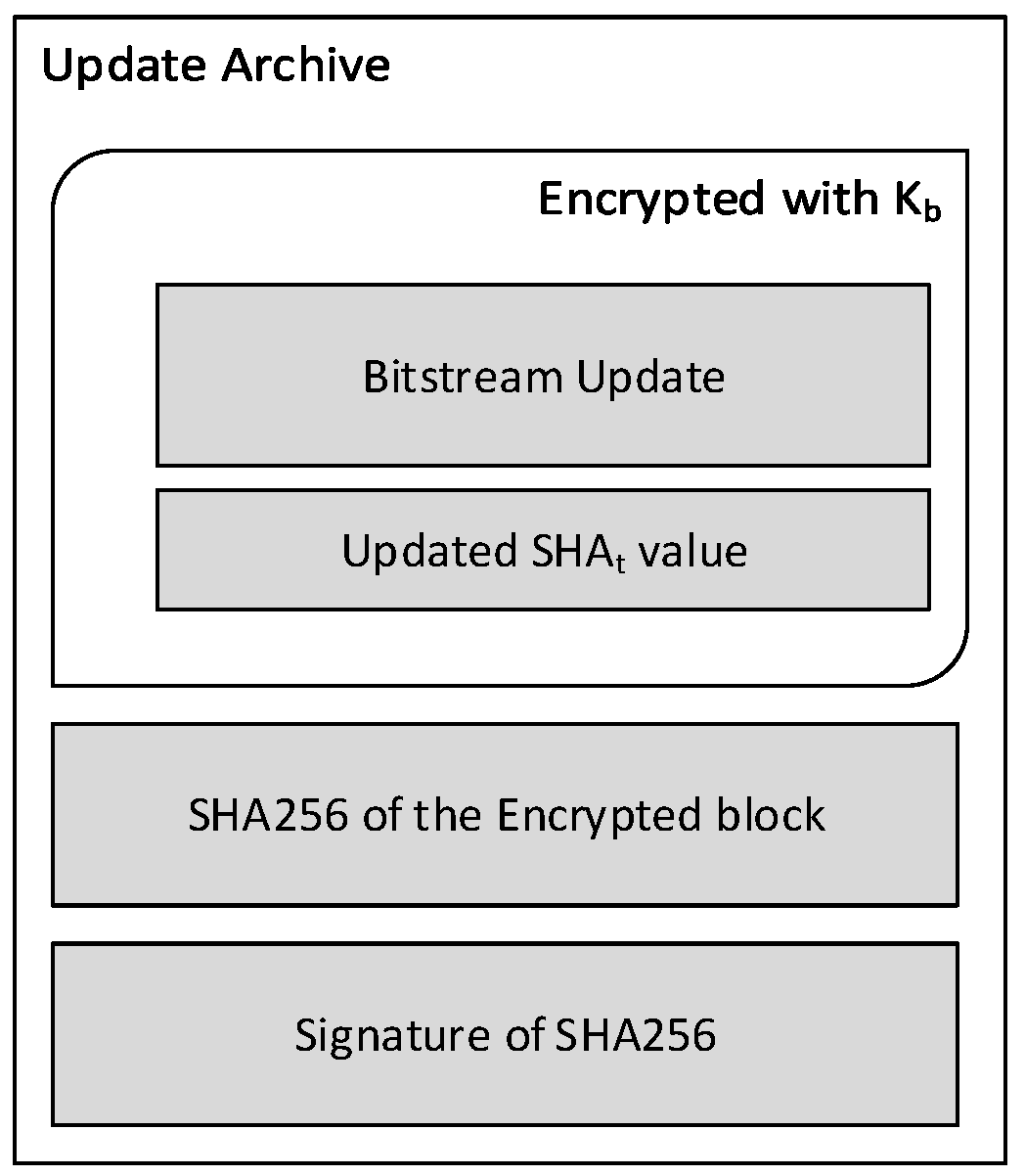

4.3.2. Secure Update Packaging and Transfer

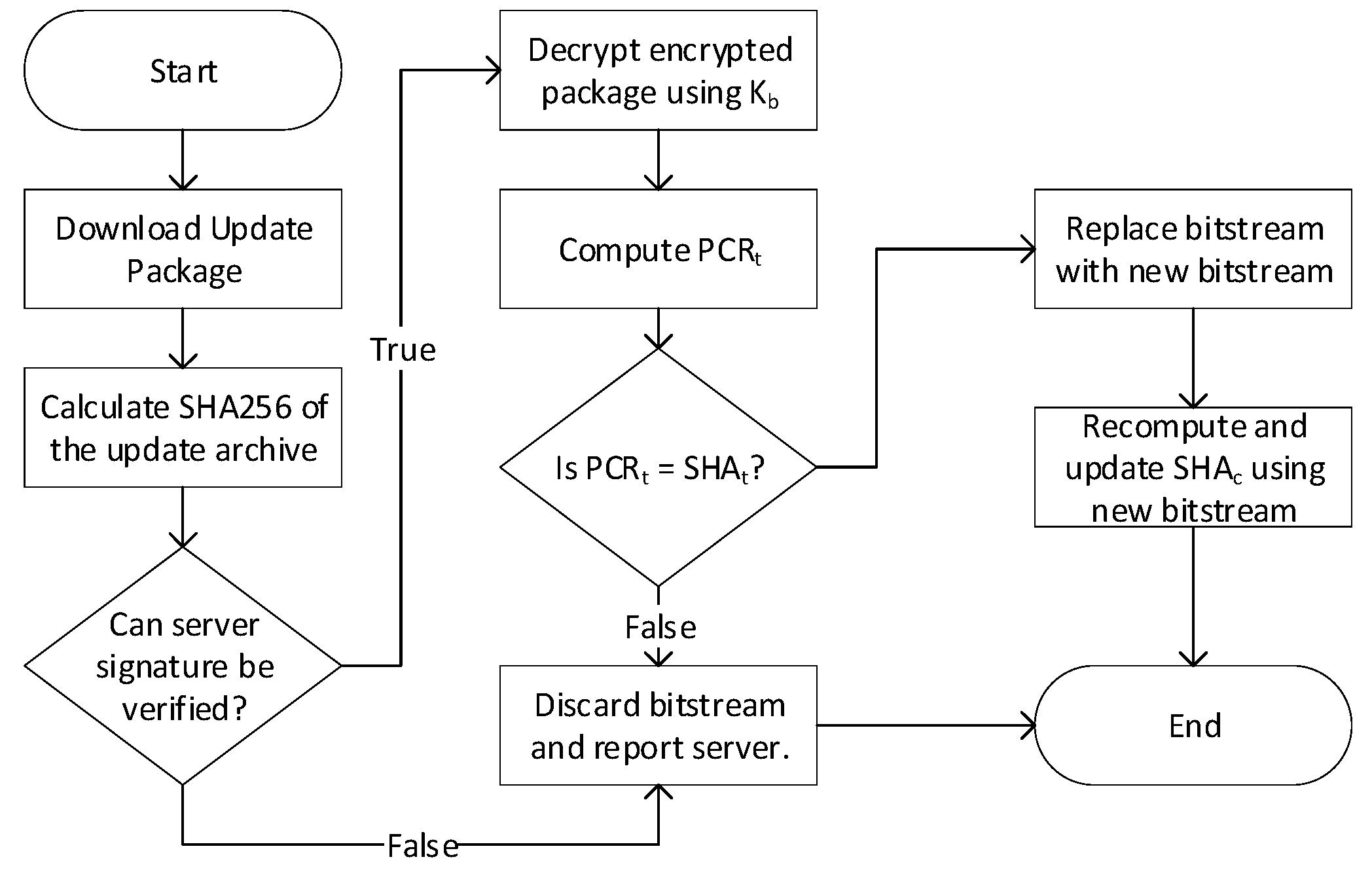

4.3.3. Applying the Update

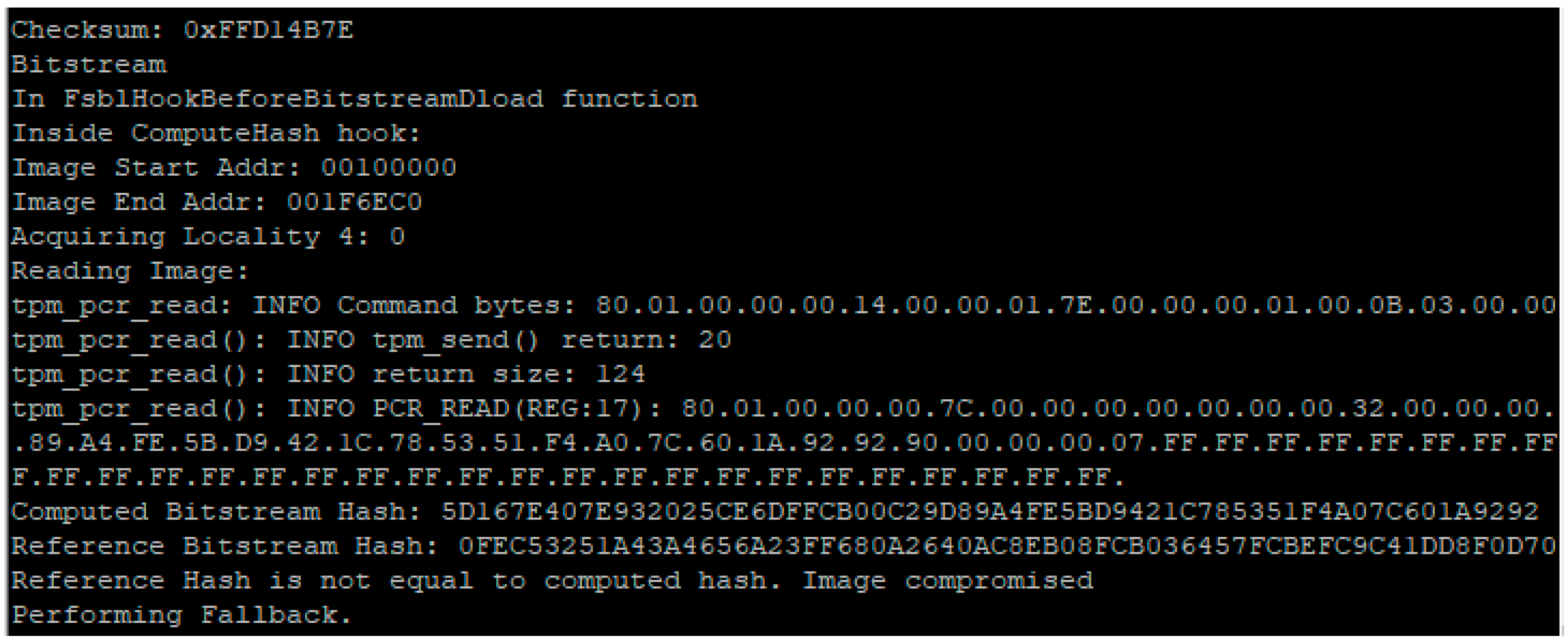

4.3.4. Secure FSBL Boot Process

5. Results and Analysis

| Algorithm 1: tpm_pcr_extend function |

| Inputs: Locality (L), PCR Index I, Data Input D |

| Output: PCR Based Hash (H) |

| Buffer = [] If (!Current active locality is L) then Request locality L from TPM If (!Current active locality is L) then Raise Exception //Make TPM2_PCR_EXTEND Request Buffer += TPM2_PCR2_EXTEND Header with Locality (L), PCR Index(I) Buffer += DATA_LENGTH (32) Buffer += D Send Buffer to TPM H = TPM2_PCR_READ(PCR=I) Return H |

| Algorithm 2: ComputeHashLoc4 Function |

| Inputs: Data Block (D), |

| Output: Hash H |

| If (!Current active locality is 4) then Request locality 4 from TPM If (!Current active locality is 4) then Raise Exception Send TPM_HASH_START Request to TPM For (I: each block of length 64 in D) If length(I) <64 then I += Padding Send TPM_HASH_DATA + I to TPM Send TPM_HASH_END Request to TPM H = TPM_READ_PCR(PCR=17) Return H |

6. Security Analysis

- Digital certificates are used for the identification of the server and participating nodes. The certificates are shared before deployment by the trusted authority and can only be modified by the trusted facility. Thus, impersonation and data spoofing are not possible in the proposed scheme.

- The encrypted configuration bitstream is packaged with the SHA256 of the encrypted bitstream, along with the bitstream package signature signed off with the private key of the server. Any changes in the bitstream will fail the hash comparison and the device will discard the updates. This prohibits the man in the middle and data spoofing attacks and provides an authentication mechanism for securely transfer the configuration files.

- The keys are stored on the tamper-resistant storage inside TPM on server and device nodes, eliminating invasive and probe attacks to break the key. Furthermore, the private keys never leave the premises, thus mitigates the man in the middle attack.

- The symmetric encryption key is updated on every bitstream. It ensures freshness of encryption keys as well as mitigates replay attacks. Once the key is used, it is never used again and hence any repeated keys can be used to identify attacks.

- During the execution, the device cannot be altered, and the keys can be accessed with the hardware isolation protection of the SPI interface. The TPM interface is only accessed in the secure mode.

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Schmidt, S.; Tausig, M.; Hudler, M.; Simhandl, G. Secure Firmware Update over the Air in the Internet of Things Focusing on Flexibility and Feasibility. 2016. Available online: https://www.researchgate.net/profile/Mathias_Tausig/publication/306252903_Secure_Firmware_Update_Over_the_Air_in_the_Internet_of_Things_Focusing_on_Flexibility_and_Feasibility_Proposal_for_a_Design/links/57b4721408aede8a665a50e2.pdf (accessed on 2 October 2018).

- Chandra, H.; Anggadjaja, E.; Wijaya, P.S.; Gunawan, E. Internet of Things: Over-the-Air (OTA) firmware update in Lightweight mesh network protocol for smart urban development. In Proceedings of the Asia-Pacific Conference on Communications, Yogyakarta, Indonesia, 25–27 August 2016; pp. 115–118. [Google Scholar]

- Andrade, C.E.; Byers, S.D.; Gopalakrishnan, V.; Halepovic, E.; Majmundar, M.; Poole, D.J.; Tran, L.K.; Volinsky, C.T. Managing massive firmware-over-the-air updates for connected cars in cellular networks. In Proceedings of the 2nd ACM International Workshop on Smart, Autonomous, and Connected Vehicular Systems and Services, Co-Located with MobiCom, New York, NY, USA, 16–20 October 2017; pp. 65–72. [Google Scholar]

- Zimmer, V.; Krau, M. Establishing the Root of Trust. 2016. Available online: https://www.uefi.org/sites/default/files/resources/UEFI%20RoT%20white%20paper_Final%208%208%2016%20%28003%29.pdf (accessed on 5 January 2020).

- Wilkins, R.; Richardson, B. Uefi Secure Boot in Modern Computer Security Solutions. 2013. Available online: https://media.kasperskycontenthub.com/wp-content/uploads/sites/63/2014/06/21032725/UEFI_Secure_Boot_in_Modern_Computer_Security_Solutions_2013.pdf (accessed on 4 November 2019).

- Secure the Windows 10 Boot Process|Microsoft Docs. Available online: https://docs.microsoft.com/en-us/windows/security/information-protection/secure-the-windows-10-boot-process (accessed on 4 October 2018).

- Xilinx Inc. Zynq-7000 All Programmable SoC Secure Boot. 2014. Available online: https://www.xilinx.com/support/documentation/user_guides/ug1025-zynq-secure-boot-gsg.pdf (accessed on 11 April 2018).

- Trimberger, S.M.; Moore, J.J. FPGA security: Motivations, features, and applications. Proc. IEEE 2014, 102, 1248–1265. [Google Scholar] [CrossRef]

- Tajik, S.; Lohrke, H.; Seifert, J.P.; Boit, C. On the power of optical contactless Probing: Attacking bitstream encryption of FPGAs. In Proceedings of the ACM Conference on Computer and Communications Security, Dallas, TX, USA, 30 October–3 November 2017; pp. 1661–1674. [Google Scholar]

- Xilinx Inc. TR Manual Zynq-7000 All Programmable SoC; Xilinx: San Jose, CA, USA, 2015; Volume 585, pp. 1–1863. [Google Scholar]

- Xilinx Inc. Zynq UltraScale+ Device Technical Reference Manual UG1085. 2018. Available online: https://www.xilinx.com/content/dam/xilinx/support/documentation/user_guides/ug1085-zynq-ultrascale-trm.pdf (accessed on 20 January 2020).

- Xilinx Inc. Developing Tamper-Resistant Designs with Zynq UltraScale+ Devices. 2018. Available online: https://www.xilinx.com/support/documentation/application_notes/xapp1323-zynq-usp-tamper-resistant-designs.pdf (accessed on 11 April 2018).

- Iveia Atlas-I-Z8 Low-Power Zynq UltraScale+ SoM-iVeia. Available online: http://iveia.com/atlas-i-z8 (accessed on 30 November 2018).

- Jacob, N.; Heyszl, J.; Zankl, A.; Rolfes, C.; Sigl, G. How to break secure boot on FPGA SoCs through malicious hardware. In Cryptographic Hardware and Embedded Systems—CHES 2017; Fischer, W., Homma, N., Eds.; Springer: Cham, Switzerland, 2017; Volume 10529, pp. 425–442. [Google Scholar]

- Xilinx Inc. UG 470-7 Series FPGAs Configuration. Available online: https://www.xilinx.com/support/documentation/user_guides/ug470_7Series_Config.pdf. (accessed on 30 July 2019).

- Ender, M.; Moradi, A.; Paar, C. The Unpatchable Silicon: A Full Break of the Bitstream Encryption of Xilinx 7-Series FPGAs. 2020. Available online: https://www.usenix.org/system/files/sec20-ender.pdf (accessed on 12 January 2020).

- Owen, D., Jr.; Heeger, D.; Chan, C.; Che, W.; Saqib, F.; Areno, M.; Plusquellic, J. An Autonomous, Self-Authenticating, and Self-Contained Secure Boot Process for Field-Programmable Gate Arrays. Cryptography 2018, 2, 15. [Google Scholar] [CrossRef] [Green Version]

- Che, W.; Saqib, F.; Plusquellic, J. PUF-based authentication. In Proceedings of the 2015 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Austin, TX, USA, 2–6 November 2015; pp. 337–344. [Google Scholar]

- Lebedev, I.; Hogan, K.; Devadas, S. Invited paper: Secure boot and remote attestation in the sanctum processor. In Proceedings of the IEEE Computer Security Foundations Symposium, Oxford, UK, 9–12 July 2018; pp. 46–60. [Google Scholar]

- Xilinx Inc. Using Encryption and Authentication to Secure an UltraScale/UltraScale+ FPGA Bitstream Application Note (XAPP1267). 2017. Available online: https://www.xilinx.com/support/documentation/application_notes/xapp1267-encryp-efuse-program.pdf (accessed on 1 February 2018).

- Carelli, A.; Cristofanini, C.A.; Vallero, A.; Basile, C.; Prinetto, P.; di Carlo, S. Securing bitstream integrity, confidentiality and authenticity in reconfigurable mobile heterogeneous systems. In Proceedings of the 2018 IEEE International Conference on Automation, Quality and Testing, Robotics, Cluj-Napoca, Romania, 24–26 May 2018; pp. 1–6. [Google Scholar]

- Vliegen, J.; Rabbani, M.M.; Conti, M.; Mentens, N. SACHa: Self-Attestation of Configurable Hardware. In Proceedings of the Europe Conference and Exhibition, Florence, Italy, 25–29 March 2019; pp. 746–751. [Google Scholar]

- Pocklassery, G.; Che, W.; Saqib, F.; Areno, M.; Plusquellic, J. Self-authenticating secure boot for FPGAs. In Proceedings of the 2018 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), Washington, DC, USA, 30 April–4 May 2018; pp. 221–226. [Google Scholar]

- Trusted Computing Group. TCG PC Client Platform TPM Profile (PTP) Specification Family ‘2.0′ TCG Public Review. 2017. Available online: https://www.trustedcomputinggroup.org/wp-content/uploads/PCClientPlatform-TPM-Profile-for-TPM-2-0-v1-03-20-161114_public-review.pdf (accessed on 20 July 2018).

- Arthur, W.; Challener, D.; Goldman, K. A Practical Guide to TPM 2.0. 2015. Available online: https://0-link-springer-com.brum.beds.ac.uk/book/10.1007/978-1-4302-6584-9 (accessed on 7 July 2018).

- Drimer, S. Volatile FPGA Design Security—A Survey. 2008. Available online: https://pdfs.semanticscholar.org/c766/73ebed90f741f6804ee301362d9e7b366173.pdf (accessed on 30 January 2019).

- Zhang, J.; Lin, Y.; Qu, G. Reconfigurable Binding against FPGA Replay Attacks. ACM Trans. Des. Autom. Electron. Syst. 2015, 20, 1–20. [Google Scholar]

- Xilinx AXI Hardware ICAP. Available online: https://www.xilinx.com/products/intellectual-property/axi_hwicap.html (accessed on 11 May 2019).

- Chakraborty, R.S.; Saha, I.; Palchaudhuri, A.; Naik, G.K. Hardware trojan insertion by direct modification of FPGA configuration bitstream. IEEE Des. Test. 2013, 30, 45–54. [Google Scholar] [CrossRef]

- NIST. Recommended Elliptic Curves for Federal Government Use. Available online: https://github.com/isislovecruft/library--/blob/master/cryptography%20%26%20mathematics/elliptic%20curve%20cryptography/Recommended%20Elliptic%20Curves%20for%20Federal%20Government%20Use%20(1999)%20-%20NIST.pdf (accessed on 24 September 2020).

- Francillon, A.; Nguyen, Q.; Rasmussen, K.B.; Tsudik, G. A minimalist approach to Remote Attestation. In Proceedings of the Design, Automation & Test, Europe Conference & Exhibition, Dresden, Germany, 24–28 March 2014. [Google Scholar]

- WebHome-U-Boot-DENX. Available online: https://www.denx.de/wiki/U-Boot (accessed on 29 October 2019).

- AVNET ZedBoard|Zedboard. Available online: http://zedboard.org/product/zedboard (accessed on 19 January 2018).

- SLB 9670VQ2.0—Infineon Technologies. Available online: https://www.infineon.com/cms/en/product/security-smart-card-solutions/optiga-embedded-security-solutions/optiga-tpm/slb-9670vq2.0/ (accessed on 3 November 2018).

- Xilinx Inc. Programming ARM TrustZone Architecture on the Xilinx Zynq7000 All Programmable SoC User Guide (UG1019). 2014. Available online: https://www.xilinx.com/support/documentation/user_guides/ug1019-zynq-trustzone.pdf (accessed on 23 July 2019).

- Siddiqui, A.S.; Saqib, F. HEADS-UNCC/TPM_Baremetal_Drivers: TPM Baremetal for FPGAs and other Embedded Systems. Available online: https://github.com/HEADS-UNCC/TPM_baremetal_drivers (accessed on 18 June 2020).

| Algorithm | RSA 1024 | RSA 2048 | ECC NISTP256 | ECC BNP256 | AES 128 | AES 256 | SHA1 | SHA256 |

|---|---|---|---|---|---|---|---|---|

| TPM 1.2 | Yes | Yes | No | No | Optional | Optional | Yes | No |

| TPM 2.0 | Optional | Yes | Yes | Yes | Yes | Optional | Yes | Yes |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Siddiqui, A.S.; Gui, Y.; Saqib, F. Secure Boot for Reconfigurable Architectures. Cryptography 2020, 4, 26. https://0-doi-org.brum.beds.ac.uk/10.3390/cryptography4040026

Siddiqui AS, Gui Y, Saqib F. Secure Boot for Reconfigurable Architectures. Cryptography. 2020; 4(4):26. https://0-doi-org.brum.beds.ac.uk/10.3390/cryptography4040026

Chicago/Turabian StyleSiddiqui, Ali Shuja, Yutian Gui, and Fareena Saqib. 2020. "Secure Boot for Reconfigurable Architectures" Cryptography 4, no. 4: 26. https://0-doi-org.brum.beds.ac.uk/10.3390/cryptography4040026