Miniaturized Memory Devices

A special issue of Micromachines (ISSN 2072-666X). This special issue belongs to the section "A:Physics".

Deadline for manuscript submissions: closed (30 September 2022) | Viewed by 7084

Special Issue Editors

Interests: nanomaterials; thin films; memory; photovoltaics; digital manufacturing

Special Issue Information

Dear Colleagues,

Nowadays, electronic memory elements are an essential component of all electronic devices, from computers to toys and from heath monitors to space technology. Furthermore, the solid-state implementations of these devices show great potential in such applications as artificial synapses, neuromorphic computing, and reconfigurable architectures. Numerous candidates for emerging electronic memory technologies, such as ferroelectric (FeRAM), phase change random access memory (PCRAM), magnetoresistive (MRAM), resistive random access memory (ReRAM), macromolecular, and Mott memory devices, as well as organic memory, etc., have been reported. On the other side, the miniaturization concept was proposed, for first time, by Richard Feynman in his lecture “Plenty of Room at the Bottom”. His theoretical concept has materialized in the electronic devices sector with miniaturization being one of the current trends in electronics.

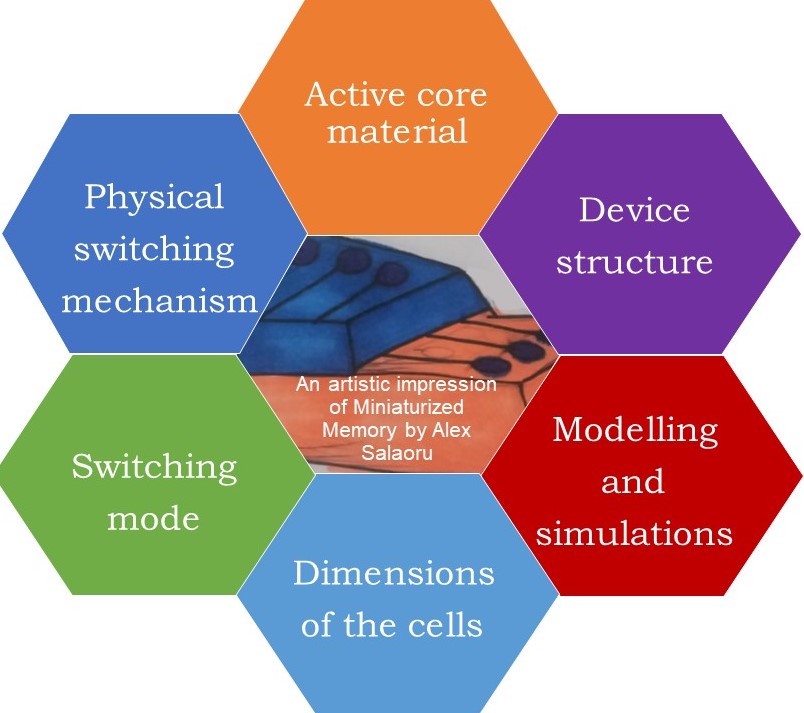

This Special Issue will encompass a few of the most important aspects that are shared by all types of memories, such as fabrication, investigation of physical switching/charging mechanism(s), mathematical modeling, and applications; these are but a few examples, and the Special Issue is therefore open to additional aspects of fields related to memory. For this Special Issue, we invite contributions from both academia and the industry.

Dr. Iulia Salaoru

Prof. Shashi Paul

Guest Editors

Manuscript Submission Information

Manuscripts should be submitted online at www.mdpi.com by registering and logging in to this website. Once you are registered, click here to go to the submission form. Manuscripts can be submitted until the deadline. All submissions that pass pre-check are peer-reviewed. Accepted papers will be published continuously in the journal (as soon as accepted) and will be listed together on the special issue website. Research articles, review articles as well as short communications are invited. For planned papers, a title and short abstract (about 100 words) can be sent to the Editorial Office for announcement on this website.

Submitted manuscripts should not have been published previously, nor be under consideration for publication elsewhere (except conference proceedings papers). All manuscripts are thoroughly refereed through a single-blind peer-review process. A guide for authors and other relevant information for submission of manuscripts is available on the Instructions for Authors page. Micromachines is an international peer-reviewed open access monthly journal published by MDPI.

Please visit the Instructions for Authors page before submitting a manuscript. The Article Processing Charge (APC) for publication in this open access journal is 2600 CHF (Swiss Francs). Submitted papers should be well formatted and use good English. Authors may use MDPI's English editing service prior to publication or during author revisions.

Keywords

- Organic/polymer memory (including macromolecular memory)

- Transition metal oxide memory

- Carbon-based memory

- Phase change memory

- Ferroelectric memory

- Magnetoresistive

- Flash memory devices (including nitride traps (SONOS))

- Mott memory